DDR2与DDR3 PCB信号完整性设计挑战

42 浏览量

更新于2024-08-28

2

收藏 475KB PDF 举报

"DDR2和DDR3的PCB信号完整性设计"

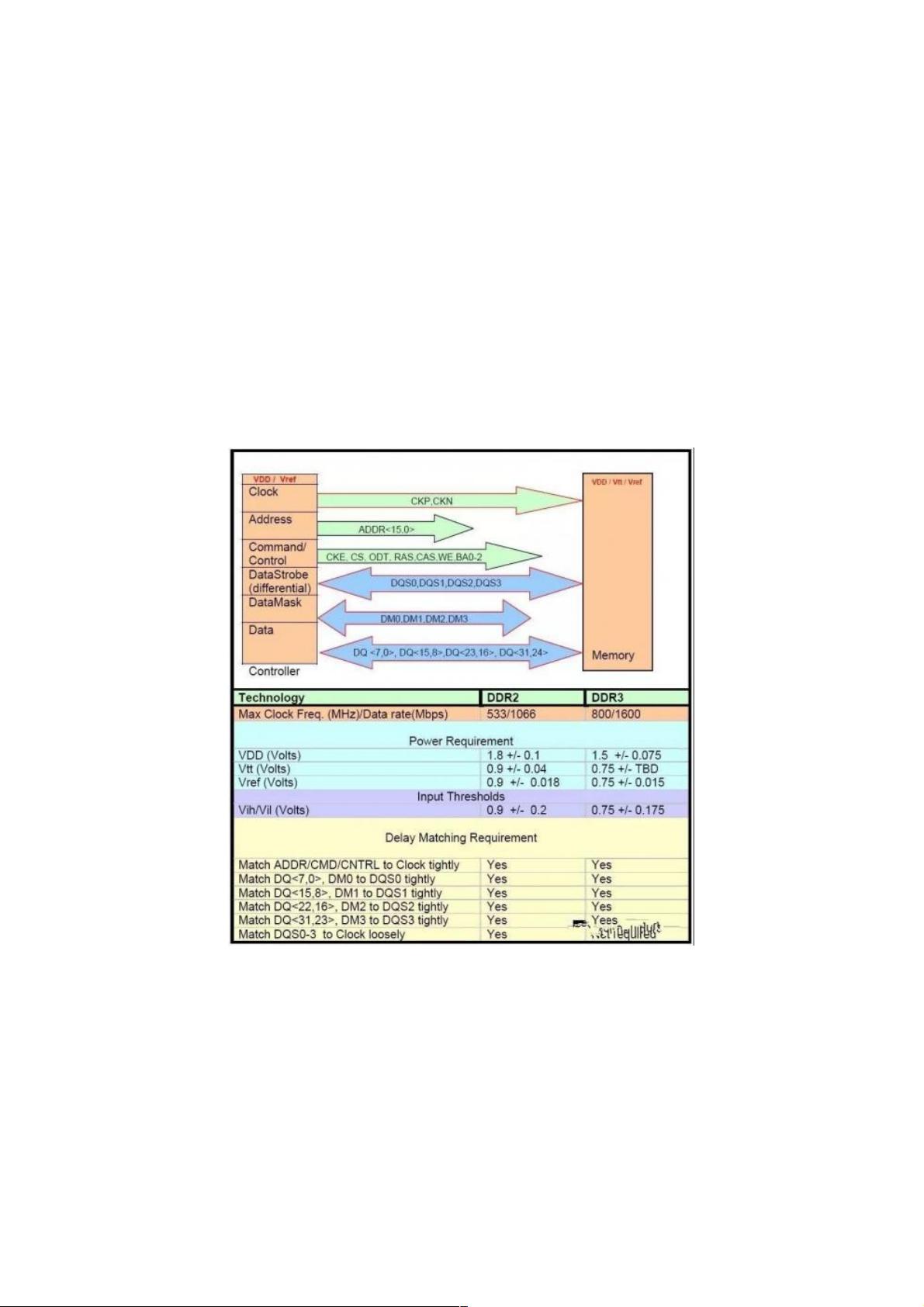

DDR2和DDR3内存模块在高速电子设备中广泛使用,其PCB设计是确保系统性能的关键环节。DDR2内存通常工作在800Mbps至1066Mbps的速度,而DDR3则可达到1600Mbps,这样的高速度对PCB的信号完整性和电源完整性提出了严格要求。

在PCB设计中,信号完整性是指确保信号在传输过程中保持其原始质量和形状的能力。这需要考虑多个因素,包括时序匹配,即确保所有信号在同一时刻到达接收端,以避免错误的数据解析。时序匹配的重要性在高速DDR内存设计中尤为突出,因为数据传输速率高,微小的延迟差异都可能导致数据错误。

电源完整性则是指电源网络在负载变化下能提供稳定电压的能力。对于DDR内存,稳定的电源供应是保证信号质量的基础,因为它直接影响到内存芯片的工作状态和信号的噪声水平。

在4层PCB设计中,挑战主要在于如何在有限的层数内实现有效的信号和电源隔离。通常,顶层和底层用于信号传输,中间两层作为接地(GND)和电源(VDD)平面。这种布局有助于减少信号间的干扰,并提高电源效率。然而,这样的设计可能会导致信号线的布线难度增加,因为所有信号必须在两个面上分布,增加了信号之间的串扰风险。

阻抗控制是另一个关键点。为了保证信号的质量,每条信号线都需要有一个特定的特征阻抗。不正确的阻抗匹配会导致信号反射,进一步影响信号完整性。设计时,通常会使用阻抗计算器和仿真软件(如Cadence ALLEGRO SI-230或Ansoft's HFSS)来确定合适的线宽和间距,以达到所需的阻抗值。

此外,DDR2和DDR3还有各自特定的技术要求,如DDR3的更低电压运行(1.5V相对于DDR2的1.8V)和更高的数据传输速率,这都需要在PCB设计中特别考虑。例如,降低电压意味着需要更精确的电源管理,以确保足够的信号幅度。

在6层或更多层的PCB设计中,可以有更多的空间进行电源平面和地平面的配置,从而提高电源完整性和信号的屏蔽效果,进一步优化性能。但即使在这种情况下,设计师仍需谨慎处理信号的拓扑结构,以减少串扰并保证时序匹配。

DDR2和DDR3的PCB设计是一个涉及多方面复杂问题的领域,包括信号完整性的计算、电源完整性的规划以及在有限层数下的最佳布局。成功的PCB设计不仅依赖于理论知识,还需要实际经验和高级工具的支持,以确保在高速操作下系统的可靠性和稳定性。

265 浏览量

139 浏览量

2021-10-11 上传

105 浏览量

128 浏览量

128 浏览量

265 浏览量

点击了解资源详情

136 浏览量

weixin_38699593

- 粉丝: 6

最新资源

- Silverlight1.1快速入门:函数查询与实战示例

- 数据结构复习题库:400+精选算法与数据结构题目

- 探索C++模板深度:罕见技巧与特殊设计详解

- Python游戏编程入门指南

- S3C2410芯片上4线电阻式触摸屏的应用与优化

- Java开发工具大盘点:从JDK到Eclipse,14款常用工具解析

- 深入探索Microsoft Reporting Services

- Java实现的各种Hash算法总结

- 探索MSP430:超低功耗16位单片机原理与应用详解

- Linux设备驱动程序:内核与硬件的桥梁

- Windows Vista内核安全深度评估:新防护与潜在漏洞

- Effective STL:深入解析STL的实践指南

- RTX内核实战:基于RealView MDK的实时操作系统演示

- 提升软件测试效率:50个具体实践方法

- SetupFactory 7.0:安装包制作简易教程

- GoF23种设计模式解析:C++实现与实战指南