DDR2与DDR3 PCB设计:信号完整性和电源完整性挑战

122 浏览量

更新于2024-08-28

收藏 822KB PDF 举报

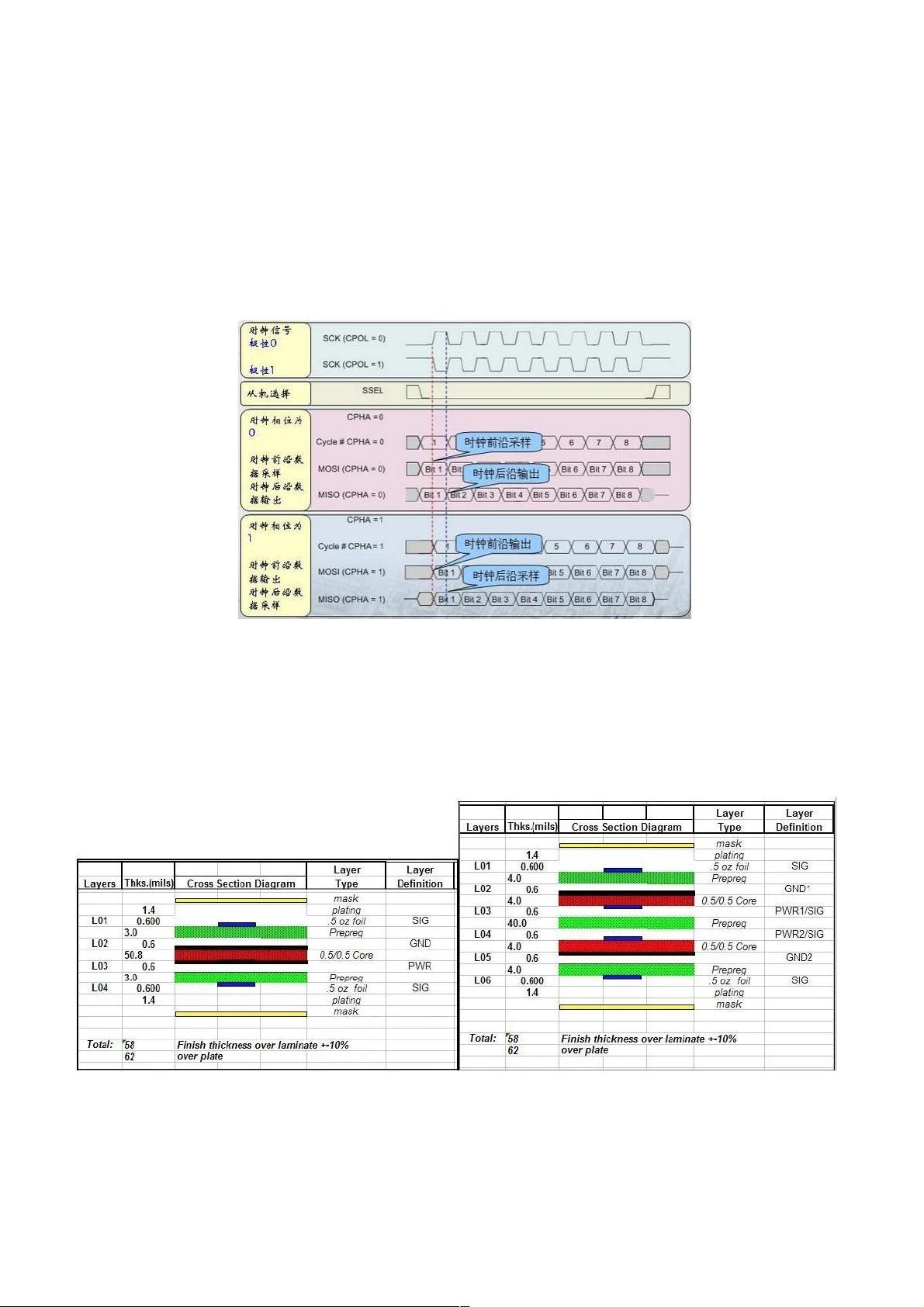

"本文主要探讨了DDR2和DDR3在PCB设计中的信号完整性和电源完整性问题,特别是在四层板设计中的挑战。文章强调了在高速传输环境下,如DDR2的800Mbps和DDR3的1600Mbps速率下,确保时序匹配和波形完整性的重要性。设计考虑因素包括PCB叠层、阻抗控制、互联拓扑、时延匹配、串扰管理、电源完整性和时序分析。作者指出,虽然有如Cadence ALLEGRO SI-230和Ansoft's HFSS等EDA工具可以帮助进行计算和仿真,但在四层板设计中,信号线通常限于顶层和底层,电源和地平面的布局策略至关重要。此外,阻抗的连续性对于DDR2的单端和差分信号线都必不可少,以确保信号质量。"

在DDR2和DDR3的PCB设计中,信号完整性(SI)和电源完整性(PI)是两个核心概念。信号完整性涉及到信号在传输过程中不受干扰,保持其原有效载波信息,确保数据传输的准确性和可靠性。而电源完整性则关注电源网络的稳定性和噪声,因为电源质量直接影响到芯片的工作性能和信号质量。

首先,PCB叠层设计是关键。在四层板设计中,通常将一层作为接地平面,另一层作为电源平面,这种布局有助于减少信号间的干扰并提高电源效率。对于六层板,可以进一步优化电源和地平面的配置,提升电源完整性,同时提供更灵活的信号路由。

阻抗控制是另一个重要的设计要素。在DDR2和DDR3的高速信号中,信号线的阻抗应保持恒定,以避免信号反射和衰减。单端信号通常需要50欧姆的阻抗匹配,而差分信号线则需保证阻抗匹配,以降低信号之间的串扰。

互联拓扑设计涉及如何有效地布置信号线,以减少延迟和串扰。DDR2和DDR3的高速信号要求精确的时序匹配,这意味着所有信号到达接收端的时间差必须在一个可接受的范围内,以确保正确解码。

串扰是高速信号传输中的常见问题,它发生在相邻信号线间因电磁耦合产生的干扰。良好的PCB设计应能通过适当的线间距、屏蔽和信号排列来减少串扰的影响。

电源完整性是高速系统设计中不可忽视的部分。DDR2和DDR3的Vtt和Vref电压需要在电源平面层上提供,以确保稳定的工作电压。电源网络的去耦和滤波也是确保低噪声电源的关键。

DDR2和DDR3的PCB设计涉及多个复杂因素的相互作用。设计师需要熟练运用各种EDA工具,结合理论知识和实践经验,以实现高效、可靠的高速信号传输。

134 浏览量

710 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

108 浏览量

点击了解资源详情

点击了解资源详情

124 浏览量

weixin_38688097

- 粉丝: 5

- 资源: 928

最新资源

- 有关GSM原理一些详细描述

- MyEclipse中文攻略

- tech ourself shell programming

- 常用算法设计方法常用算法设计方法

- 王宏文《自动化专业英语教程》PART1中文翻译

- 中文TEX教程 inotes.pdf

- 时代光华《成功的项目管理》讲义

- Bruce Eckel - Thinking In Patterns Problem-Solving Techniques Using Java

- 电视系统常用名词解释

- modelsim 使用教程

- MyEclipse 6 Java 开发中文教程

- java模式(精华篇)

- JSP基础(英文版)

- ★java及j2ee面试题集(很重要).

- JSP网页编程 JSp课件

- Linux常用命令大全整理