1 Introduction to Hardware Obfuscation: Motivation … 7

1.2.1 Integrated Circuit Supply Chain

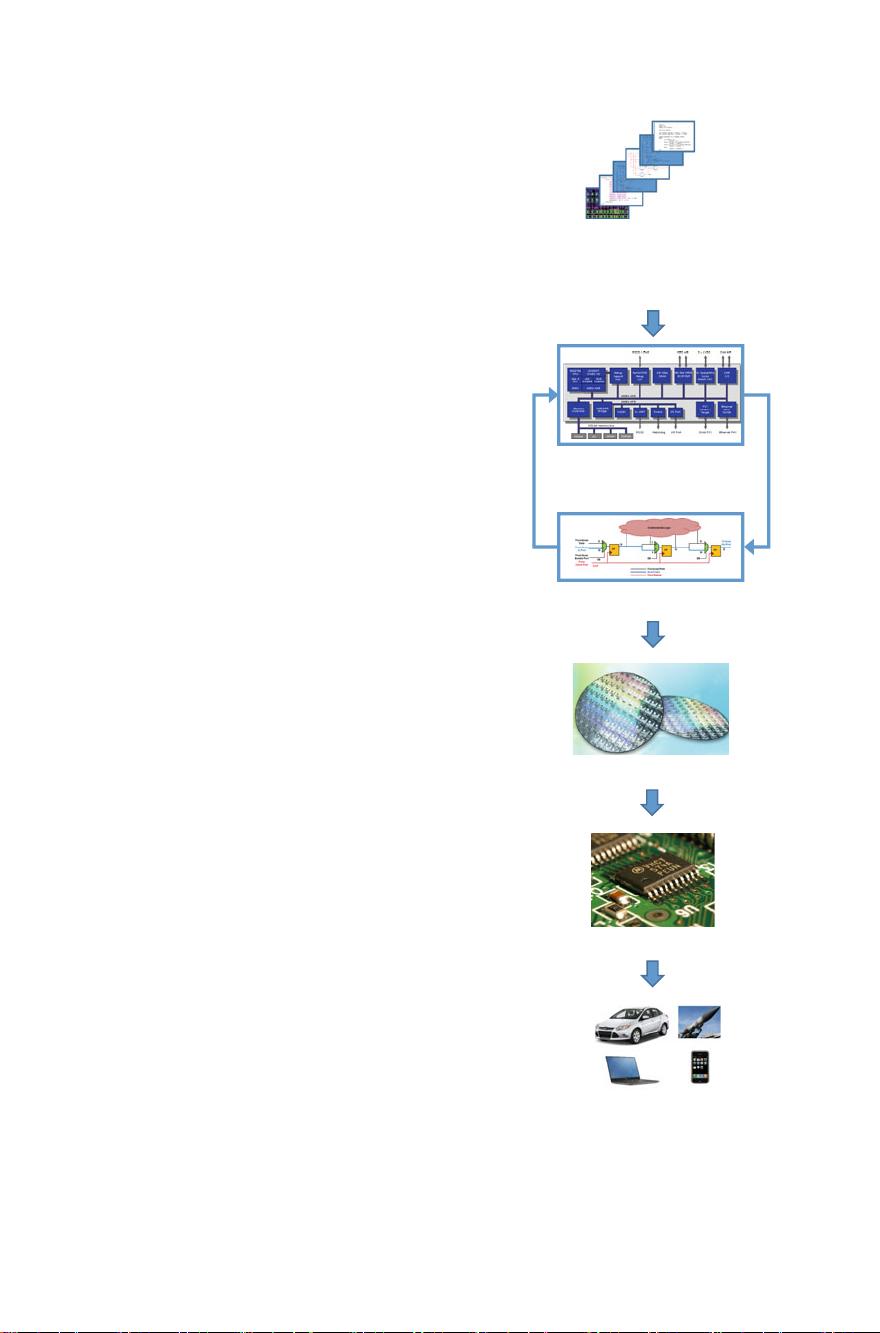

Figure 1.2 shows the various steps involved in today’s semiconductor supply chain.

Each step is carried out in different parts of the globe by different entities (not

necessarily under the same company) in order to reduce the insurmountable costs

associated with producing state-of-the-art ICs and to reduce time-to-market.

• IP Vendor: Integrated circuits today are most commonly in the form of system-on-

chips or SoCs. This means that a single silicon die contains intellectual property

from several different vendors who could be scattered all across the globe. For

example, the power management circuitry may come from an analog IP vendor

in Texas, while the cryptographic IP core might come from a separate vendor in

Europe. With increasing complexity of today’s ICs and short turnaround times, it

only makes sense for a design house (or SoC integrator) to buy IPs from several

different vendors (usually at a much better rate) than to build the entire IC in-house

from scratch. These IPs can generally be classified as (i) soft IP (RTL level, e.g.,

in the form of Verilog or VHDL), (ii) firm IP (gate-level IPs), and (iii) hard IPs

(layout-level IPs, also known as hard macros, e.g., embedded SRAM).

• Design House/SoC Integrator: After collecting the necessary IP blocks, the

design house puts these IPs in a single design and performs exhaustive simu-

lations/verification to ensure that the overall design functions as intended. During

this stage, electronic design automation (EDA) tools, which are commonly pur-

chased from external EDA vendors, are heavily employed in order to perform

synthesis, place and route (P&R), timing analysis, and verification. Note that most

design houses today have gone ‘fabless’ meaning that they do not maintain their

own silicon production facility (i.e., foundry).

• Design-for-Test: Design-for-Test (DFT) is a stage in the IC design process where

infrastructures are integrated on-chip for post-manufacturing tests. A few decades

ago, it was feasible to comprehensively test bare circuits after manufacturing so that

defects generated during fabrication (e.g., short-circuit, damaged gates) could be

detected quickly. However, with the sheer scale of ICs today, it is no longer possible

to engage in exhaustive logic testing post-fabrication. As a result, the design house

can choose to send its entire design (usually in gate-level form) to a separate DFT

facility that specializes in inserting test infrastructures into the circuit. This can

include specialized flip-flops (FFs) called scan FFs, which can allow a tester to

observe and control internal parts of the design (which, otherwise, might not be

accessible through the primary inputs of the circuit). Other advanced test structures

for self-diagnosis such as built-in-self-test or BIST and test compression can also

be incorporated at this stage to ensure good fault coverage of the circuit-under-test.

• Foundry: After performing comprehensive tests and design, the SoC integrator

generates a final layout file (usually in the form of a GDSII file) and sends it to

a semiconductor foundry. The foundry first generates a mask from the file and

then etches the patterns from t he mask onto an actual silicon wafer to produce

the IC die (after dicing the wafer). The foundry may also test the individual die

at this point, using manufacturing test patterns that are provided by the design

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功