CADENCE Allegro 高速PCB仿真设计实战指南

"EDA高速设计与PCB仿真主要讲解了基于CADENCE Allegro工具的板级仿真设计,涵盖了高速设计的定义、PCB仿真的重要性以及详细的设计流程。本书内容包括仿真设置、拓扑提取与建立、时序仿真、设置约束及赋予PCB以及后仿真过程与参数设置。"

在高速电子设计领域,正确理解高速信号和高速设计至关重要。高速信号是指频率超过1GHz的信号,这类信号会受到边缘速率的影响,导致传输线效应显著,如信号反射、串扰和衰减等。为解决这些问题,高速PCB仿真是必不可少的步骤。

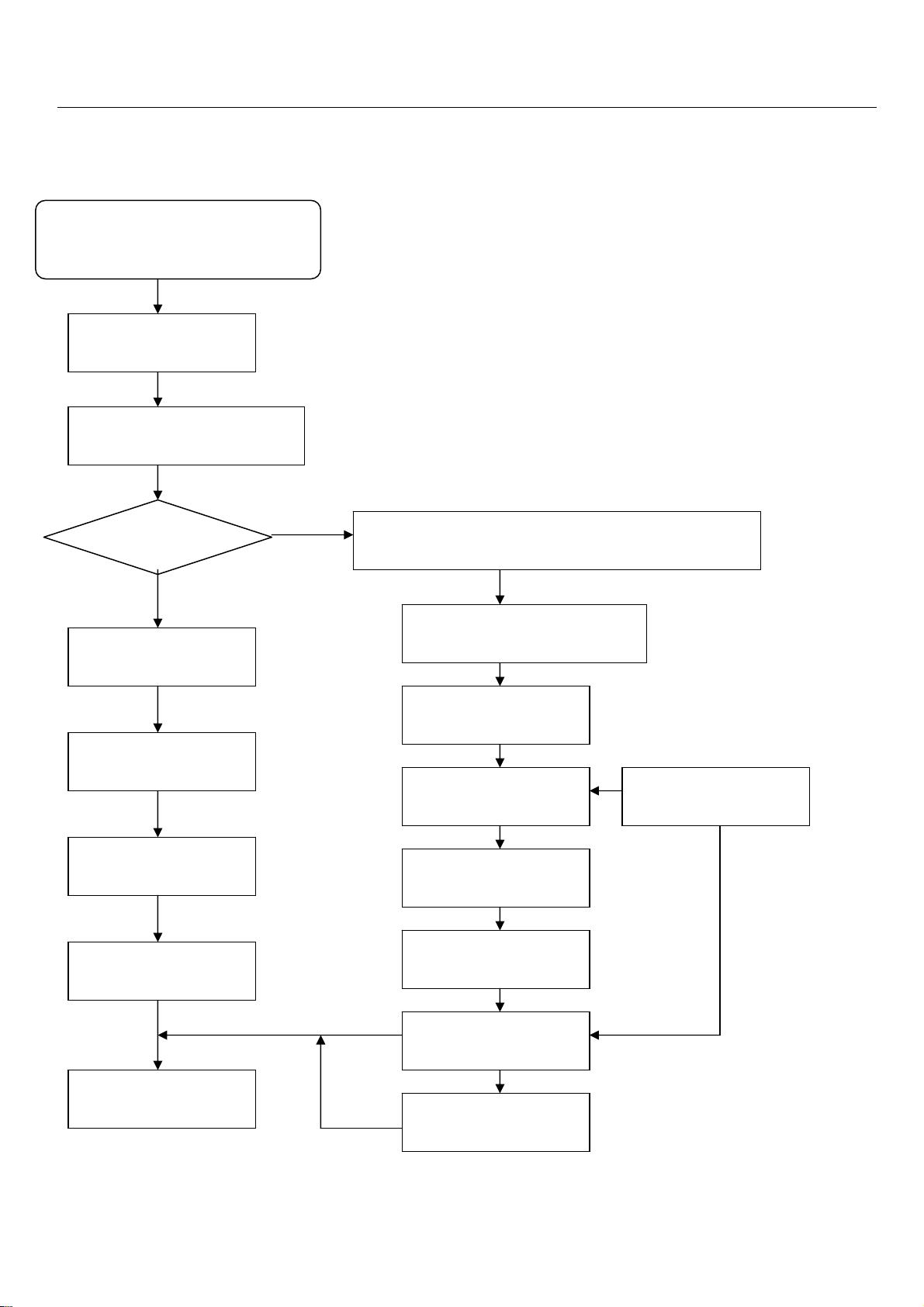

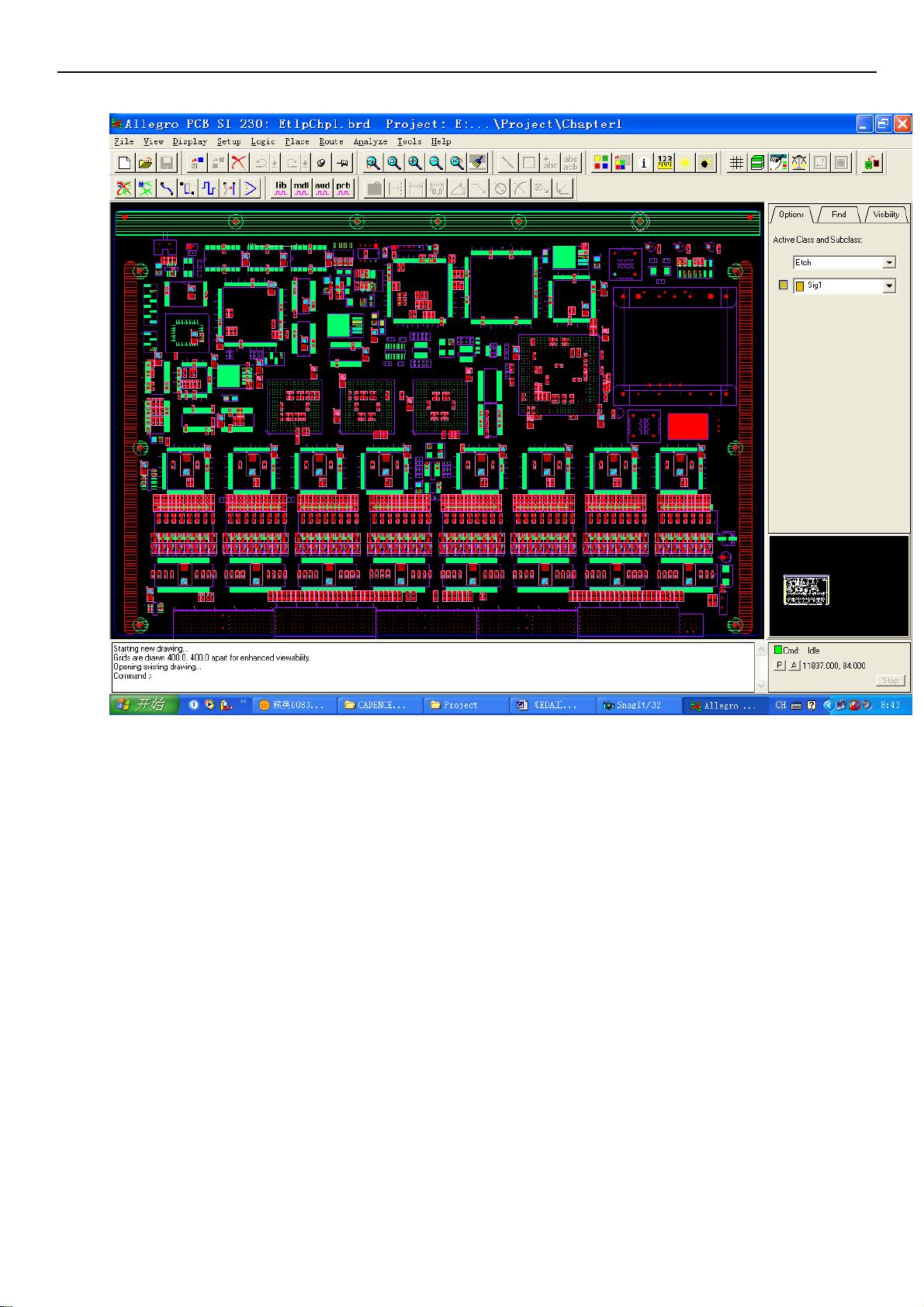

PCB仿真不仅包括板级SI(信号完整性)仿真,以确保信号在PCB上传输时的完整性,还涉及系统级SI仿真,以评估整个系统层面的信号质量。在设计流程中,通常先确定PCB仿真的一般流程,然后利用CADENCE Allegro这样的专业工具进行具体操作,包括设置仿真环境、提取网络拓扑、分配模型、设定测试条件等。

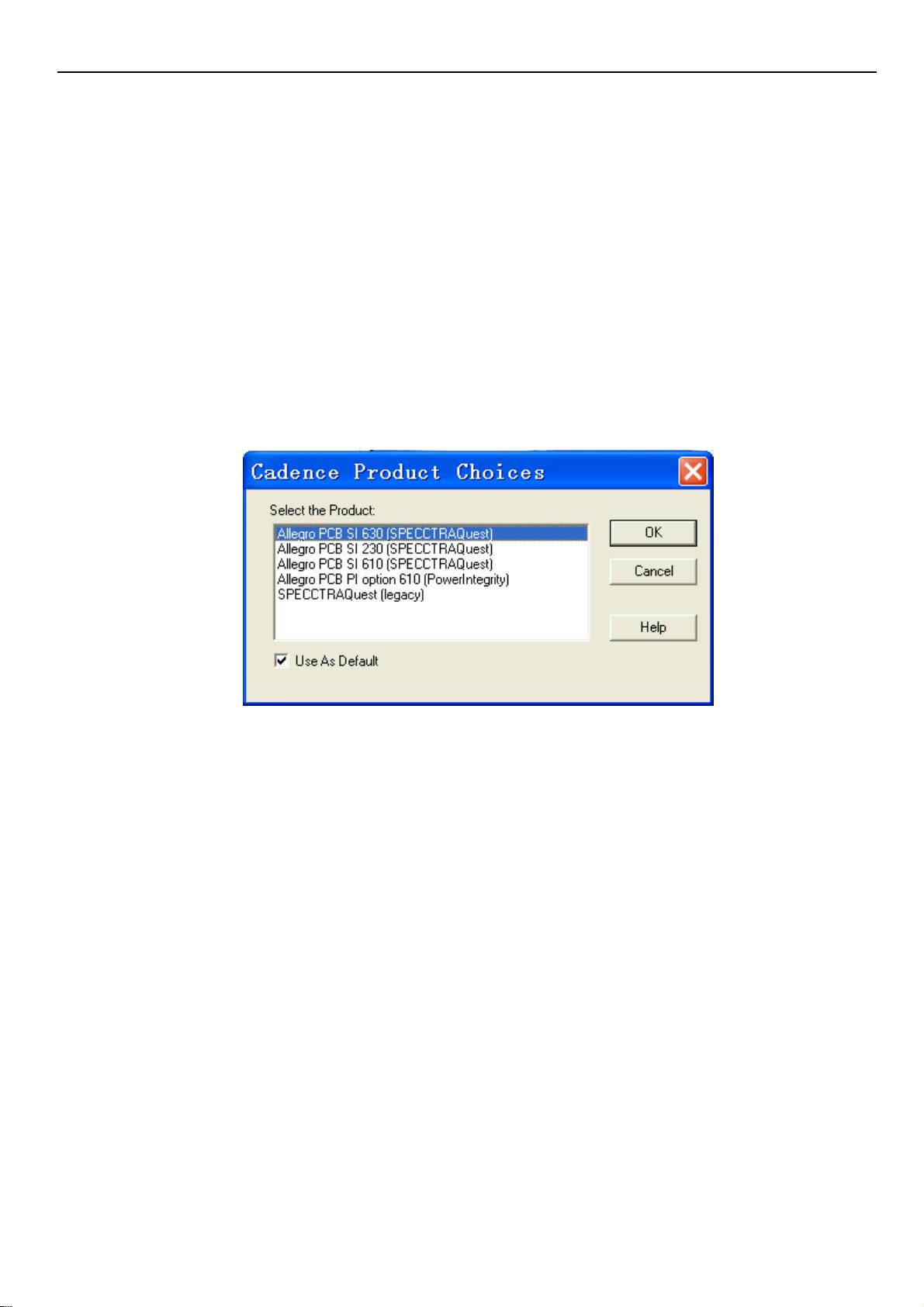

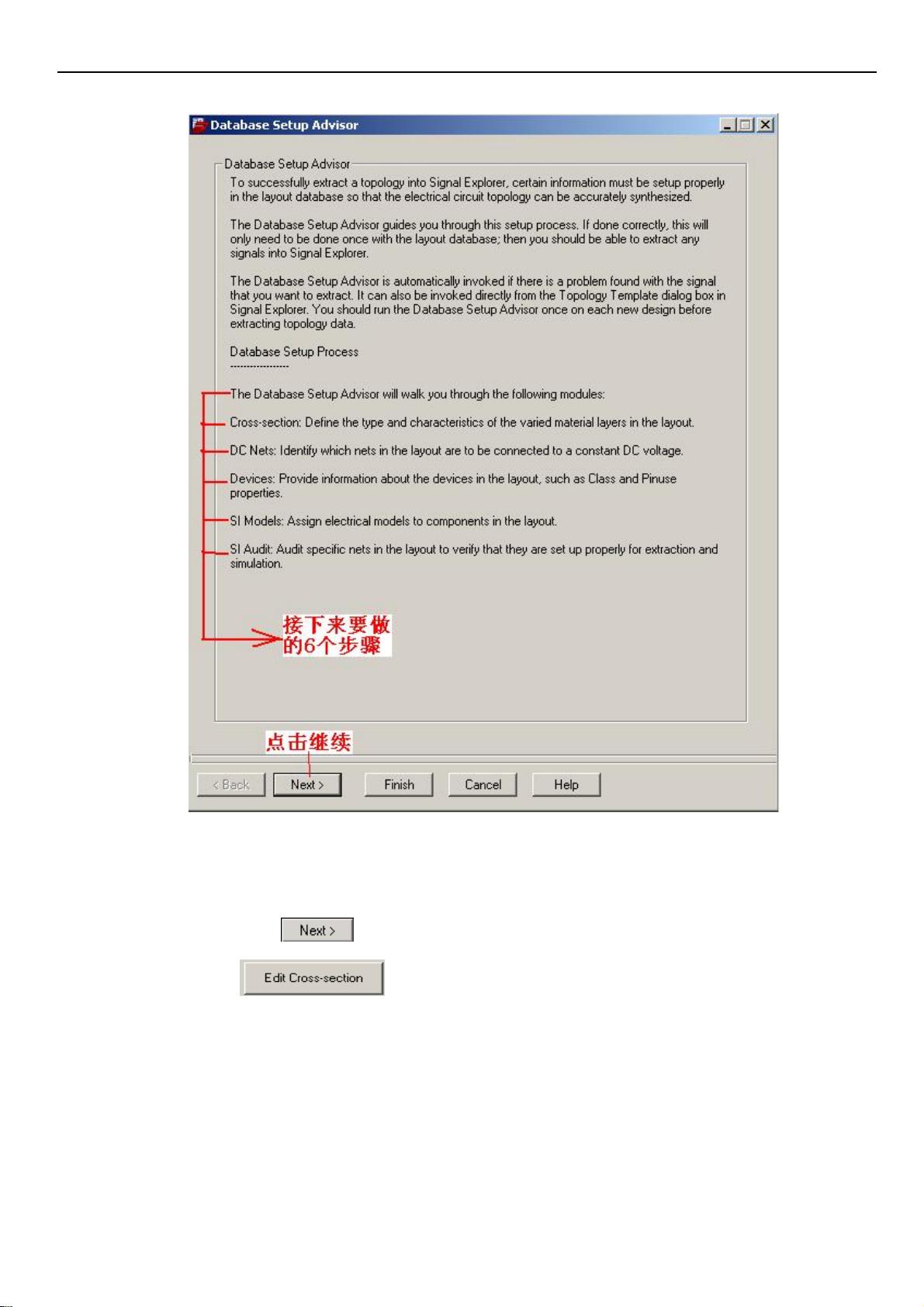

在设置阶段,设计者需要打开BRD文件,并调用设置向导,进行一系列参数配置,如叠层参数、线宽、DC网络电平、器件模型、IO管脚测试条件和逻辑门限值等。对于差分驱动器,还需要特别关注其设置以优化信号对的性能。

在提取和建立拓扑进行仿真时,可以使用SignalAnalysis或ConstraintManager自动提取,也可以手工建立和调整,以确保模拟真实电路情况。SIGXPLORER和SIGWAVE工具则用于设定仿真参数和执行仿真过程。

时序仿真部分,包括传统的共同时钟同步系统和源同步接口的仿真,分析时序参数,确保时钟信号的准确传输。时钟同步系统的仿真过程包括时序计算和仿真执行,而源同步接口仿真则需考虑源同步时序公式,以保证数据传输的同步性。

设置约束是确保设计符合规范的关键步骤,设计者需要启动约束条件设置界面,逐个添加约束,并理解各个约束标签栏的作用。最后,将这些约束应用到PCB文件上,以确保设计符合预设的标准。

后仿真过程包括参数设置和准备工作,这一阶段的精细调整有助于验证设计是否满足所有要求,为最终的硬件实现提供可靠保证。

"EDA高速设计与PCB仿真"深入探讨了高速PCB设计中的关键环节,提供了一套完整的基于CADENCE Allegro的仿真设计方法,对于提升PCB设计质量和效率具有重要指导价值。

179 浏览量

104 浏览量

2020-10-20 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

夏雨夜寐

- 粉丝: 50

- 资源: 7

最新资源

- GPS-Library-for-proteus_it_GPS_

- FOSDET-开源

- 基于C语言实现不同频率闪烁多个LED灯(含源代码+使用说明).zip

- watch-child-nodes:观察DOM节点的子级列表,为每个新元素和每个已删除元素调用一个函数

- OWASP-security-scanner:自动化的安全扫描程序,用于使用python selenium-python自动化模块和漂亮的soup web scrapper模块在python 3.9.1中进行的sql注入和跨站点脚本编写

- pandas-ods-reader-0.1.4.tar.gz

- uber-driver-game:一款叙事性新闻游戏,探索优步司机的经济和生活

- Mj_Farsi_font_

- blazor-file-upload-image-preview:在使用Syncfusion Blazor File Upload组件上传图像之前显示图像预览

- Klientutv-inl2:Simpel网上商店

- flutter_cache_manager:颤振的通用缓存管理器

- telPHP-开源

- 易语言源码密码验证找回源码.rar

- pandas-montecarlo-0.0.2.tar.gz

- HmcREG7_REG9_CALC_HMC锁定窗口计算方法_

- nagyprism(x1,x2,y1,y2,h,rho):用于计算 Nagy 棱镜地形校正的函数文件-matlab开发