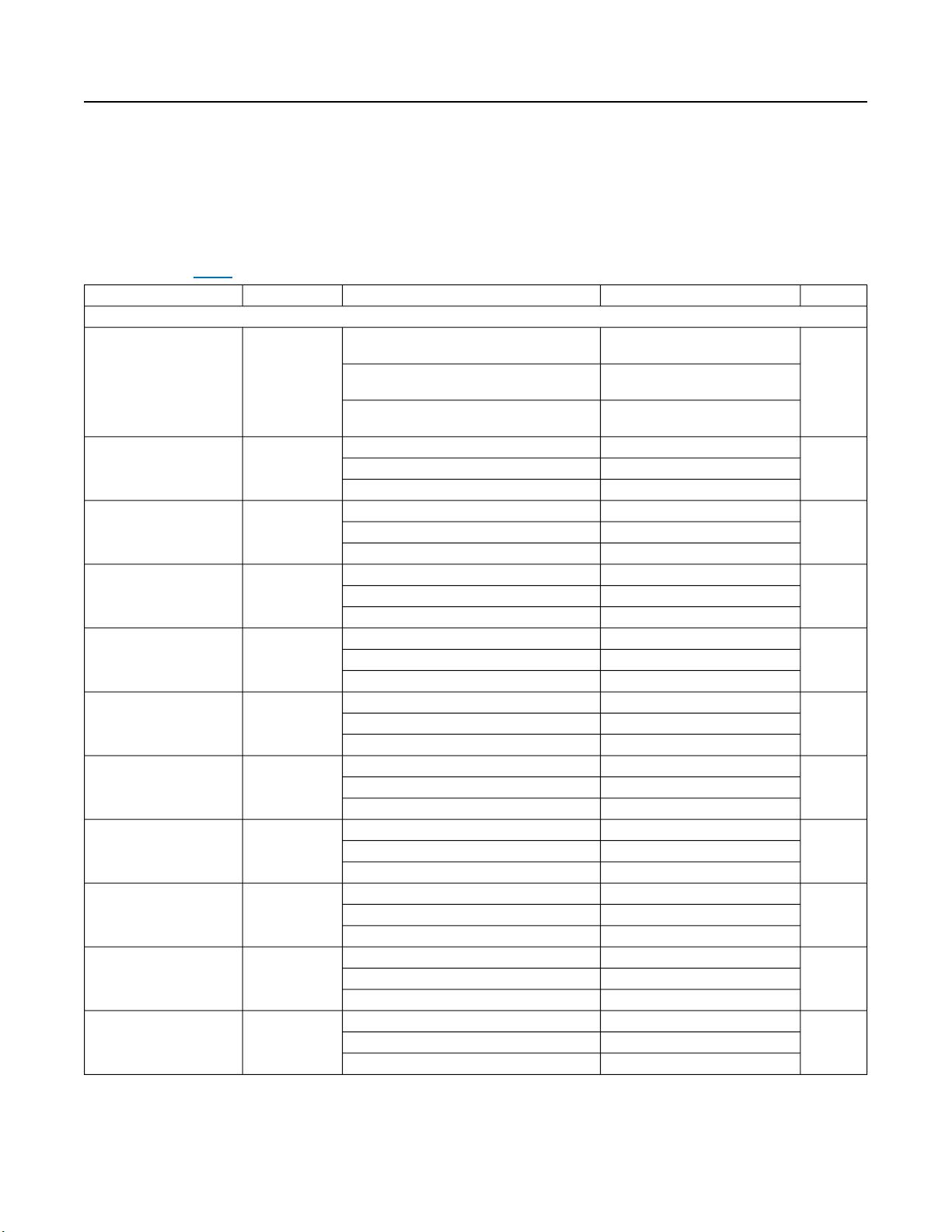

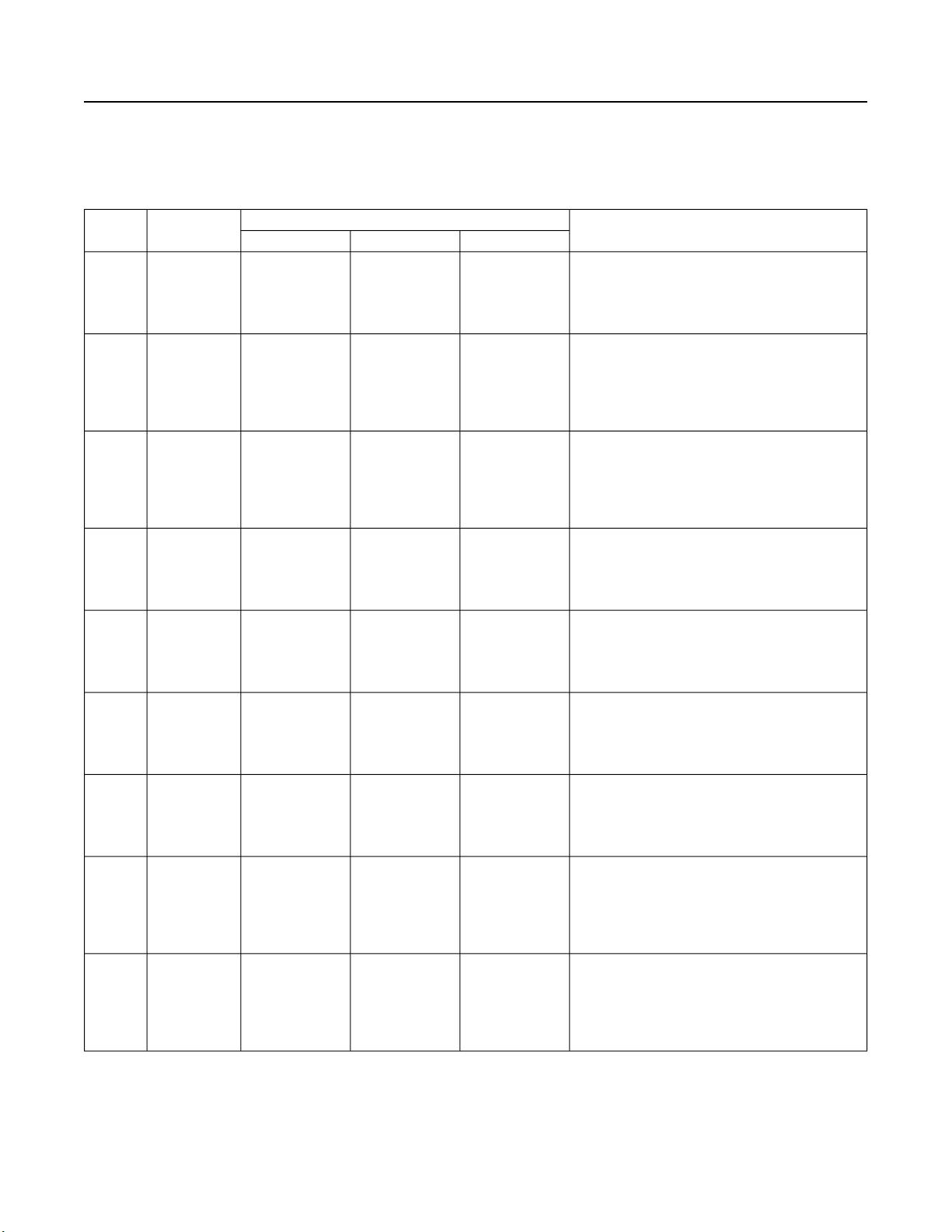

PIN NAME

FUNCTION MODE

FUNCTION

GMSL2 GMSL1 MAX96724R

33 CKCP

DISABLED*

CKCP

CKAP(alt)

A0C

C0C

DISABLED*

CKCP

CKAP(alt)

A0C

C0C

DISABLED*

CKCP

CKAP(alt)

A0C

C0C

DISABLED: CKCP is Disabled in 4-Lane Mode

CKCP: D-PHY Port C Clock Lane (2-lane)

CKAP(alt): D-PHY Port A CLK ALT (4-lane)

A0C: C-PHY Port A Lane 0 Output C (4-lane)

C0C: C-PHY Port C Lane 0 Output C (2-lane)

34 CKCN

DISABLED*

CKCN

CKAN(alt)

A1A

C1A

DISABLED*

CKCN

CKAN(alt)

A1A

C1A

DISABLED*

CKCN

CKAN(alt)

A1A

C1A

DISABLED: CKCN is Disabled in 4-Lane Mode

CKCN: D-PHY Port C Clock Lane (2-lane)

CKAN(alt): D-PHY Port A CLK ALT (4-lane)

A1A: C-PHY Port A Lane 1 Output A (4-lane)

C1A: C-PHY Port C Lane 1 Output A (2-lane)

35 DA1P

DA1P*

DC1P

A1B

C1B

DA1P*

DC1P

A1B

C1B

DA1P*

DC1P

A1B

C1B

DA1P: D-PHY Port A Data Lane 1 (4-lane)

DC1P: D-PHY Port C Data Lane 1 (2-lane)

A1B: C-PHY Port A Lane 1 Output B (4-lane)

C1B: C-PHY Port C Lane 1 Output B (2-lane)

36 DA1N

DA1N*

DC1N

A1C

C1C

DA1N*

DC1N

A1C

C1C

DA1N*

DC1N

A1C

C1C

DA1N: D-PHY Port A Data Lane 1 (4-lane)

DC1N: D-PHY Port C Data Lane 1 (2-lane)

A1C: C-PHY Port A Lane 1 Output C (4-lane)

C1C: C-PHY Port C Lane 1 Output C (2-lane)

37 DA2P

DA2P*

DD0P

A2A

D0A

DA2P*

DD0P

A2A

D0A

DA2P*

DD0P

A2A

D0A

DA2P: D-PHY Port A Data Lane 2 (4-lane)

DD0P: D-PHY Port D Data Lane 0 (2-lane)

A2A: C-PHY Port A Lane 2 Output A (4-lane)

D0A: C-PHY Port D Lane 0 Output A (2-lane)

38 DA2N

DA2N*

DD0N

A2B

D0B

DA2N*

DD0N

A2B

D0B

DA2N*

DD0N

A2B

D0B

DA2N: D-PHY Port A Data Lane 2 (4-lane)

DD0N: D-PHY Port D Data Lane 0 (2-lane)

A2B: C-PHY Port A Lane 2 Output B (4-lane)

D0B: C-PHY Port D Lane 0 Output B (2-lane)

39 CKAP

CKAP*

CKDP

DISABLED

A2C

D0C

CKAP*

CKDP

DISABLED

A2C

D0C

CKAP*

CKDP

DISABLED

A2C

D0C

CKAP: D-PHY Port A Clock Lane (4-lane)

CKDP: D-PHY Port D Clock Lane (2-lane)

DISABLED: When CKAP/N(alt) is Enabled

A2C: C-PHY Port A Lane 2 Output C (4-lane)

D0C: C-PHY Port D Lane 0 Output C (2-lane)

40 CKAN

CKAN*

CKDN

DISABLED

A3A

D1A

CKAN*

CKDN

DISABLED

A3A

D1A

CKAN*

CKDN

DISABLED

A3A

D1A

CKAN: D-PHY Port A Clock Lane (4-lane)

CKDN: D-PHY Port D Clock Lane (2-lane)

DISABLED: When CKAP/N(alt) is Enabled

A3A: C-PHY Port A Lane 3 Output A (4-lane)

D1A: C-PHY Port D Lane 1 Output A (2-lane)

41 DA3P

DA3P*

DD1P

A3B

D1B

DA3P*

DD1P

A3B

D1B

DA3P*

DD1P

A3B

D1B

DA3P: D-PHY Port A Data Lane 3 (4-lane)

DD1P: D-PHY Port D Data Lane 1 (2-lane)

A3B: C-PHY Port A Lane 3 Output B (4-lane)

D1B: C-PHY Port D Lane 1 Output B (2-lane)

42 DA3N

DA3N*

DD1N

A3C

D1C

DA3N*

DD1N

A3C

D1C

DA3N*

DD1N

A3C

D1C

DA3N: D-PHY Port A Data Lane 3 (4-lane)

DD1N: D-PHY Port D Data Lane 1 (2-lane)

A3C: C-PHY Port A Lane 3 Output C (4-lane)

D1C: C-PHY Port D Lane 1 Output C (2-lane)

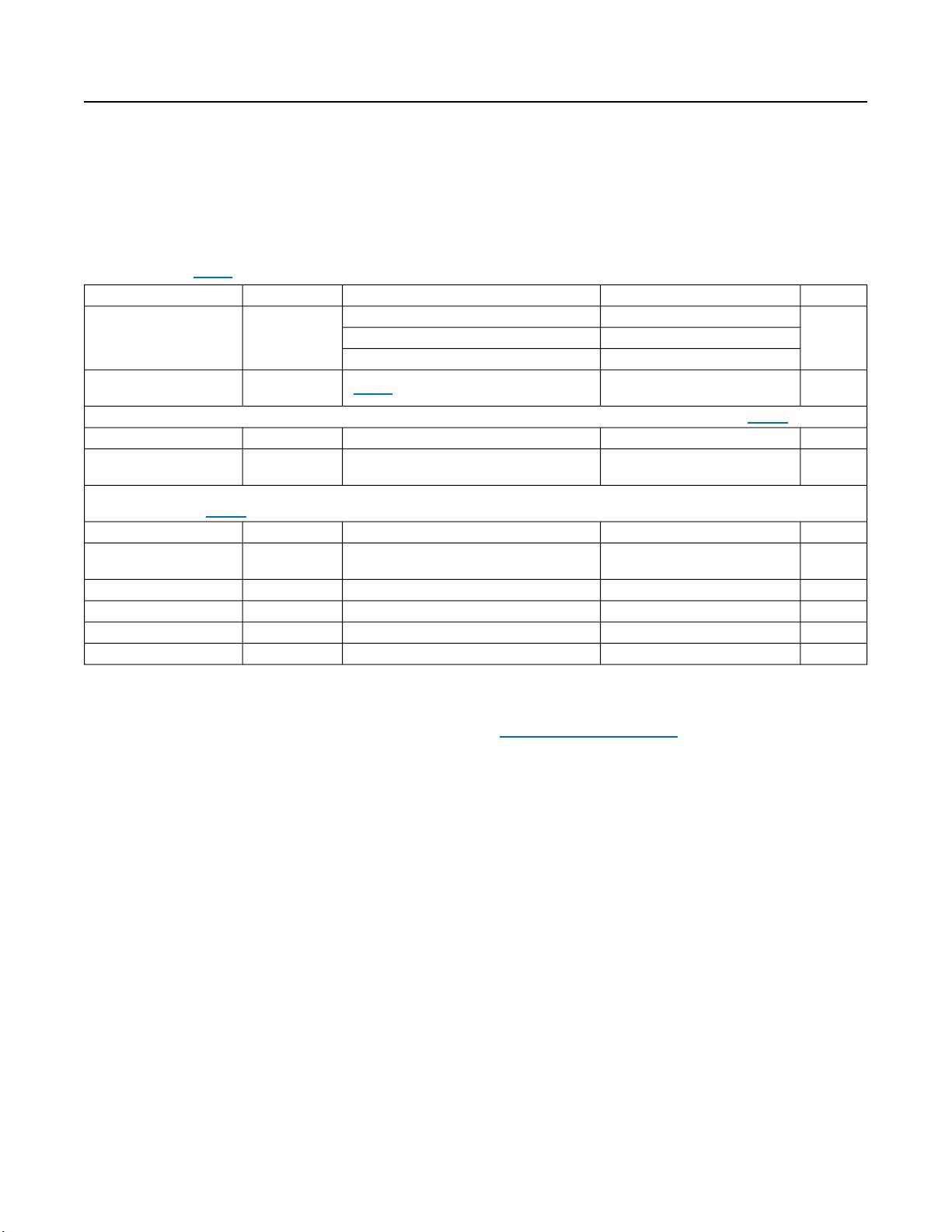

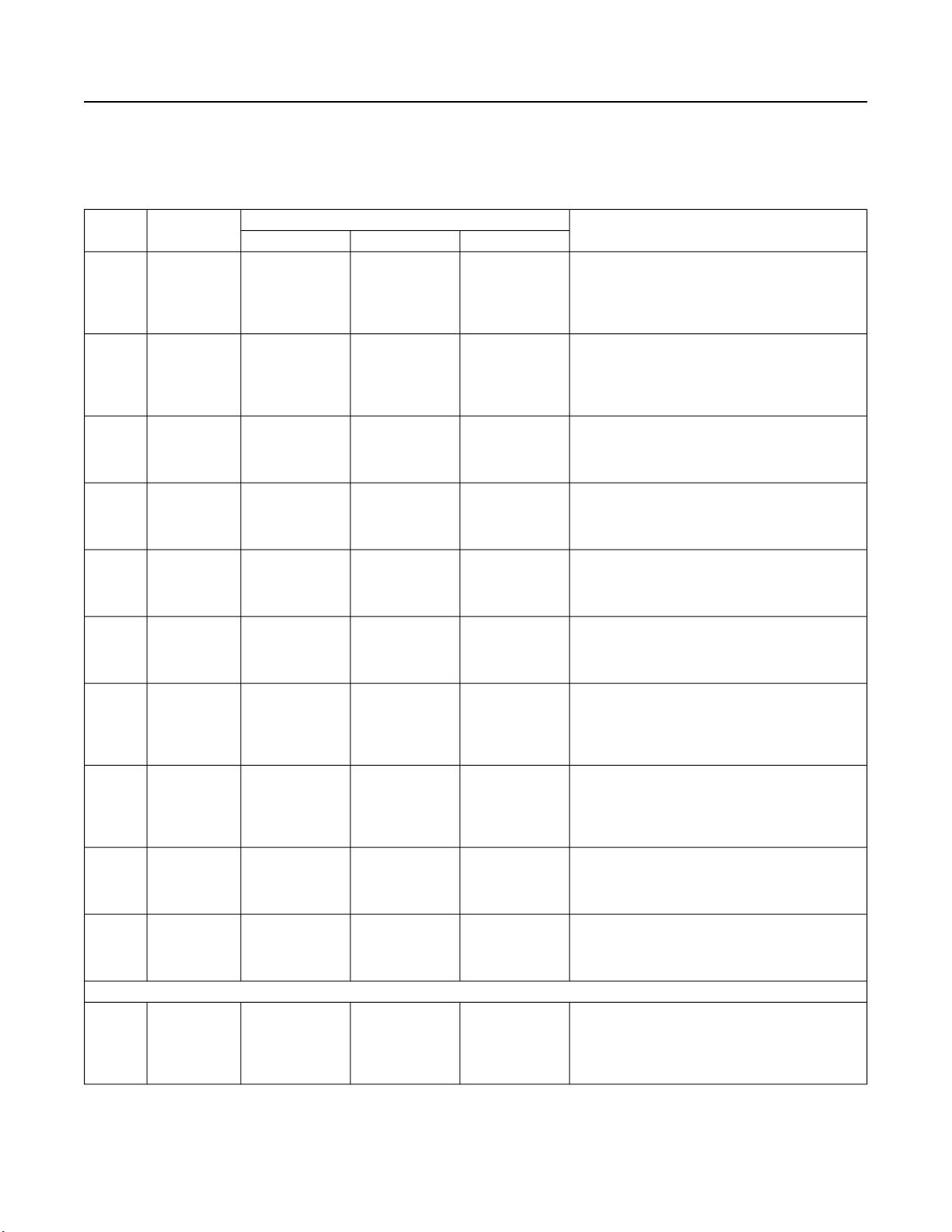

CSI-2 INTERFACE — PORT B/E/F (* denotes default state after power-up)

43 DB0P

DB0P*

DE0P

B0A

E0A

DB0P*

DE0P

B0A

E0A

N.C.

DB0P: D-PHY Port B Data Lane 0 (4-lane)

DE0P: D-PHY Port E Data Lane 0 (2-lane)

B0A: C-PHY Port B Lane 0 Output A (4-lane)

E0A: C-PHY Port E Lane 0 Output A (2-lane)

N.C.: No Connect

MAX96724/F/R Quad Tunneling GMSL2/1 to CSI-2 Deserializer

www.analog.com Analog Devices | 19