【Cadence HDL ASIC实现攻略】:HDL到ASIC设计转换的高效技巧!

发布时间: 2025-01-09 20:20:50 阅读量: 4 订阅数: 8

HDL语言与ASIC原理:修改后的状态机.pdf

# 摘要

本文全面概述了使用Cadence工具链实现HDL ASIC的设计与优化过程。首先,介绍了HDL设计基础及其转换为ASIC的理论基础,随后详细探讨了代码质量控制的各个方面。在实践操作部分,文章深入讲解了设计输入、验证、逻辑合成与优化、以及物理设计与布局布线的实践技巧。接着,重点阐述了ASIC实现中的关键技术,如时序约束与分析、低功耗设计技术、以及测试与故障诊断方法。最后,通过多个高级优化案例,分析了如何在HDL到ASIC转换过程中提升性能、减少面积占用,并实现低功耗设计。本文旨在为读者提供一整套ASIC设计与优化的实用知识,增强ASIC设计的效率与可靠性。

# 关键字

Cadence HDL ASIC实现;设计基础与转换;质量控制;逻辑合成优化;物理设计布局;时序约束分析;低功耗技术;测试故障诊断;性能面积优化案例;低功耗设计案例

参考资源链接:[Cadence Design Entry HDL中文教程:全面指南](https://wenku.csdn.net/doc/4r4i2p4oa6?spm=1055.2635.3001.10343)

# 1. Cadence HDL ASIC实现概述

随着集成电路技术的飞速发展,ASIC(应用特定集成电路)设计已成为芯片设计领域的一个关键环节。在这一章中,我们将探索Cadence提供的HDL(硬件描述语言) ASIC实现的技术路线图。首先,我们将概述ASIC实现的流程,包括从HDL编码到最终芯片生产的关键步骤。然后,我们将简要介绍Cadence在HDL ASIC实现中所扮演的重要角色,包括它提供的先进设计工具和设计方法。

接下来,我们深入探讨ASIC实现过程中的技术挑战,如时序优化、功耗管理以及信号完整性。此外,我们还会关注Cadence解决方案在这些领域内提供的优势,例如通过高级功耗优化技术降低功耗,以及利用精确的时序分析工具保证系统时序性能。

最后,我们将以Cadence工具链如何在现代HDL ASIC设计项目中实现高效率和高质量为结尾,为读者提供一个清晰的、可操作的ASIC设计和实现的最佳实践。随着本章节的结束,读者将对ASIC设计有一个宏观的认识,并为进一步学习更深入的技术细节打下坚实的基础。

# 2. HDL设计基础与转换理论

## 2.1 HDL设计的基本概念

### 2.1.1 HDL语言的起源与特性

硬件描述语言(HDL)是用于电子系统设计自动化的一种编程语言,它能够描述数字电路的结构和行为。HDL的起源可以追溯到20世纪60年代,随着集成电路的出现和复杂性增加,需要一种新的方式来模拟、测试和验证这些电路。到了20世纪80年代,随着计算机辅助设计(CAD)工具的发展,HDL开始成为主流。

HDL具有以下特性:

- **文本形式描述**:HDL代码是用标准文本形式编写的,易于版本控制和存储。

- **可模拟与验证**:HDL允许工程师在实际制造集成电路前,通过软件模拟验证电路设计的功能与性能。

- **可综合性**:HDL代码可被专门的综合工具转换成实际的电子电路,这是实现ASIC和FPGA等硬件的关键步骤。

### 2.1.2 设计抽象层次与规范说明

在HDL设计中,抽象层次的概念是至关重要的。设计通常分为以下三个层次:

- **行为级(Behavioral Level)**:描述了电路的功能行为,但不涉及具体实现。在这一层,开发者使用算法或者过程来表达设计意图,如状态机、算术操作等。

- **寄存器传输级(Register Transfer Level, RTL)**:在RTL层,设计者描述了数据在寄存器之间的流动以及相应的操作。这是目前主流集成电路设计所使用的层次。

- **门级(Gate Level)**:这一层次提供了对电路更详细的描述,包括具体的逻辑门以及它们之间的连接。

规范说明是指对设计需求的明确描述。这是设计过程的起点,为后续的设计、仿真、测试以及验证工作提供依据。规范可以是自然语言描述、形式化语言描述、或者使用HDL编写的高级功能描述。

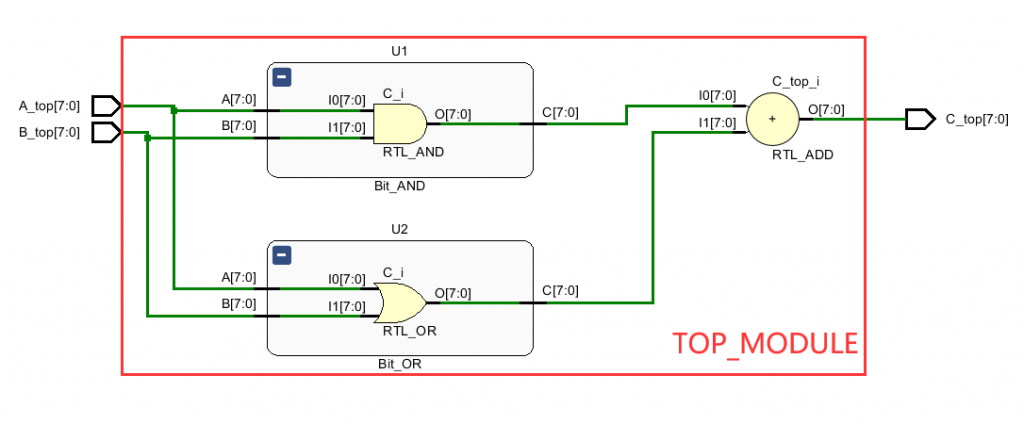

## 2.2 从HDL到ASIC的转换原理

### 2.2.1 合成过程的理论基础

HDL到ASIC的转换过程包括多个步骤,首先是设计的合成过程。合成工具将HDL代码转换为门级或更底层的网表(netlist),这个过程基于特定的硬件描述语言综合标准,如IEEE 1364标准的Verilog或IEEE 1076标准的VHDL。

合成过程依赖于目标技术库(Technology Library),这个库定义了所有可以在目标工艺上实现的标准单元(Standard Cells),如逻辑门、触发器等。综合过程分为以下三个主要阶段:

- **逻辑综合**:将HDL代码翻译成逻辑门的集合。

- **映射**:将逻辑门映射到目标技术库中的实际硬件元件。

- **优化**:对映射后的设计进行优化,以提高性能或减少资源占用。

### 2.2.2 设计转换的约束条件和优化目标

设计转换过程中的约束条件包括时间、面积、功耗和可靠性等方面。开发者必须在这些约束条件中寻找平衡,以达到预期的设计目标。例如,在移动设备中,功耗可能是一个重要的优化目标,而在高性能服务器中,吞吐量和计算速度可能是优先考虑的。

优化目标通常包含:

- **面积优化**:减小芯片的尺寸,以降低制造成本和功耗。

- **时序优化**:确保信号可以在所需的时钟周期内传输,满足时序要求。

- **功耗优化**:减少能耗,延长电池寿命,减少冷却成本。

## 2.3 HDL代码的质量控制

### 2.3.1 代码风格与可读性改进

为了提高HDL代码的质量,代码风格的规范和可读性改进是关键。良好的代码风格不仅使代码易于阅读,也有助于代码维护和后续的综合过程。例如:

- 使用有意义的变量名和模块名。

- 维护一致的缩进和注释风格。

- 将复杂的功能分解为小型、可复用的模块。

下面是一个简单的VHDL代码示例,展示了规范的命名和格式化:

```vhdl

-- VHDL Example: Simple Counter Module

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity counter is

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

count : out STD_LOGIC_VECTOR(7 downto 0));

end counter;

architecture Behavioral of counter is

signal temp_count : STD_LOGIC_VECTOR(7 downto 0) := (others => '0');

begin

process(clk, reset)

begin

if reset = '1' then

temp_count <= (others => '0');

elsif rising_edge(clk) then

temp_count <= temp_count + 1;

end if;

end process;

count <= temp_count;

end Behavioral;

```

### 2.3.2 代码性能与面积优化技巧

优化HDL代码来提升性能和减少面积,是HDL设计中非常重要的环节。性能优化主要关注的是速度和时序,而面积优化则主要关注资源使用和芯片尺寸。一些常用的优化技巧包括:

- **流水线技术(Pipelining)**:通过在数据路径中引入寄存器来提高时钟频率。

- **资源共享(Resource Sharing)**:通过合并具有相似操作的硬件资源来减少所需的硬件数量。

- **状态机优化**:精简状态机的复杂度,合并不必要的状态。

例如,针对下面的Verilog代码段:

```verilog

always @(posedge clk) begin

q <= d; // Simple register assignment

end

```

可以优化为带使能信号的寄存器:

```

```

0

0