Nexys 4 DDR进阶秘籍:玩转七段显示器的技巧

发布时间: 2024-12-18 11:03:20 阅读量: 6 订阅数: 6

# 摘要

本文介绍了Nexys 4 DDR开发板与七段显示器的基础知识及其在数字钟项目中的应用。章节一概述了Nexys 4 DDR开发板和七段显示器的基本概念。第二章深入探讨了七段显示器的数字编码及控制方法,包括其工作原理、结构介绍、数字与段位映射关系,以及利用Verilog实现控制的技巧。第三章讲述了高级显示技巧与优化,包括动态扫描显示和使用PWM技术调整亮度与对比度。第四章专注于综合应用项目——数字钟的设计与实现,涵盖了需求分析、时钟模块实现和系统集成测试。最后一章讨论了Nexys 4 DDR的进阶开发技巧,如高级外设接口技术、FPGA开发环境优化和项目开发经验分享。整体而言,本文为工程技术人员提供了一系列从基础到进阶的开发指导和优化策略,旨在提升七段显示器在数字显示项目中的使用效率和质量。

# 关键字

Nexys 4 DDR;七段显示器;数字编码;Verilog;动态扫描;PWM;数字钟;FPGA开发环境;系统集成测试

参考资源链接:[Nexys4-DDR开发板详解:Artix-7 FPGA的实践平台](https://wenku.csdn.net/doc/6469abfc5928463033e103cc?spm=1055.2635.3001.10343)

# 1. Nexys 4 DDR和七段显示器基础

## 简介

在数字逻辑设计的学习路径上,Nexys 4 DDR开发板结合七段显示器提供了一个既基础又实用的起点。Nexys 4 DDR是一个面向学术和工业领域的FPGA开发板,配备有Xilinx Artix-7 FPGA、各种输入输出接口、以及一系列的外设,包括七段显示器。七段显示器则是早期电子显示器的一个代表,尽管它已被现代LCD和LED显示器所取代,但在教学和一些特定的应用场景中,它的简单直接和低成本仍使其有不可替代的价值。

## Nexys 4 DDR开发板

Nexys 4 DDR开发板以其高性价比、丰富的用户I/O接口和强大的计算能力,成为学习FPGA技术的一个优良平台。本章节将介绍开发板的基本组件,包括核心处理器、内存、I/O端口,以及如何通过USB接口与计算机连接进行编程。

## 七段显示器基础

### 工作原理概述

七段显示器由7个LED组成,排列成“8”字形状,通过分别点亮不同的LED来显示0到9的数字。每个LED称为一段,因此得名“七段显示器”。每个段位分别对应到数字的一种编码,通过控制这些LED的开关状态,可以展示数字、字母,甚至简单的符号。

### 应用场景

在实际应用中,七段显示器可用于显示计数、时间、温度等数据。例如,在一个简单的数字钟项目中,七段显示器能够清晰地显示当前的时、分、秒信息。接下来的章节将深入探讨如何编程控制七段显示器,实现各种显示效果。

# 2. 七段显示器的数字编码与控制

### 2.1 七段显示器的工作原理

#### 2.1.1 七段显示器的结构介绍

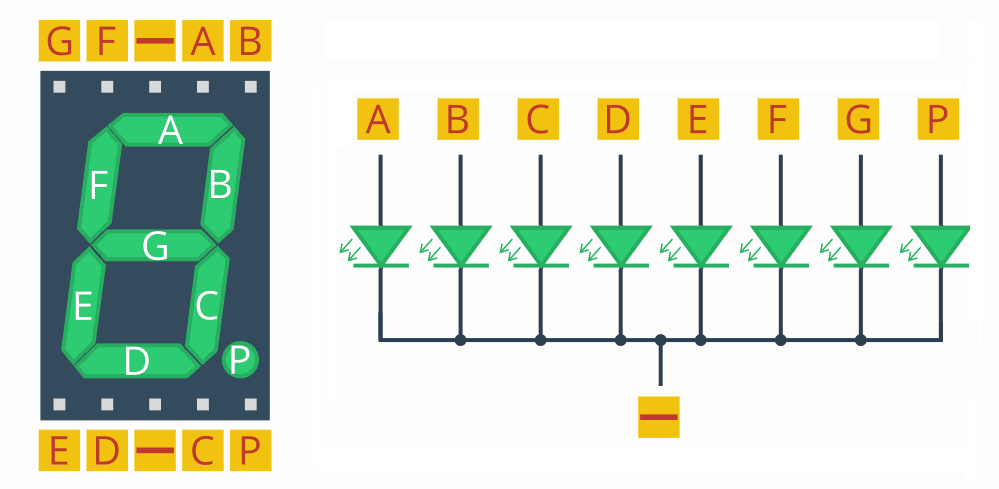

七段显示器是一种常用的电子显示设备,其工作原理基于将数码管的七个独立段(A-G)点亮或熄灭来显示数字0-9。每个段对应显示数字的一个部分,通过适当的组合可以展示所有阿拉伯数字。

- **数码管的七个段**:通常,七段显示器由七个发光二极管(LEDs)组成,它们被安排成“8”字型,分别标记为A、B、C、D、E、F和G。

- **共阴极与共阳极**:七段显示器分为共阴极和共阳极两种类型。在共阴极七段显示器中,所有LED的阴极都连接在一起,并接地。阳极分别接到各个段的驱动线路。当驱动线路为高电平时,相应的段点亮。在共阳极七段显示器中,所有LED的阳极连接在一起并接正电源,阴极分别接驱动线路,阴极接地时段点亮。

#### 2.1.2 数字与段位的映射关系

为了显示数字,需要确定每个段位在显示特定数字时的状态(点亮或熄灭)。下表展示了0到9每个数字对应的段位状态,其中1代表点亮,0代表熄灭:

| 数字 | A | B | C | D | E | F | G |

|-------|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

通过上表可以看出,不同的数字点亮的段位是不同的,而了解这种映射关系对于编程控制七段显示器至关重要。

### 2.2 编程控制七段显示器

#### 2.2.1 利用Verilog实现基本显示

要使用Verilog编程语言控制七段显示器,我们首先需要定义一个模块来驱动每个段位。以下是一个简单的Verilog代码示例,用于显示数字0到9:

```verilog

module seven_segment_display(

input [3:0] binary_input, // 4-bit binary input

output reg [6:0] seg // 7-bit output to control the segments

);

// Combinational block to set the output seg based on binary_input

always @(*) begin

case (binary_input)

4'b0000: seg = 7'b1000000; // Display 0

4'b0001: seg = 7'b1111001; // Display 1

4'b0010: seg = 7'b0100100; // Display 2

4'b0011: seg = 7'b0110000; // Display 3

// ... continue for 4-9

4'b1001: seg = 7'b0110000; // Display 9

default: seg = 7'b1111111; // Turn all off for undefined cases

endcase

end

endmodule

```

在这个例子中,`binary_input`是一个4位的输入,代表了要显示的数字的二进制编码。输出`seg`是一个7位的向量,每一位对应七段显示器的一个LED段(A到G)。`always @(*)`块是一个组合逻辑块,它根据输入的值来决定输出的LED段的状态。

#### 2.2.2 点亮多个七段显示器

在实际应用中,我们可能需要显示多位数字,这时就需要连接多个七段显示器。要实现这一功能,我们可以在Verilog中添加额外的逻辑来控制多个显示器。

```verilog

// ... [省略其它代码]

// Modified always block to handle multiple seven-segment displays

always @(*) begin

case (binary_input[3:2]) // Select which display to control based on the upper bits of the input

2'b00: begin

seg = 7'b1000000; // Display 0 on the first display

// Other controls for the remaining displays

end

2'b01: begin

seg = 7'b0110000; // Display 9 on the first display

// Other controls for the remaining displays

end

// ... continue for other cases

endcase

end

// ... [省略其它代码]

```

在上述代码中,通过改变`binary_input`的高位来选择要控制的七段显示器,并设置其段位状态。这样就可以控制多个显示器以显示多位数字了。

#### 2.2.3 利用有限状态机优化显示效果

为了优化显示效果,我们可以引入有限状态机(FSM)。FSM可以控制七段显示器显示数字时的动态变化,比如创建滚动显示或者创建动态更新效果。

```verilog

// ... [省略其它代码]

// FSM example to control a dynamic update of the display

module seven_segment_FSM(

// Inputs and outputs

);

reg [2:0] state = 0; // State variable

// FSM logic

always @(posedge clk) begin

case (state)

3'b000: begin

// Display logic for state 0

state = state + 1;

end

3'b001: begin

// Display logic for state 1

state = state + 1;

end

// ... continue for other states

default: begin

// Reset state or handle default case

state = 0;

end

endcase

end

// ... [省略其它代码]

```

在这个FSM的实现中,`state`变量用于追踪当前的状态,而`always @(posedge clk)`块确保在每个时钟上升沿改变状态。根据当前的状态,我们可以在每个显示器上显示不同的数字,并创建出连续变化的显示效果。

通过这样的方法,可以实现复杂的显示逻辑,并且优化了显示效果。在有限状态机的帮助下,可以实现例如数字钟等需要定时更新显示的应用。

以上章节内容通过对七段显示器的工作原理、编程控制方法以及优化显示技术的介绍,为读者提供了深入理解七段显示器控制的基础知识和实践技能。在后续章节中,我们将继续探讨更高级的显示技巧与优化方法,以及如何将这些技术应用于实际项目中,例如设计一个数字钟。

# 3. 高级显示技巧与优化

### 3.1 实现动态扫描显示

动态扫描显示是一种在多显示器场合下,通过快速切换显示内容到各个显示器上,从而在视觉上形成持续显示效果的技术。这种技术不仅能够节省IO端口的使用,还能扩展显示单元的数量,特别适合于需要显示多位数字信息的应用,如数字钟、频率计等。

#### 3.1.1 动态扫描的原理

动态扫描的基本原理是利用人眼的视觉暂留特性,通过在短时间内快速轮流点亮不同的七段显示器,从而使得每个显示器都能够在一段时间内保持显示状态。由于扫描切换速度足够快,用户的肉眼无法分辨出切换过程,只能看到持续显示的效果。

这种技术的关键在于扫描频率的控制。如果扫描频率过低,会导致显示器闪烁,影响显示效果;如果扫描频率过高,则可能增加FPGA的处理负担,影响系统性能。

#### 3.1.2 动态扫描显示的Verilog实现

在Verilog中实现动态扫描显示需要设计一个计数器,用于确定扫描频率,以及一个状态机,用于控制不同的七段显示器轮流点亮。

```verilog

module dynamic_scan(

input clk, // 时钟信号

output reg [7:0] seg, // 七段显示器的段位信号

output reg [3:0] an // 七段显示器的位选信号

);

// 参数定义

parameter COUNTER_MAX = 10000000; // 定义扫描频率,具体值根据实际需求调整

reg [23:0] scan_counter = 0; // 扫描计数器

// 动态扫描逻辑

always @(posedge clk) begin

if (scan_counter == COUNTER_MAX - 1) begin

scan_counter <= 0; // 计数器清零

an <= an + 1; // 位选信号递增,用于选择下一个显示器

if (an == 4'b1111) begin

an <= 0; // 循环至初始位置

end

end else begin

scan_counter <= scan_counter + 1; // 计数器累加

end

end

// 每个显示器的显示内容

always @(*) begin

case(an)

4'b0000: seg = display0; // 第一个显示器的显示内容

4'b0001: seg = display1; // 第二个显示器的显示内容

// 更多显示器的显示内容

default: seg = 8'hFF; // 默认熄灭

endcase

end

endmodule

```

在上述代码中,`scan_counter`用于控制扫描频率,当其值达到预设的最大值时,通过改变`an`信号来选择下一个要点亮的七段显示器。`seg`信号根据`an`的选择输出对应的显示内容。这样的设计使得多个七段显示器能够轮流显示不同的数字,从而实现动态扫描显示效果。

### 3.2 提升显示的亮度和对比度

在设计七段显示器显示系统时,亮度和对比度对于显示效果至关重要。亮度决定了显示内容的可见性,对比度则影响了显示内容与背景的区分度。

#### 3.2.1 理解亮度和对比度的电子特性

亮度通常由七段显示器的背光或本身LED的电流大小决定,亮度越高,显示内容越清晰,但过高的亮度可能缩短显示器的使用寿命,并增加功耗。

对比度则是由显示器的亮暗区域的差异决定的。一个高对比度的显示设备能够在明亮的环境下依然保持内容清晰可见。

#### 3.2.2 使用PWM技术调整亮度

脉冲宽度调制(PWM)是一种常用的技术,用于调节设备的功率输出,从而控制其亮度。在七段显示器的应用中,可以通过调整PWM信号的占空比来改变通过LED的电流,进而控制亮度。

```verilog

module pwm_brightness(

input clk, // 时钟信号

input [3:0] duty_cycle, // PWM占空比

output pwm_out // PWM输出信号

);

reg [7:0] pwm_counter = 0; // PWM计数器

always @(posedge clk) begin

pwm_counter <= pwm_counter + 1; // 计数器累加

end

// 生成PWM波形

assign pwm_out = (pwm_counter < duty_cycle) ? 1'b1 : 1'b0;

endmodule

```

在上述代码中,通过调整`duty_cycle`的值,可以控制PWM输出信号的占空比。例如,占空比为50%时,意味着在每个PWM周期内,信号有一半的时间是高电平,另一半时间是低电平。如果`duty_cycle`增大,则占空比增加,通过LED的电流增多,亮度提高;反之则亮度降低。

这种方法可以有效地控制显示亮度,并且可以通过软件动态调整,实现亮度的自动或手动调节功能。

```mermaid

graph TD;

A[开始] --> B[设置duty_cycle];

B --> C{PWM计数器};

C -->|< duty_cycle| D[输出PWM高电平];

C -->|>= duty_cycle| E[输出PWM低电平];

D --> F[调节通过LED的电流];

E --> F;

F --> G[改变亮度];

G --> H[结束];

```

上述流程图展示了PWM调节亮度的步骤,从设置占空比到输出PWM信号,最终改变七段显示器的亮度。

通过这种方式,我们可以灵活地控制七段显示器的亮度,以适应不同的环境和用户需求。而使用Verilog实现PWM控制,能够方便地集成到FPGA项目中,通过简单的参数调整即可完成亮度的优化。

# 4. 综合应用项目:数字钟的设计与实现

## 4.1 数字钟的需求分析

### 4.1.1 功能描述与系统分解

数字钟作为一款基础的电子时计装置,其核心功能在于实时显示当前的时、分、秒信息。在设计数字钟时,我们需要关注以下几点功能需求:

- 显示当前的时、分、秒,采用24小时制或12小时制显示,可能包含AM/PM标识。

- 能够通过按钮手动设置当前时间。

- 具有时间校准功能,例如通过接收外部时间同步信号(如NTP网络时间协议)进行调整。

- 在Nexys 4 DDR这样的FPGA开发板上实现时,需要考虑资源分配和处理速度,以保证时间的精确度。

在系统分解上,数字钟的设计可细分为以下几个部分:

- **时钟模块**:负责生成和维护时间基准,内部使用计数器和逻辑门电路。

- **显示模块**:将时钟模块的输出信息转换为七段显示器上的可视数字。

- **控制模块**:处理外部输入(如按钮、网络信号等),并据此调整时钟模块的时间。

- **用户接口**:包括按钮和显示屏,用于用户输入和显示时间信息。

### 4.1.2 时钟模块的实现

在FPGA上实现时钟模块,我们通常会使用一个高频时钟信号作为计时基准。以 Nexys 4 DDR开发板为例,假设我们拥有一个50MHz的时钟输入,为了获得1秒的计时精度,我们需要一个计数器来累计时钟周期。

```verilog

module clock_module(

input clk, // 50MHz clock input

input reset, // Reset signal for initializing

output reg [5:0] sec, // 6-bit output for seconds (0-59)

output reg [5:0] min, // 6-bit output for minutes (0-59)

output reg [4:0] hour // 5-bit output for hours (0-23)

);

// Define constants for seconds and minutes

localparam MAX_SEC = 60;

localparam MAX_MIN = 60;

// Intermediate registers for counting

reg [25:0] count_1sec = 0; // Counts to 50 million for one second

always @(posedge clk or posedge reset) begin

if (reset) begin

// Reset the clock registers

sec <= 0;

min <= 0;

hour <= 0;

count_1sec <= 0;

end else begin

if (count_1sec >= MAX_SEC - 1) begin

// One second has elapsed

count_1sec <= 0;

sec <= sec + 1;

if (sec >= MAX_SEC - 1) begin

// One minute has elapsed

sec <= 0;

min <= min + 1;

if (min >= MAX_MIN - 1) begin

// One hour has elapsed

min <= 0;

hour <= hour + 1;

if (hour >= 24) begin

// Twenty-four hours have elapsed, reset the clock

hour <= 0;

end

end

end

end else begin

count_1sec <= count_1sec + 1;

end

end

end

endmodule

```

在上面的代码中,我们定义了一个名为 `clock_module` 的模块,它接收一个50MHz的时钟信号和一个复位信号。计时器使用一个26位的计数器 `count_1sec` 来实现每秒的计数。每当前一个计数器达到50,000,000次时,我们增加秒数计数器 `sec`,并相应地处理分钟和小时计数器 `min` 和 `hour`。

## 4.2 七段显示器在数字钟中的应用

### 4.2.1 数字钟显示逻辑的设计

在数字钟的设计中,七段显示器用于向用户展示当前时间。要将二进制时间数据转换为七段显示器能够理解的信号,我们需要设计一个显示逻辑模块,负责解码并驱动七段显示器。由于七段显示器直接对应0到9的数字,我们需要实现一个二进制到七段解码器。

```verilog

module display_decoder(

input [3:0] binary_input, // 4-bit binary input

output reg [6:0] seg // 7-segment output (a-g)

);

// Define the binary to 7-segment mapping

always @(binary_input) begin

case (binary_input)

4'b0000: seg = 7'b1000000; // 0

4'b0001: seg = 7'b1111001; // 1

4'b0010: seg = 7'b0100100; // 2

4'b0011: seg = 7'b0110000; // 3

4'b0100: seg = 7'b0011001; // 4

4'b0101: seg = 7'b0010010; // 5

4'b0110: seg = 7'b0000010; // 6

4'b0111: seg = 7'b1111000; // 7

4'b1000: seg = 7'b0000000; // 8

4'b1001: seg = 7'b0010000; // 9

default: seg = 7'b1111111; // Blank display for undefined inputs

endcase

end

endmodule

```

在这个 `display_decoder` 模块中,我们定义了一个4位输入 `binary_input` 来表示0到9的数字,以及一个7位输出 `seg` 来驱动七段显示器。通过一个 `case` 语句,我们根据输入的数字选择正确的段位编码,以点亮七段显示器的适当部分。

### 4.2.2 Verilog代码编写与调试

编写完基本的时钟模块和显示解码模块后,我们需要将它们整合到一起,并编写顶层模块,以实现整个数字钟的功能。在整合代码时,我们可能需要使用到FPGA开发板上的资源,例如按钮输入、七段显示器输出端口等。以下是一个简化的顶层模块示例:

```verilog

module digital_clock(

input clk, // 50MHz clock input from the board

input reset, // Active-high reset button from the board

input set, // Active-high set button from the board

input [3:0] btn, // Additional buttons for fine control

output [6:0] seg_0, // Segments for the unit seconds display

output [6:0] seg_1, // Segments for the tens seconds display

output [6:0] seg_2, // Segments for the unit minutes display

output [6:0] seg_3, // Segments for the tens minutes display

output [6:0] seg_4 // Segments for the unit hours display

// Other segments are omitted for brevity

);

wire [5:0] sec;

wire [5:0] min;

wire [4:0] hour;

clock_module clk_mod(

.clk(clk),

.reset(reset),

.sec(sec),

.min(min),

.hour(hour)

);

display_decoder dec_0(

.binary_input(sec % 10),

.seg(seg_0)

);

display_decoder dec_1(

.binary_input(sec / 10),

.seg(seg_1)

);

display_decoder dec_2(

.binary_input(min % 10),

.seg(seg_2)

);

display_decoder dec_3(

.binary_input(min / 10),

.seg(seg_3)

);

display_decoder dec_4(

.binary_input(hour % 10),

.seg(seg_4)

);

// ... Other decoders and control logic

endmodule

```

在顶层模块中,我们创建了时钟模块 `clk_mod` 和五个显示解码器实例 `dec_0` 到 `dec_4`,分别对应秒和分钟的单位与十位、以及小时的单位位。每个显示解码器接收相应的二进制输入,并输出对应的七段信号。顶层模块还需要根据按钮输入,如 `set` 按钮来调整当前时间。

## 4.3 系统集成与测试

### 4.3.1 整合各个模块

在数字钟的设计中,整合各个模块是非常关键的一步,需要确保所有的模块能够协同工作。整合过程中要注意以下几点:

- 确保信号命名清晰,避免命名冲突。

- 尽量减少信号在模块间的长距离传输,以降低延迟和电磁干扰。

- 使用约束文件正确配置FPGA开发板上的物理引脚。

### 4.3.2 测试流程和问题解决

在整合所有模块后,接下来是测试阶段。测试流程应该遵循以下步骤:

- **单元测试**:先测试单个模块的功能,确保它们各自能正常工作。

- **集成测试**:把各个模块结合起来,测试它们之间的交互。

- **功能测试**:验证整个系统的功能是否符合需求。

- **性能测试**:确保系统运行稳定,没有性能瓶颈。

在测试过程中,如果遇到问题,需要逐步排查,确定是哪个模块的问题,然后定位到具体代码段进行修复。

```markdown

总结:

在本节中,我们详细探讨了数字钟项目的需求分析、七段显示器的应用、以及系统集成与测试的流程。每个步骤都为数字钟项目的成功实施奠定了坚实的基础。从需求分析到实际操作,我们不仅涉及到了FPGA时钟模块的设计,还研究了数字显示逻辑,以及如何将这些模块有效地集成到一起。此外,测试流程确保了我们的设计能够达到预期的性能和功能要求,为下一章的高级开发技巧打下了良好的基础。

```

在上述内容中,我们已经深入探讨了数字钟项目的需求分析、七段显示器在数字钟中的应用,以及系统集成与测试。下一章将介绍 Nexys 4 DDR开发板上的高级开发技巧,包括高级外设接口技术、开发环境优化和项目开发经验分享。通过本章节的介绍,我们可以预见更深层次的技术细节和实施技巧,为更复杂的项目打下坚实的基础。

# 5. Nexys 4 DDR进阶开发技巧

## 5.1 高级外设接口技术

### 5.1.1 接口技术概述

在FPGA开发中,高级外设接口技术是连接外部设备与FPGA板卡的重要桥梁。这些接口技术可以是简单的并行接口,也可以是复杂的串行接口,例如USB、HDMI、SPI、I2C等。接口技术的核心在于确保数据传输的准确性和效率,同时兼容各种外部设备标准。

### 5.1.2 外设接口编程示例

下面是一个简单的SPI接口外设编程示例。在这个例子中,我们将通过SPI接口与一个模拟数字转换器(ADC)进行通信。代码是用Verilog编写的。

```verilog

module spi_master(

input wire clk, // 主时钟

input wire reset, // 复位信号

input wire start, // 开始信号

input wire [7:0] mosi_data, // 主输出从输入数据

output reg mosi, // 主输出从输入

input wire miso, // 主输入从输出

output reg sclk, // SPI时钟

output reg cs_n, // 片选信号,低电平有效

output reg done // 完成信号

);

// 状态机状态定义

localparam IDLE = 2'b00;

localparam TRANSFER = 2'b01;

localparam DONE = 2'b10;

reg [1:0] state = IDLE; // 状态机当前状态

reg [2:0] bit_cnt = 0; // 位计数器

// 时钟分频计数器

reg [7:0] clk_divider = 0;

// SPI时钟分频和位传输控制

always @(posedge clk or posedge reset) begin

if (reset) begin

// 重置所有信号和状态

sclk <= 0;

mosi <= 0;

cs_n <= 1;

done <= 0;

state <= IDLE;

end else begin

case (state)

IDLE: begin

if (start) begin

cs_n <= 0; // 拉低片选信号,开始传输

sclk <= 0; // 初始时钟设置为0

bit_cnt <= 0; // 位计数器重置

state <= TRANSFER;

end

end

TRANSFER: begin

// 时钟分频控制

clk_divider <= clk_divider + 1;

if (clk_divider == 8'hff) begin

clk_divider <= 0;

sclk <= ~sclk; // 翻转SPI时钟

if (sclk) begin

mosi <= mosi_data[7 - bit_cnt]; // 发送当前位数据

bit_cnt <= bit_cnt + 1;

if (bit_cnt == 8) begin

state <= DONE;

end

end

end

end

DONE: begin

cs_n <= 1; // 拉高片选信号,结束传输

done <= 1; // 设置完成信号

state <= IDLE;

end

endcase

end

end

endmodule

```

## 5.2 FPGA开发环境优化

### 5.2.1 集成开发环境(IDE)介绍

FPGA的集成开发环境(IDE)是整个开发过程的核心。Xilinx的Vivado和Intel的Quartus Prime是业界广泛使用的两个IDE。它们集成了设计输入、综合、实现、仿真和硬件调试等功能。此外,还支持高级语言和图形化编程,提高了开发效率。

### 5.2.2 优化编译流程和调试技巧

编译流程的优化可以在很大程度上提升工作效率,以下是一些优化策略:

1. **增量编译**:Vivado支持增量编译,这可以节省不必要的综合和实现时间。

2. **多核处理**:启用多核编译可以加速编译过程。

3. **分析综合报告**:使用报告中的关键信息,对设计进行优化。

4. **预综合优化**:在综合之前进行代码优化,如减少逻辑层次,减少时钟树分支等。

调试技巧包括:

1. **逻辑分析仪**:使用逻辑分析仪来捕获信号状态,观察时序问题。

2. **芯片外部引脚连接**:将FPGA的输出引脚连接到LED或示波器上,方便观察。

3. **仿真**:在实际烧录到FPGA前,进行充分的仿真测试。

## 5.3 项目开发经验分享

### 5.3.1 常见问题及解决方案

在FPGA项目开发中常见的问题包括时序违规、资源利用不充分和外设通信问题。对于时序违规,可以通过添加流水线、调整时钟域交叉策略或者改变布线来解决。资源优化可以使用资源分析工具进行,比如Vivado的Resource Utilization报告。外设通信问题可通过添加接口协议检查逻辑和使用更健壮的通信协议来解决。

### 5.3.2 优秀开发实践的总结

最后,以下是FPGA开发中的一些优秀实践:

- **代码模块化**:将功能模块化,便于重用和维护。

- **版本控制**:使用版本控制系统,如Git,记录设计变更。

- **硬件抽象层(HAL)**:为常用外设编写HAL,简化主程序代码。

- **测试驱动开发(TDD)**:首先编写测试用例,然后编写功能,保证设计质量。

通过遵循这些实践,不仅可以提高开发效率,还可以确保项目的质量与可维护性。

0

0