Nexys 4 DDR硬件解密:全面剖析开发板架构

发布时间: 2024-12-18 10:52:42 阅读量: 6 订阅数: 6

RGB_nexys4ddr亮灯_fpga_

# 摘要

本文详细介绍了Nexys 4 DDR开发板的技术细节与应用。首先对开发板的硬件基础进行了概述,包括主要的硬件组件及其功能,如FPGA核心板卡、内存和存储模块以及外围接口。接着阐述了软件开发环境,介绍了Xilinx开发工具链和硬件描述语言在设计实现中的应用。文章还探讨了Nexys 4 DDR在多媒体处理、外设接口扩展和网络通信等方面的高级应用实例。最后,讨论了性能优化与故障排除的策略,并分享了实际项目案例与实战经验,旨在为开发者提供深入的技术支持和实用建议。

# 关键字

Nexys 4 DDR;硬件基础;软件开发环境;高级应用;性能优化;故障排除

参考资源链接:[Nexys4-DDR开发板详解:Artix-7 FPGA的实践平台](https://wenku.csdn.net/doc/6469abfc5928463033e103cc?spm=1055.2635.3001.10343)

# 1. Nexys 4 DDR开发板概述

Nexys 4 DDR开发板是Xilinx公司推出的一款低成本的FPGA学习和开发平台,是众多电子工程师和在校学生在学习FPGA时的首选。本章将对Nexys 4 DDR开发板的基本情况进行一个概述,涵盖其设计理念、主要功能以及它在行业中的应用。

## 1.1 设计理念与定位

Nexys 4 DDR的设计理念是提供一个用户友好、价格合理的FPGA学习与开发环境。它集成了多个常用的接口和模块,使得用户能够在无需额外成本投入的情况下,学习FPGA基础、掌握硬件编程技能,并进行一些基础的硬件原型设计。

## 1.2 主要功能特点

Nexys 4 DDR开发板的主要特点包括:

- **FPGA核心板卡**:搭载Xilinx Artix-7系列FPGA,提供足够的逻辑单元以满足不同复杂度项目的需求。

- **内存和存储模块**:配备有大容量的DDR2内存和非易失性存储,用于运行复杂的程序和数据存储。

- **外围接口和扩展槽**:包括以太网接口、USB接口、Pmod和HDMI接口等多种扩展槽,方便与各类外围设备连接。

通过介绍Nexys 4 DDR的基本信息和特色,本章旨在为读者提供一个全面的开发板概览,为接下来深入了解硬件和软件开发环境奠定基础。

# 2. Nexys 4 DDR的硬件基础

### 2.1 主要硬件组件介绍

#### 2.1.1 FPGA核心板卡

在本节中,我们将深入探讨Nexys 4 DDR的核心组件,首先是FPGA(Field-Programmable Gate Array)核心板卡。FPGA是Nexys 4 DDR开发板的“大脑”,它具有大量的逻辑单元,可以实现复杂数字逻辑功能。Nexys 4 DDR采用的是Xilinx Artix-7系列的XC7A100T FPGA芯片。这款芯片集成了6系列的特性,例如,高容量的逻辑单元和高性能的I/O特性,使其成为学习数字系统设计和嵌入式处理的优秀平台。

#### 2.1.2 内存和存储模块

除了FPGA核心之外,Nexys 4 DDR还配备了多种内存和存储模块。核心板卡上有一个128Mbit的SPI闪存,用于存储配置数据和固件。另外,还提供了512Mb的DDR3 SDRAM,用以提供更大的数据存储和处理能力。这些内存模块为FPGA提供了运行时所需的数据和程序存储空间。

#### 2.1.3 外围接口和扩展槽

Nexys 4 DDR提供了一系列的外围接口和扩展槽,使得用户能够连接各种外设和模块。其中包括Pmod(Peripheral Module)接口,用于连接各种传感器和外围设备,还有用于连接显示器和摄像头的HDMI和VGA接口。除此之外,板上还有用于扩展如SD卡等存储设备的SD卡插槽。用户可以通过这些接口和槽位,将Nexys 4 DDR开发板应用到更广泛的场景中。

### 2.2 硬件连接和交互

#### 2.2.1 IO端口的分配和使用

Nexys 4 DDR的FPGA提供了丰富的I/O端口,这些端口被分配给板上的各种接口和设备。理解这些端口的分配对于用户设计电路和开发应用程序至关重要。例如,板上的开关和LED灯直接连接到FPGA的特定引脚上,用户可以通过编程这些引脚来控制开关的状态和LED的亮灭。在开发过程中,可以使用Xilinx Vivado工具来分配和配置这些端口,使其符合特定的应用需求。

#### 2.2.2 外部设备接口的通信协议

为了有效地与外部设备通信,Nexys 4 DDR采用了一系列的标准通信协议。这些协议包括串行通信接口SPI和I2C,以及USB和HDMI接口,它们各自有独特的数据传输协议。理解这些协议的细节对于开发高效、稳定的接口应用至关重要。例如,USB接口需要遵守USB协议来确保与不同设备间的兼容性。

#### 2.2.3 电源管理与功耗分析

在设计和使用Nexys 4 DDR开发板时,电源管理也是一个重要的考虑因素。开发板通过外部电源适配器供电,并且有专门的电压监控电路来确保稳定的操作电压。在功耗方面,开发板在不同工作模式下的功耗不同,因此用户需要根据实际应用场景合理配置电源和散热系统,以避免过热和潜在的硬件损坏。

为了进一步阐释Nexys 4 DDR的硬件基础,我们可以观察一个简单的示例——LED闪烁程序。这个程序利用FPGA上的I/O端口控制板上LED灯的亮灭,演示了基础硬件交互的过程。

```vhdl

-- VHDL 示例代码:LED闪烁程序

entity led_blink is

Port ( led : out STD_LOGIC;

clk : in STD_LOGIC);

end led_blink;

architecture Behavioral of led_blink is

signal counter : integer := 0;

begin

process(clk)

begin

if rising_edge(clk) then

counter <= counter + 1;

if counter = 50000000 then -- 假设时钟频率为50MHz

led <= NOT led; -- 切换LED状态

counter <= 0;

end if;

end if;

end process;

end Behavioral;

```

在这个VHDL代码片段中,我们定义了一个简单的计数器来生成延时,并在达到特定计数值时切换LED的状态。这个过程演示了如何使用时钟信号(clk)和输出信号(led)来控制硬件设备。

针对上述代码,硬件逻辑的实现及参数说明如下:

- `entity led_blink`:定义了一个VHDL模块,它有`led`输出信号和`clk`输入信号。

- `architecture Behavioral`:描述了模块的工作逻辑。

- `signal counter`:是一个整型计数器,用于实现定时功能。

- `process(clk)`:定义了一个进程块,它在时钟信号的上升沿触发。

- `counter <= counter + 1`:在每个时钟周期计数器值增加1。

- `if counter = 50000000 then`:检查计数器是否达到50MHz时钟周期的预设值,约等于1秒。

- `led <= NOT led`:切换LED灯的状态。

通过这段简单的代码和逻辑分析,我们可以看到FPGA在硬件控制中的基本应用方式,这对于理解Nexys 4 DDR的硬件基础非常有帮助。接下来我们将深入探讨Nexys 4 DDR的软件开发环境,以获得更全面的开发体验。

# 3. Nexys 4 DDR的软件开发环境

## 3.1 Xilinx开发工具链概览

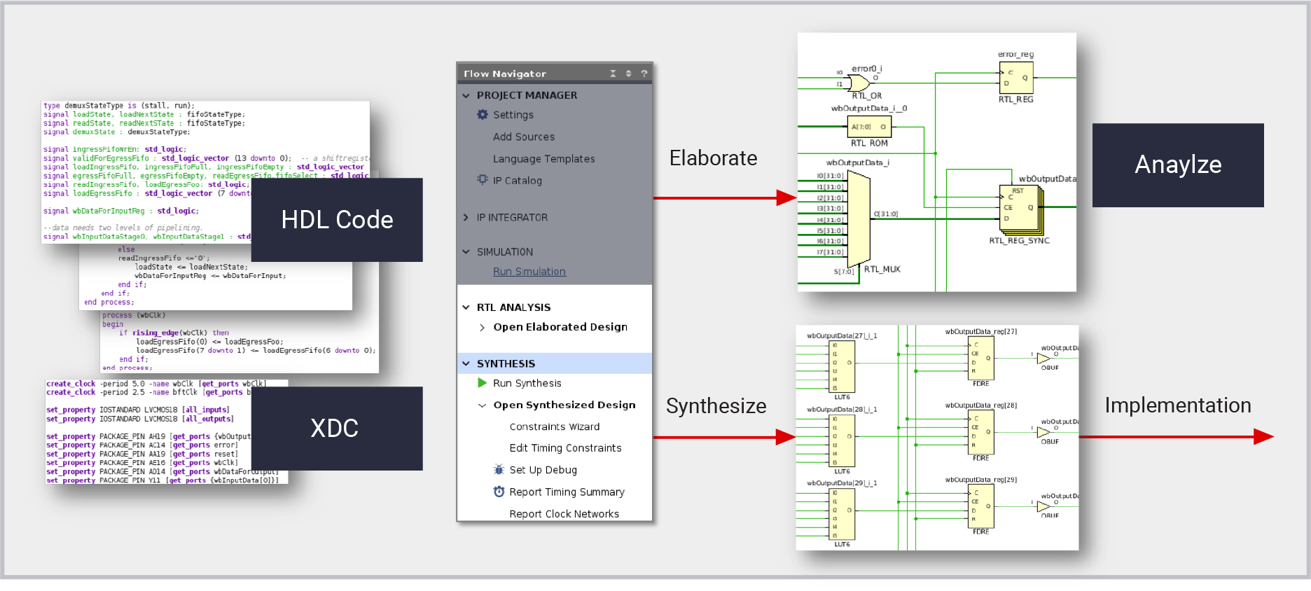

### 3.1.1 Vivado设计套件的基础

Vivado是Xilinx公司推出的全面重新设计的FPGA设计套件,它改变了从设计输入到芯片配置的整个设计流程。Vivado支持更高级别的抽象设计,提供了更高的设计生产力和更快的时序收敛。它对各种规模的设计均有优化,包括系统级芯片(SoC)设计、IP集成、HDL仿真和分析、综合、布局布线以及针对特定用途的优化等。

Vivado设计套件的基本架构包含以下几个主要部分:

- **HDL分析和仿真:** Vivado HLS (高层次综合) 能够将C/C++/System C代码转换成硬件实现,简化了从算法到硬件的转化过程。Vivado也内置了功能强大的仿真工具,可以对设计进行详尽的测试。

- **综合和优化:** Vivado综合工具可以将HDL代码转换成逻辑元件并进行优化,以满足时序要求和性能目标。它支持快速重综合,这对于实现设计的迭代改进非常有用。

- **实现:** 这部分包括了布局布线、时序约束的实施和时序优化。Vivado的实现算法针对当前和下一代FPGA架构进行了优化,提供快速且高质量的实现结果。

- **分析和调试:** Vivado提供了详尽的设计分析工具,包括逻辑分析仪、功率分析和时序分析。这些工具帮助设计师识别设计中可能存在的问题,并在上板前进行修复。

在使用Vivado设计套件时,设计者必须理解其设计理念和使用方法,这对于充分发挥Nexys 4 DDR开发板的性能至关重要。

### 3.1.2 SDK集成开发环境

Xilinx SDK(软件开发套件)是为Zynq和其他Xilinx SoC产品专门设计的开发环境,是Vivado套件的一个组成部分。它提供了一个集成的开发平台,支持软件和硬件的设计集成,大大简化了嵌入式系统的开发过程。

SDK的主要特点包括:

- **多核处理器支持:** SDK支持双核ARM Cortex-A9处理器,允许开发人员充分利用处理器的性能。

- **图形化用户界面:** SDK的GUI简化了软件开发过程,包括项目管理、源代码编辑、调试等。

- **系统配置工具:** 允许设计人员配置处理器和外设,设置内存映射和中断系统。

- **软件库和驱动程序:** 提供丰富的软件库和驱动程序,方便开发人员访问FPGA内部和外部的资源。

SDK允许开发者编写、编译和调试运行在Nexys 4 DDR开发板上的C/C++代码。通过与Vivado设计套件的集成,开发者可以实现软件与硬件之间的无缝交互。

## 3.2 硬件描述语言与设计实现

### 3.2.1 VHDL和Verilog的使用

VHDL(VHSIC Hardware Description Language)和Verilog是硬件描述语言(HDL)的两个主要标准,用于描述数字逻辑电路。在Nexys 4 DDR开发板的开发中,它们是将设计从概念转换为实际硬件实现的关键工具。

在使用HDL进行设计时,重要的是要遵守一定的设计流程和编码风格:

- **模块化设计:** 以模块为单位组织设计,每个模块完成特定的功能。

- **顶层模块:** 顶层模块负责将各个子模块连接起来,形成完整的电路设计。

- **仿真测试:** 在综合之前,应使用仿真工具测试各模块的功能正确性。

- **综合和实现:** VHDL和Verilog代码需要被综合工具转换为FPGA可实现的逻辑门和触发器。

例如,一个简单的VHDL模块如下所示:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity AND_gate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

Y : out STD_LOGIC);

end AND_gate;

architecture Behavioral of AND_gate is

begin

Y <= A and B;

end Behavioral;

```

在这个模块中,我们定义了一个简单的AND门电路,它有两个输入(A和B)和一个输出(Y)。这样的模块可以被综合成FPGA内部的逻辑元件。

### 3.2.2 硬件仿真与调试

硬件仿真允许设计者在将设计下载到实际硬件之前,验证其逻辑和功能是否正确。仿真工具有助于发现设计中的错误和缺陷,并允许开发者在不同的情景下测试设计。

在进行硬件仿真时,通常包括以下步骤:

1. **编写测试台(Testbench):** 测试台是一个特殊的HDL模块,用于模拟设计的外部环境,产生输入信号,并观察输出信号。

2. **仿真运行:** 使用仿真工具(如Vivado的仿真器)执行测试台,生成仿真波形和日志文件。

3. **结果分析:** 分析仿真输出,确保设计的输出与预期一致。

4. **调试:** 如果发现逻辑错误,需要回到HDL代码进行修改,并重新进行仿真。

在设计较复杂的情况下,可能还会需要使用逻辑分析仪等硬件工具来观察FPGA引脚上的实际信号,帮助调试和验证设计。

## 3.3 下载、配置和测试程序

### 3.3.1 JTAG与iMPACT工具的使用

JTAG(Joint Test Action Group)是一种被广泛采用的标准协议,用于测试芯片和电路板,并且提供了用于编程和调试FPGA的接口。iMPACT是Xilinx提供的一个用于配置FPGA的工具集,支持多种配置模式,包括JTAG配置。

使用JTAG配置FPGA的一般流程如下:

1. **设计综合和实现:** 在Vivado中完成设计的综合和实现,生成比特流文件。

2. **打开iMPACT工具:** 运行iMPACT软件,并且导入生成的比特流文件。

3. **配置设备:** 通过JTAG将比特流文件下载到FPGA中。连接好JTAG电缆后,点击配置按钮开始下载过程。

4. **验证和测试:** 下载完成后,可以执行各种测试来验证设计的功能正确性。

使用iMPACT进行JTAG配置的优点包括快速编程,可以在几秒钟内完成下载过程,同时也支持即时的更新和测试。

### 3.3.2 开发板的配置流程

开发板配置是一个将设计实现下载到FPGA中的过程。这个过程可以在开发的任何阶段执行,用于实现新的设计或者更新现有设计。下面是配置Nexys 4 DDR开发板的一般步骤:

1. **硬件连接:** 确保开发板与计算机通过JTAG电缆正确连接,并且开发板的电源开关已打开。

2. **生成比特流文件:** 在Vivado中运行实现流程,生成比特流文件。

3. **启动iMPACT:** 打开iMPACT,根据需要选择合适的配置模式。

4. **选择设备:** iMPACT会检测到连接的FPGA设备,选择正确的设备型号。

5. **下载比特流:** 选择导入的比特流文件,并执行下载到FPGA的操作。

6. **功能验证:** 配置完成后,可以运行一些测试程序来验证设计的功能。

### 3.3.3 功能验证与性能测试

功能验证是确保设计按预期工作的重要步骤。在完成配置之后,验证设计是否满足所有的功能要求是至关重要的。为了验证设计,可以编写一系列的测试向量,并通过仿真和实际硬件测试来执行这些测试向量。

性能测试则是为了评估设计在速度和资源利用上的表现。在Nexys 4 DDR开发板上,性能测试通常包括:

- **时序分析:** 检查设计是否满足时序要求,没有违反时序约束。

- **资源占用:** 评估FPGA资源的利用情况,包括查找表(LUTs)、寄存器、内存块等。

- **功耗评估:** 通过实际测量或仿真工具评估设计的功耗。

性能测试是优化设计和提高整体性能的重要依据。在实际应用中,测试可以使用一些标准的测试平台和基准测试,这些测试针对不同类型的逻辑设计进行优化。

# 4. Nexys 4 DDR的高级应用实例

Nexys 4 DDR开发板不仅仅是一个学习工具,它还能够用于开发各种高级应用,尤其在多媒体处理、外设接口扩展以及网络和通信协议实现方面。本章节将探讨如何运用这些功能,以及如何将Nexys 4 DDR开发板的应用潜力最大化。

## 4.1 多媒体处理与接口应用

### 4.1.1 视频与图像处理模块

多媒体处理通常涉及到大量的数据处理,而FPGA由于其并行计算的特性,在视频和图像处理方面有着得天独厚的优势。Nexys 4 DDR开发板装备了足够的资源以进行基本的图像处理。

**实现步骤:**

1. **硬件配置:** 使用Vivado设计套件在Nexys 4 DDR上配置FPGA,为其加载图像处理硬件逻辑。

2. **视频源接入:** 将视频源(如摄像头模块)通过Pmod接口连接到开发板。

3. **图像处理:** 设计图像处理逻辑(例如边缘检测、色彩转换等)并将其下载到FPGA。

4. **结果展示:** 将处理后的图像信号输出到显示器或通过HDMI接口显示。

**代码示例与分析:**

```verilog

// 一个简单的Verilog模块,用于灰度化处理

module grayscale(

input wire clk,

input wire [23:0] rgb_in, // 假定24位RGB输入

output reg [7:0] gray_out // 8位灰度输出

);

always @(posedge clk) begin

// 计算灰度值,这里简单使用加权平均方法

gray_out <= (rgb_in[23:16]*30 + rgb_in[15:8]*59 + rgb_in[7:0]*11) / 100;

end

endmodule

```

在这个Verilog代码块中,我们定义了一个模块`grayscale`用于将彩色图像转换为灰度图像。每个时钟上升沿,它读取一个RGB值,通过加权求和计算灰度值,并输出。

### 4.1.2 音频接口与信号处理

音频处理同样是多媒体应用中的一个常见领域。Nexys 4 DDR提供了音频接口,使得在板卡上实现音频信号的处理成为可能。

**实现步骤:**

1. **音频模块连接:** 将音频输入输出模块通过Pmod接口连接到Nexys 4 DDR。

2. **音频信号捕获:** 使用ADC将模拟音频信号转换为数字信号。

3. **信号处理:** 编写FPGA逻辑以对数字音频信号进行处理(如噪声消除、频率均衡等)。

4. **信号输出:** 将处理后的音频信号通过DAC转换回模拟信号,或直接输出数字音频。

音频处理通常更复杂,因为它可能需要实时处理大量数据,同时保持低延迟。Nexys 4 DDR的FPGA资源足够用于实现一些基本的音频处理算法。

## 4.2 外设接口的扩展与应用

### 4.2.1 USB接口与数据传输

现代计算设备几乎无一例外地使用USB接口进行数据交换,因此能够在FPGA板卡上实现USB接口功能是非常有价值的。

**实现步骤:**

1. **USB模块选择:** 选择合适的USB接口模块,Nexys 4 DDR可以通过Pmod接口连接。

2. **USB固件开发:** 使用Vivado开发USB固件逻辑,以实现USB通信协议。

3. **驱动开发:** 如果需要,编写USB设备驱动程序,以便在计算机上识别和通信。

4. **数据传输测试:** 测试USB接口的数据传输速率和稳定性。

**表格展示USB接口实现细节:**

| USB接口类型 | 数据传输速率 | 协议复杂度 | 推荐应用场景 |

| ------------ | -------------- | ------------ | --------------- |

| USB 2.0 | 最高480 Mbps | 中等 | 高速数据采集 |

| USB 3.0 | 最高5 Gbps | 高 | 高清视频流传输 |

### 4.2.2 Pmod与HDMI接口的编程实践

Nexys 4 DDR开发板集成了HDMI接口,提供了标准的数字视频和音频输出能力。Pmod则提供了额外的灵活性,允许连接各种自定义模块和传感器。

**实现步骤:**

1. **HDMI输出设置:** 使用Xilinx IP核生成HDMI视频信号,并通过HDMI接口输出。

2. **Pmod模块接入:** 将所需的Pmod模块接入开发板的相应插槽。

3. **数据采集与处理:** 编写逻辑来采集Pmod模块的数据并进行处理。

4. **显示与交互:** 将处理后的数据显示在HDMI监视器上,并与用户交互。

**代码示例:**

```verilog

// 一个简单的Verilog模块,用于将数据输出到HDMI接口

module hdmi_output(

input wire clk, // 时钟信号

input wire [23:0] data_in, // 输入的RGB数据

output wire hsync, vsync, // 行场同步信号

output wire [7:0] red, green, blue // HDMI颜色分量输出

);

// HDMI IP核实例化代码...

// HDMI输出逻辑代码...

endmodule

```

在这个例子中,我们将一个RGB视频数据流通过HDMI发送到显示器。在实际的实现中,HDMI IP核需要正确配置,以满足显示设备的要求。

## 4.3 网络与通信协议实现

### 4.3.1 Ethernet接口与网络通信

Nexys 4 DDR板卡的网络功能使其可以连接到本地网络,与远程设备进行通信。

**实现步骤:**

1. **网络接口配置:** 在Vivado中配置MAC和PHY IP核,以实现以太网通信。

2. **TCP/IP协议栈集成:** 集成TCP/IP协议栈到FPGA设计中,以便进行高级网络通信。

3. **数据包处理:** 设计数据包的发送和接收逻辑。

4. **功能测试与验证:** 通过实际的网络通信测试功能,确保数据传输的准确性和稳定性。

### 4.3.2 无线通信模块的应用案例

随着物联网的发展,无线通信功能变得越来越重要。Nexys 4 DDR可以通过添加额外的模块来支持无线通信,如Wi-Fi或蓝牙。

**实现步骤:**

1. **无线模块选择:** 根据应用需求选择合适的无线通信模块。

2. **硬件接入:** 将无线模块通过Pmod接口连接到Nexys 4 DDR。

3. **软件开发:** 在FPGA上编写无线通信的协议逻辑。

4. **功能验证:** 通过与其它无线设备的通信来验证模块的功能。

本章节通过对Nexys 4 DDR开发板在多媒体处理、外设接口扩展以及网络通信方面应用实例的探讨,展示了如何将这些高级功能融入到项目中,进而实现各种复杂的硬件设计和应用程序。通过精心设计的案例,读者可以更深入地理解Nexys 4 DDR在实际应用中的强大功能和灵活性。

# 5. Nexys 4 DDR的性能优化与故障排除

在Nexys 4 DDR开发板的使用过程中,性能优化与故障排除是确保系统稳定运行的关键。本章节将探讨性能分析工具的使用,资源利用率的优化方法,以及遇到问题时的故障诊断步骤。

## 5.1 系统性能分析与优化方法

### 5.1.1 性能评估工具的使用

性能评估是优化过程的第一步。Xilinx提供了多个工具,如Vivado中的时序分析器和资源分析器,用于评估FPGA设计的性能。

- **时序分析器**:通过检查设计中的时序约束是否满足,可以确保数据在逻辑单元之间可靠地传输。

- **资源分析器**:用于查看资源利用率,比如查找表(LUTs)、寄存器、块RAM和数字信号处理器(DSP)的使用情况。

在Vivado中,可以通过以下步骤使用这些分析器:

1. 打开Vivado并加载您的项目。

2. 在设计视角中,点击“Run Implementation”完成设计实现。

3. 实现完成后,进入“Synthesis”->“Run Timing Analysis”和“Run Utilization”来获取时序和资源利用报告。

### 5.1.2 资源利用率优化策略

资源利用率优化涉及到设计的改进,以减少对FPGA硬件资源的需求,从而提升性能和降低功耗。

- **优化代码逻辑**:使用更高效的数据流和控制流结构,减少不必要的逻辑。

- **模块化设计**:将大型设计分解成更小的模块,有助于资源重用。

- **异步逻辑优化**:减少异步逻辑的使用,因为它们可能会引入不可预测的延迟。

优化的一个典型示例是减少逻辑层级深度,这可以通过合并逻辑门或简化算术操作来实现。这通常意味着在设计源代码中进行迭代和修改,直至满足资源限制。

## 5.2 常见问题与故障诊断

### 5.2.1 硬件故障的排查流程

硬件故障可能会导致开发板无法正常工作。以下是排查硬件故障的步骤:

1. **视觉检查**:检查开发板上的所有接插件是否正确连接,焊点是否完好。

2. **供电检查**:使用万用表检查电源输出是否稳定,电压是否符合规格。

3. **板载LED指示灯**:监控板载LED的状态,通常指示灯可以提供关于设备工作状态的快速反馈。

### 5.2.2 软件故障的调试技巧

软件故障可能是由不正确的配置、代码错误或资源冲突引起的。调试软件故障的技巧包括:

- **使用Vivado逻辑分析仪**:捕获和分析设计中信号的行为。

- **编写自检代码**:实现一些简单的测试程序,用来检查各个模块的运行状态。

- **逐级调试**:如果可能的话,逐步加载设计的不同部分,检查在哪一步出现错误。

当遇到复杂问题时,创建一个最小、完整、可验证(MCVE)的测试案例,可以帮助快速定位问题。

## 5.3 项目案例与实战经验分享

### 5.3.1 实际项目中遇到的挑战

在实际项目中,开发团队可能会遇到各种挑战,包括但不限于:

- **资源限制**:在设计大型系统时,可能会面临资源不足的问题。

- **时序收敛**:高速信号传输可能引发时序问题,要求设计者有更高的时序约束知识。

- **热管理**:FPGA在高负载下可能会产生大量热量,需要有效的散热措施。

### 5.3.2 高效开发与团队协作经验

- **版本控制**:使用Git等版本控制系统跟踪代码变更。

- **持续集成**:实施持续集成流程确保代码质量,例如使用GitHub Actions进行自动化测试。

- **知识共享**:定期举行内部培训和知识分享会,提升团队整体技术水平。

这些实战经验可以帮助开发团队在遇到项目挑战时,以更系统化的方式解决问题。

以上所述的工具使用、优化策略、故障排查方法,以及项目经验,都是在Nexys 4 DDR开发板使用过程中,提升性能和解决实际问题时至关重要的。通过遵循这些步骤,我们可以有效地提高系统的性能,确保开发板的稳定运行。

0

0