Nexys 4 DDR时钟管理秘技:掌握精确同步的艺术

发布时间: 2024-12-18 11:16:36 阅读量: 7 订阅数: 5

# 摘要

本文针对Nexys 4 DDR开发板的时钟管理系统进行了全面探讨,涵盖时钟管理基础、同步原理、实践技巧以及高级应用等关键内容。通过深入分析时钟域的概念和重要性、同步机制的理论基础以及同步方法的对比选择,本文提供了有效的时钟管理实践技巧,包括配置FPGA时钟资源、编写时钟管理代码以及处理时钟域交叉问题。进一步地,文章还探讨了高级同步技术在FPGA中的应用,并提出了优化时钟管理性能的策略。通过对精选案例的分析与实验验证,本文揭示了时钟同步在具体应用项目中的实现方法和故障排除技巧,为相关领域的工程师和技术人员提供了宝贵的技术参考和实操指导。

# 关键字

Nexys 4 DDR;时钟管理;时钟同步;时钟域交叉;FPGA配置;性能优化

参考资源链接:[Nexys4-DDR开发板详解:Artix-7 FPGA的实践平台](https://wenku.csdn.net/doc/6469abfc5928463033e103cc?spm=1055.2635.3001.10343)

# 1. Nexys 4 DDR时钟管理基础

在现代数字系统设计中,Nexys 4 DDR FPGA板是教学和工业应用中常用的一种开发平台,其强大的时钟管理能力是它的一大亮点。正确理解和掌握Nexys 4 DDR的时钟管理系统是进行高效FPGA设计的关键。本章将为您介绍时钟管理的基本概念,并为后续章节打下坚实的基础。

## 1.1 FPGA时钟资源概述

FPGA(Field-Programmable Gate Array)提供了灵活的时钟资源,允许设计师通过编程配置时钟网络以满足特定的时钟需求。Nexys 4 DDR板搭载的Xilinx Artix-7系列FPGA为实现复杂的时钟管理提供了丰富资源,包括全局时钟缓冲区(BUFG)、区域时钟缓冲区(BUFH)和专用时钟输入引脚等。

## 1.2 时钟域的概念及其重要性

在数字逻辑设计中,"时钟域"是一个与特定时钟信号同步工作的电路区域。理解时钟域及其管理对于避免可能的时钟域交叉(CDC)问题至关重要。在接下来的章节中,我们将深入探讨如何识别并处理时钟域交叉问题。

## 1.3 时钟管理的目标与挑战

时钟管理的目标是确保整个系统中时钟信号的一致性、稳定性和可靠性。由于FPGA系统中可能存在多个时钟源和多种时钟频率,设计者面临的挑战是如何设计出既能保证性能又能稳定工作的时钟管理方案。这些问题将在后续章节中通过具体的案例和实验进行剖析。

通过本章内容的阅读,您将建立起对Nexys 4 DDR时钟管理的基本理解,为学习更深层次的时钟同步原理与实践技巧打下坚实基础。

# 2. 时钟同步原理详解

### 2.1 时钟域的概念及其重要性

#### 2.1.1 时钟域定义与分类

在数字系统设计中,特别是FPGA与ASIC设计,时钟域是指由同一个时钟信号驱动的同步元件集合。这些元件在逻辑功能上是相关的,并且在时间上是协调一致的。根据功能的不同,时钟域可以被分为两大类:全局时钟域和局部时钟域。全局时钟域指的是覆盖整个系统或大部分设计的时钟域,例如主时钟信号。局部时钟域则通常与特定的功能模块相关,例如数据路径、控制逻辑等。

时钟域交叉(CDC)问题是数字系统设计中的一个常见问题,指的是数据在两个不同的时钟域之间传输时,可能会导致数据的不稳定和不可预测的行为。这个问题的关键在于不同的时钟域拥有不同的时钟信号,这些信号频率、相位可能不一致。

时钟域分类的目的在于提高设计的可管理性和可维护性,尤其是在复杂的系统中,有效的时钟域管理可以确保数据的正确传输和处理。

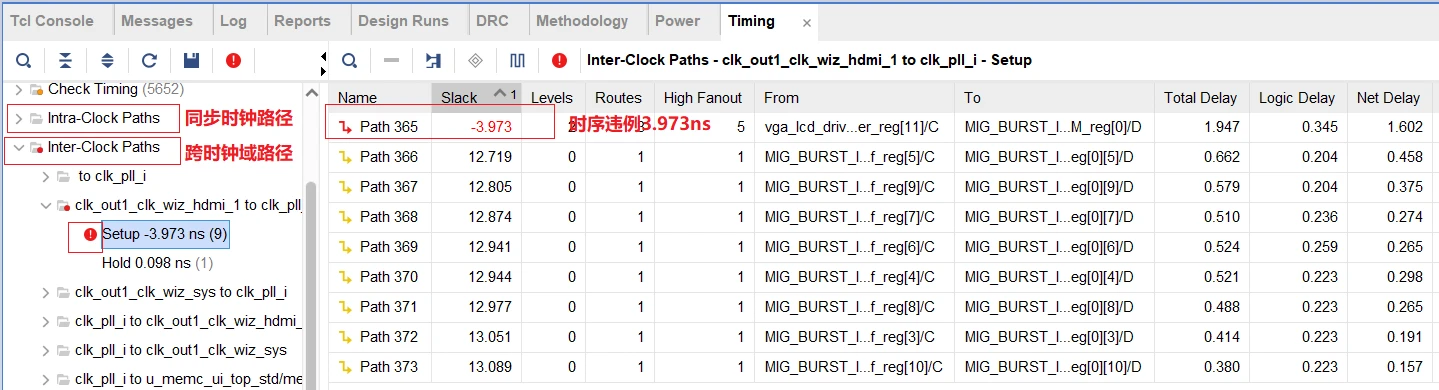

#### 2.1.2 时钟域交叉问题解析

在现代数字系统设计中,时钟域交叉是一个需要特别关注的问题。当数据从一个时钟域传输到另一个时钟域时,由于时钟频率或者相位的差异,可能会产生数据失配、竞争条件等问题,最终导致系统不稳定或者功能失效。

为了解决时钟域交叉问题,设计者通常会采用一些同步机制来确保数据在跨越时钟域时的稳定性。常用的同步机制包括双触发器同步(Double Flop Synchronization)、握手协议(Handshaking Protocol)、脉冲同步器(Pulse Synchronizer)等。通过这些方法可以有效减少由于时钟域交叉导致的数据丢失和数据竞争等问题。

### 2.2 同步机制的理论基础

#### 2.2.1 同步信号的传播与稳定

同步信号是确保数字电路能够按照预定的时序运行的关键。在FPGA设计中,同步信号的传播需要满足以下原则:首先,信号必须在建立时间(setup time)和保持时间(hold time)内稳定;其次,信号传播过程中要避免过长的路径,以免产生过多的延迟,导致时序违反。

为了稳定同步信号,设计者通常会考虑以下几点:优化逻辑设计以减少路径的长度、使用高速逻辑器件、合理分配时钟资源,并使用时钟树优化(Clock Tree Synthesis, CTS)等技术来改善时钟信号的质量。这些技术能够帮助减少时钟歪斜(skew)、减少时钟延迟、并确保信号在规定时间内正确到达。

#### 2.2.2 同步设计的关键技术

同步设计是数字电路设计中的核心技术之一。它涉及许多方面,包括时钟域的划分、时钟树的构建、以及时钟域间同步机制的实现。在设计时,设计者会基于同步设计的关键技术,如时钟分频、时钟倍频、时钟多路复用等,来确保电路的正常运行。

时钟分频可以降低时钟频率,以匹配特定功能模块的需要;时钟倍频则用于提供更高频率的时钟信号。时钟多路复用允许多个时钟信号共享一个物理时钟线,这有助于减少物理资源的占用。此外,设计者还会使用各种同步技术,如双触发器同步、脉冲同步等,来解决时钟域之间的同步问题。

### 2.3 同步方法的对比与选择

#### 2.3.1 传统同步方法的局限性

传统同步方法在解决时钟域交叉问题上,虽然有效但仍有局限性。例如,双触发器同步在处理高速信号时可能会引入较大的延迟,从而限制了系统的整体性能。传统的握手协议则可能因为复杂的控制逻辑而增加设计复杂度和延时。

这些局限性要求设计者在实际应用中,不仅需要考虑同步方法的有效性,还要考虑到系统的性能要求、资源的占用以及设计的复杂性。因此,对于不同的应用场景,需要仔细评估并选择合适的同步方法。

#### 2.3.2 现代同步技术的创新点

随着技术的发展,现代同步技术在解决时钟域交叉问题上展现出了新的特点。这些技术包括基于异步FIFO(First-In-First-Out)的设计、使用特殊的同步器元件、以及采用更加智能化的时钟管理策略。

异步FIFO设计通过在不同的时钟域之间建立一个独立的存储单元来解决时钟域交叉问题,它能够在不需要严格同步的情况下,保证数据的稳定传输。特殊的同步器元件如握手电路、序列检测器等,可以提供更可靠的数据同步机制。而更智能化的时钟管理策略,比如时钟门控(Clock Gating)技术,可以在减少功耗的同时,确保系统时钟的正确和稳定。

通过结合现代同步技术,设计者可以在保证数据完整性的同时,提高系统的性能和可靠性。这为高速、高复杂度的数字系统设计提供了更多的可能性。

# 3. Nexys 4 DDR时钟管理实践技巧

## 3.1 配置FPGA时钟资源

### 3.1.1 时钟引脚的分配

在处理FPGA时钟资源时,首要步骤是确定时钟引脚的分配策略。Nexys 4 DDR板上的FPGA——Xilinx Artix-7系列芯片,提供了灵活的时钟输入和输出管理能力。正确配置时钟引脚对于确保系统时钟的稳定性和准确性至关重要。以下是配置时钟引脚的一些关键点:

- **识别时钟引脚**:Xilinx Artix-7 FPGA的时钟引脚通常具有`GTPCLK`、`MGTCLK`等前缀。在配置时,需要确认引脚位置,例如查看Nexys 4 DDR的技术手册或使用Vivado等工具中的引脚规划器。

- **时钟扇出**:在确定了输入时钟引脚后,需要为每个时钟域选择合适的扇出位置,以最小化时钟路径的延迟并保持信号质量。

- **考虑外围设备**:如果FPGA需要与外部设备(如DDR内存、以太网 PHY等)通信,则需为这些接口预留专用时钟引脚,以满足特定的时序要求。

```mermaid

flowchart LR

A(开始分配时钟引脚) --> B(识别FPGA时钟引脚)

B --> C(时钟扇出规划)

C --> D(预留外围设备时钟引脚)

D --> E(验证时钟分配方案)

```

### 3.1.2 时钟管理器的使用与配置

时钟管理器是FPGA中用于产生和管理时钟信号的关键组件。Nexys 4 DDR的Xilinx Artix-7 FPGA集成了数字时钟管理器(DCM)和相位锁定环(PLL)等资源,能够实现诸如时钟分频、倍频、相移等功能。以下是配置时钟管理器的基本步骤:

- **打开Xilinx Vivado**:启动Vivado,创建或打开一个项目,并指定Nexys 4 DDR硬件平台。

- **添加时钟管理器IP核**:在Viv

0

0