【高级玩法】:扭环形计数器的进阶使用技巧(时序逻辑优化大揭秘)

发布时间: 2024-12-28 12:14:34 阅读量: 5 订阅数: 11

# 摘要

扭环形计数器作为一种重要的时序逻辑电路,在数字系统设计中扮演着核心角色。本文从扭环形计数器的基本概念和理论入手,深入探讨了其工作原理、类型特点、性能分析以及优化策略。接着,文章详细介绍了高级应用技巧,包括定制化设计和故障诊断方法。通过模拟与仿真的章节,作者展示了如何选择模拟工具、实施技巧,并通过仿真案例进行了深入分析。文章的后半部分聚焦于扭环形计数器在复杂系统中的应用,探讨了与其它组件的协同工作以及系统级时序逻辑的挑战。最终,文章展望了新技术对扭环形计数器未来的影响,讨论了其发展前景和创新实践。

# 关键字

扭环形计数器;时序逻辑;性能优化;模拟仿真;系统集成;技术创新

参考资源链接:[扭环形计数器:同步二进制与N进制逻辑详解](https://wenku.csdn.net/doc/5u1ne7av12?spm=1055.2635.3001.10343)

# 1. 扭环形计数器简介与基础

## 1.1 扭环形计数器的定义与应用

扭环形计数器是一种数字电路设备,用于记录和追踪事件发生的次数。它通过一种特制的“环形”结构,实现对事件频率的计数。在信息技术、工业自动化、航空航天和其他高精密度领域中,扭环形计数器发挥着至关重要的作用。

## 1.2 基本工作原理

扭环形计数器基于环形结构,通过一组反相器(或称作“环状线性反馈移位寄存器”)与一组与门(AND gates)实现计数功能。每个计数周期,数据在寄存器中按一定规则进行移位,与门用于检测特定模式,从而实现计数逻辑。

## 1.3 计数器的数字表示与实例

计数器通过二进制数来表示计数值。例如,一个4位的扭环形计数器可以通过4个触发器来实现,触发器的状态会在每个计数周期变化,按照二进制顺序进行计数,从0000到1111,然后回到0000继续计数。

扭环形计数器由于其结构简单,成本较低,且易于实现和理解,成为许多应用中的首选计数器类型。下一章,我们将深入探讨其工作原理的各个方面。

# 2. 扭环形计数器的理论深入

### 2.1 扭环形计数器的工作原理

#### 2.1.1 扭环形计数器的结构组成

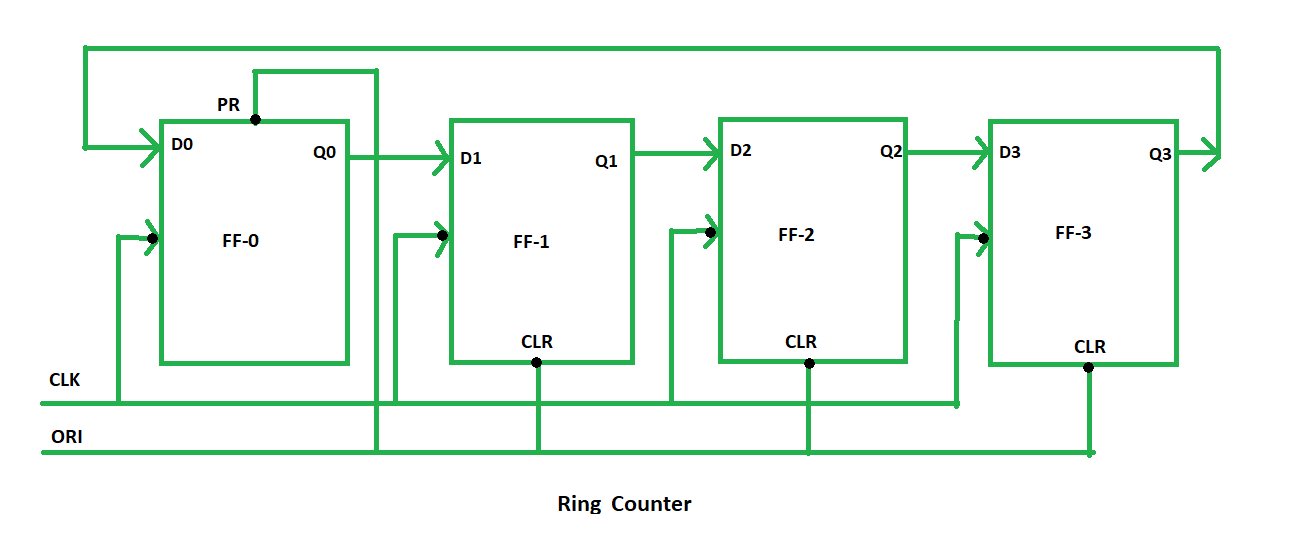

扭环形计数器(也称为环形计数器)是一种序列生成电路,它由一系列的D触发器构成,每个触发器的输出都连接到下一个触发器的输入。这种连接方式形成了一个环状结构,因此得名“扭环形”。环形计数器的结构非常简单,通常只需要N个D触发器就可以构建一个模数为N的计数器。

下面是一个简单的扭环形计数器结构图:

```mermaid

graph LR

A[D触发器] --> B[D触发器]

B --> C[D触发器]

C --> A

```

在该结构中,每个D触发器的输出连接到下一个D触发器的输入。D触发器的时钟输入端通常会被同步的时钟信号所驱动。在复位信号(Reset)的控制下,扭环形计数器可以被初始化到一个已知的状态,这通常是计数序列的起始点。

#### 2.1.2 时序逻辑的核心概念

时序逻辑是一种电路设计方法,其中输出不仅取决于当前的输入,还取决于电路的先前状态。扭环形计数器就是时序逻辑电路的一个实例。为了理解扭环形计数器的工作,首先需要了解一些基础的时序逻辑概念:

- **状态**:在任何给定的时间点,电路的输出可以被认为是其当前的状态。

- **状态转换**:在时钟信号的驱动下,电路的状态会根据输入信号和当前状态进行转换。

- **触发器**:是实现时序逻辑的关键组件,能够存储和转移比特信息。

- **时钟信号**:决定了状态转换发生的时刻,通常是一个周期性的脉冲信号。

在扭环形计数器中,每次时钟信号的上升沿都会使电路状态发生转换,D触发器输出的值会根据其输入值更新。由于D触发器的输出连接到下一个D触发器的输入,因此电路的状态会按照一个预定义的序列在不同的触发器之间进行移动,产生一系列的输出模式。

### 2.2 扭环形计数器的类型与特点

#### 2.2.1 同步与异步计数器的比较

扭环形计数器通常可以被分为同步和异步两种类型。同步计数器与异步计数器的区别在于触发器的状态转换是否同时发生。

- **同步计数器**:在同步计数器中,所有的触发器都会在相同的时钟信号边沿同时进行状态转换。这使得同步计数器有很好的时序特性,但是随着计数器位数的增加,负载增加会导致时钟偏斜问题。

- **异步计数器**:异步计数器的触发器并不需要等待前面的触发器,因此每个触发器的状态转换时间略有不同。异步计数器的响应速度通常较慢,且设计复杂度高。

扭环形计数器多数情况下指的是同步扭环形计数器,因为异步扭环形计数器的实现与常规的扭环形计数器差别较大。

#### 2.2.2 常见扭环形计数器的种类

扭环形计数器在实现上有很多不同的方式,常见的扭环形计数器包括以下几种:

- **线性反馈移位寄存器(LFSR)**:使用反馈逻辑来改变计数序列,具有较好的伪随机特性。

- **循环冗余校验(CRC)生成器**:在数据通信中用于错误检测。

- **伪随机二进制序列(PRBS)生成器**:常用于测试和通信系统。

每种扭环形计数器的设计都有其独特的特点和用途。例如,LFSR可以提供长周期的重复序列,而CRC生成器则更注重于检错能力。

### 2.3 扭环形计数器的性能分析

#### 2.3.1 时序分析与优化基础

扭环形计数器的性能分析通常涉及以下几个方面:

- **时钟偏斜(Clock Skew)**:由于在高频率下时钟信号在不同D触发器间的传播速度不同,时钟信号可能在不同触发器间不同步,从而影响计数器的性能。

- **信号完整性(Signal Integrity)**:高速电路设计中,信号之间可能会相互干扰,影响数据的准确性。

- **功耗(Power Consumption)**:随着计数器的频率增加,功耗也会增加,这对于移动设备和低功耗应用来说是一个问题。

为了优化扭环形计数器的性能,可以通过以下方法:

- **调整时钟路径**:通过设计合理的电路布局来减少时钟偏斜。

- **使用差分时钟信号**:以提高信号的抗干扰能力。

- **降低工作频率**:合理选择计数器的工作频率以降低功耗。

#### 2.3.2 性能瓶颈识别与改进策略

扭环形计数器的性能瓶颈通常包括:

- **延迟问题**:D触发器的延迟以及信号的传输延迟可能导致计数器无法在预期的时钟频率下工作。

- **同步问题**:在高频率下,保证所有触发器同步变得困难。

- **功耗和热问题**:高速运行时计数器的功耗增加,可能会导致器件过热。

改进策略可以包括:

- **使用高速触发器**:选择具有更低延迟的D触发器来提高性能。

- **采用预取样技术**:通过预取样减少触发器的延迟。

- **优化散热设计**:使用更好的散热技术,例如散热片或风扇,以减少热量积累。

通过这些策略,可以显著提高扭环形计数器的工作性能和稳定性。

# 3. 扭环形计数器的高级应用技巧

## 3.1 时序优化的实践方法

### 时钟频率与延迟分析

在设计和应用扭环形计数器时,优化时钟频率与减少延迟是提升系统性能的关键。提高时钟频率可以加速计数器的响应速度,但同时也可能增加延迟,影响系统稳定性。在优化过程中,需要对计数器的每一个逻辑门延迟进行细致分析,确保时钟周期内的所有信号都能稳定传递,避免因延迟过长导致的时序违规。

通过实验验证,可以使用硬件描述语言(HDL)如Verilog或VHDL编写测试平台,对计数器的时钟频率进行调整和分析。示例如下:

```verilog

module clock_frequency_test(

input clk, // 输入时钟信号

input reset, // 复位信号

output reg [3:0] count // 4位计数器输出

);

always @(posedge clk or posedge reset) begin

if (reset)

count <= 4'b0000;

else

count <= count + 1;

end

endmodule

```

上述代码段定义了一个简单的时钟频率测试模块,其内部实现了一个4位的上升沿触发计数器。在仿真中逐渐增加时钟频率,观察计数器的计数是否正确,以此来确定合适的时钟频率上限。

### 线路长度与负载均衡的调整

线路长度的优化对于减少信号传播延迟至关重要。通过缩短关键路径上的线路长度,可以显著减少信号传输时间,从而提高整体性能。负载均衡是指在多负载环境中,分配线路负载,使其尽可能均匀,减少单条线路的负载压力。例如,在FPGA中实现扭环形计数器时,可以使用专用的全局时钟网络,以确保时钟信号同步到达各个寄存器。

线路长度的优化可以通过物理布局工具实现,而负载均衡则涉及到信号分布策略的调整。在HDL代码中,设计者应尽量避免在单个信号线上连接过多负载,

0

0