【工作时序与同步】:深入探讨扭环形计数器的时序问题(确保系统稳定运行)

发布时间: 2024-12-28 12:24:40 阅读量: 12 订阅数: 11

基于扭环形计数器设计交通信号灯自动控制电路

# 摘要

扭环形计数器作为一种重要的数字逻辑组件,在时序控制和同步系统设计中扮演着关键角色。本文首先介绍了扭环形计数器的基本概念和工作原理,随后深入探讨了其时序理论基础,包括时钟信号、同步机制、关键时序参数如延迟时间、时钟偏斜和时钟抖动的分析,以及它们在扭环形计数器稳定性中的应用。第三章聚焦于时序实践分析,包括电路布局影响、负载效应分析、时序仿真优化以及调试修正方法。第四章详述了同步策略的原理、性能评估以及在实际应用中的挑战和应对措施。第五章则侧重于高可靠扭环形计数器的设计实践,探讨了系统稳定性指标、硬件冗余和软件算法的作用,并通过案例分析展示了设计要点和反思。最后,在第六章中,本文展望了新技术、集成电路技术进步和行业标准发展对扭环形计数器未来趋势的影响以及对系统稳定性要求的市场预测。

# 关键字

扭环形计数器;时序理论;同步机制;时钟偏斜;高可靠性设计;技术发展趋势

参考资源链接:[扭环形计数器:同步二进制与N进制逻辑详解](https://wenku.csdn.net/doc/5u1ne7av12?spm=1055.2635.3001.10343)

# 1. 扭环形计数器简介与工作原理

## 扭环形计数器简介

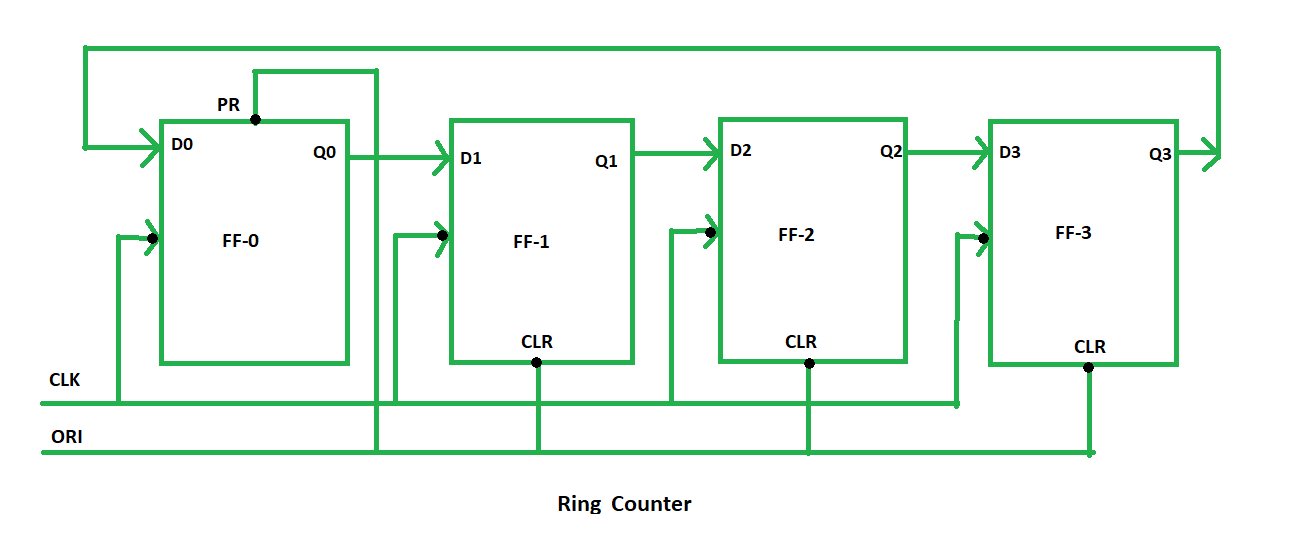

扭环形计数器是一种数字计数设备,广泛应用于电子系统中,特别是在需要环形结构进行数据处理的场合。它通过特定的环形电路设计,使得数字信号能够在一个闭合的环路中循环传递和变换状态。这种计数器的结构简洁,性能稳定,易于实现多级串联,是数字电路中的重要组成部分。

## 扭环形计数器的工作原理

工作原理上,扭环形计数器利用了一组触发器(通常是JK触发器或D触发器),这些触发器通过特定的反馈网络连接起来形成一个环形结构。每个触发器的输出端连接到下一个触发器的输入端,形成一个循环链。在时钟信号的驱动下,信号在环内按预定的顺序依次移动或翻转状态,实现计数功能。

具体来说,计数器的状态变化通常由外部时钟信号控制,每个时钟脉冲推动数据向下一个节点移动一位,从而实现循环计数。触发器的状态变化还可能受到进位信号的影响,以实现更复杂的计数模式,比如二进制计数、模n计数等。例如,在二进制计数模式下,随着每个时钟脉冲的到来,环中的位会按照2的幂次方顺序改变状态,产生0、1、2、3等计数值。

# 2. 扭环形计数器的时序理论基础

扭环形计数器是一种利用环形结构来实现计数的逻辑电路。其运作原理是通过将数据位在环形路径上进行循环移动来实现计数功能。在设计和实现这样的计数器时,理解和应用时序理论至关重要。时序理论为设计者提供了确保电路稳定性的工具和技术,通过控制和优化时钟信号和数据路径来减少错误和提高性能。本章节将深入探讨时序理论的基础知识,并分析其在扭环形计数器设计中的应用。

### 2.1 时钟信号与同步机制

#### 2.1.1 时钟信号的定义和作用

时钟信号是电子系统中的关键信号,它提供了一个周期性的时序参考,用于同步电路中的各种操作。在一个扭环形计数器中,时钟信号控制着数据位移动的时刻,确保每个位都能够在正确的时间到达下一个节点。时钟信号的准确性和稳定性直接影响计数器的可靠性和性能。一个理想的时钟信号拥有严格的周期性,且上升沿和下降沿都足够陡峭,以便于电路能够清晰地识别信号的变化。

#### 2.1.2 同步技术的分类及其应用场景

同步技术可以分为两大类:同步电路和异步电路。同步电路是指所有操作都由统一的时钟信号驱动,而异步电路则没有统一的时钟信号,各部分之间通过握手协议来实现同步。在扭环形计数器的设计中,同步技术的选择取决于具体的应用需求和电路复杂度。同步电路因其简单和易于分析的优势,在许多情况下成为首选。然而,对于需要低延迟和高吞吐量的应用,异步电路提供了更好的性能。

### 2.2 时序分析的关键参数

#### 2.2.1 延迟时间(Propagation Delay)

延迟时间是信号在电路中传播的时间。在扭环形计数器中,延迟时间是关键因素,它决定了数据位从一个触发器移动到下一个触发器所需要的时间。如果延迟时间过长,可能会导致数据位到达下一节点时的时钟边沿已经过去,从而产生计数错误。因此,在设计时必须仔细考虑延迟时间,并通过优化电路布局或使用高速元件来减少延迟。

```mermaid

graph TD

A[数据位进入计数器] --> B[延迟时间分析]

B --> C{延迟时间是否合适?}

C -->|是| D[信号正确到达下一个触发器]

C -->|否| E[调整电路布局或元件]

E --> B

```

#### 2.2.2 时钟偏斜(Clock Skew)

时钟偏斜是指在同一个时钟域内,由于路径长度不同或者电路不均匀造成的时钟信号到达不同触发器的时间差异。在扭环形计数器中,时钟偏斜可能导致触发器之间数据传输的时序问题。为了减小时钟偏斜,设计者需要尽可能保证时钟路径的对称性和均匀性,并采用适当的时钟树综合技术。

#### 2.2.3 时钟抖动(Clock Jitter)

时钟抖动是指时钟信号周期的时间不一致,表现为周期的随机波动。时钟抖动会增加信号的不确定性,可能会导致数据位的捕获不稳定。通过使用高质量的时钟源、避免噪声干扰以及使用时钟滤波和稳定技术,可以有效降低时钟抖动的影响。

### 2.3 时序理论在扭环形计数器中的应用

#### 2.3.1 时序理论对计数器稳定性的影响

时序理论通过对延迟时间、时钟偏斜和时钟抖动等关键参数的精确控制,确保了扭环形计数器的稳定运行。稳定性意味着计数器可以准确地在每个时钟周期内正确地移动和更新数据位。为了达到这一目标,设计者需要进行严格的时序分析和仿真,以及在必要时使用时序约束来保证性能。

#### 2.3.2 设计时序约束以确保扭环形计数器的稳定性

设计时序约束是确保电路稳定运行的重要步骤。时序约束通常包括设置合理的时钟周期、建立时间(setup time)和保持时间(hold time)等参数。在扭环形计数器中,这些约束确保了数据位在正确的时刻被捕获,并在下一个时钟周期到来之前保持稳定。通过约束管理工具,如EDA(电子设计自动化)软件,设计者可以在电路设计的不同阶段进行时序检查和优化。

# 3. 扭环形计数器的时序实践分析

扭环形计数器作为数字电路中的一种重要组件,其时序性能直接关系到整个系统的稳定性和可靠性。第三章我们将深入探讨扭环形计数器在实际应用中遇到的时序问题,时序仿真的应用以及调试和修正时序问题的方法。

## 3.1 实际电路中的时序问题

### 3.1.1 电路布局对时序的影响

在设计扭环形计数器时,电路布局(Layout)对于时序影响至关重要。电路布局决定了信号的传输路径长度,从而直接影响信号的传输延迟。为了确保信号能够在预定时间内到

0

0