【信号完整性问题分析】:PIN_delay设置不当导致的常见故障及快速解决方案

发布时间: 2024-11-29 01:49:43 阅读量: 131 订阅数: 28

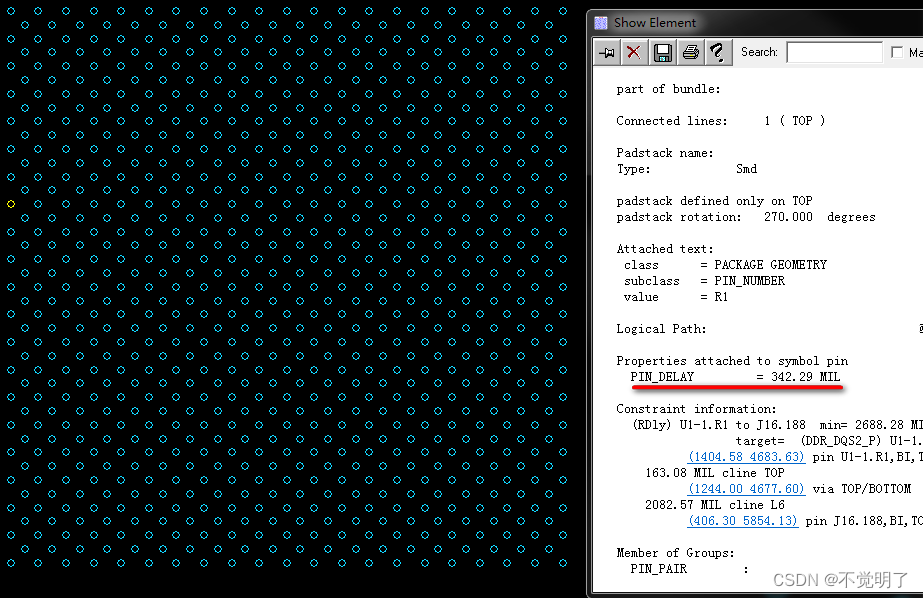

导入PIN DELAY 的方法

参考资源链接:[Allegro添加PIN_delay至高速信号的详细教程](https://wenku.csdn.net/doc/6412b6c8be7fbd1778d47f6b?spm=1055.2635.3001.10343)

# 1. 信号完整性问题概述

## 1.1 信号完整性基础

在高速数字电路设计中,信号完整性(Signal Integrity,简称SI)是确保信号在电路板上准确无误传输的关键因素。任何与原始信号相比出现的失真都可视为信号完整性问题,包括过冲、下冲、振铃、串扰和电源/地噪声等现象。

## 1.2 信号完整性问题的影响

信号完整性问题会直接影响到数字系统的性能,可能导致数据传输错误,降低系统稳定性,甚至在极端情况下导致系统完全无法工作。因此,对于高性能的IT和电子设备来说,解决信号完整性问题是设计成功的关键。

## 1.3 信号完整性分析的重要性

分析和解决信号完整性问题不仅可以保证产品的可靠性,还可以减少开发成本和缩短上市时间。这要求工程师深入了解和掌握相关的分析工具和技术,以便在设计阶段就预测并消除潜在问题。

# 2. PIN_delay的作用与重要性

### 2.1 PIN_delay基本概念解析

#### 2.1.1 信号传播与延迟原理

在数字电路中,信号从一个逻辑门传播到另一个逻辑门时,并不是瞬时发生的。信号传播涉及电荷的移动,而电荷的移动受到物理介质和电路布局的限制,存在一定的延迟。这个延迟通常被称为传播延迟(Propagation Delay),即PIN_delay。

传播延迟是指信号在两个点之间传播所需的时间,它与电路中使用的材料特性、信号路径的长度、走线的几何形状以及负载条件都有关系。PIN_delay的测量通常以纳秒(ns)为单位,而对高速电路设计而言,每一个纳秒都可能对电路性能产生显著影响。

在高速电路中,信号的速度接近于光速,而当电路的传输距离较长时,延迟就会变得非常明显,特别是在时钟频率很高的场合。为了保证数据的正确传输,电路设计必须考虑PIN_delay,并采取措施来控制它。

#### 2.1.2 PIN_delay的定义及其对信号完整性的影响

PIN_delay的定义与信号路径上的所有组件有关,包括逻辑门、互连线路、电阻、电容等。延迟的总和会影响整个电路的响应时间,进而影响到信号完整性(Signal Integrity,简称SI)。如果信号的传播时间超过了时钟周期的一部分,就会导致信号到达逻辑门时产生错误的数据,这称为时序问题。

在信号完整性分析中,PIN_delay被用来确保电路中的所有信号在预定的时间内到达目标位置,以避免数据的失真和同步错误。优化PIN_delay通常意味着找到信号路径上的延迟瓶颈,并通过改变物理布局、调整逻辑门参数或增加缓冲器等手段来缩短延迟时间。

### 2.2 PIN_delay在电路设计中的角色

#### 2.2.1 设计阶段的PIN_delay设置

在电路设计的初步阶段,设计师需要对PIN_delay进行预估和规划。这包括对电路板的布局、信号走线、以及逻辑门的连接进行详细的设计。设计阶段的PIN_delay设置是基于预计的电路参数和已知的物理定律。

对于同步信号(如时钟信号),设计者必须确保在不同的负载下,信号能按时到达每个负载点,这通常通过计算信号在电路中的传输时间来实现。而对于异步信号,则需要通过设计逻辑门的延迟来确保信号之间具有正确的时序关系。

在设计阶段,设计者可以利用先进的电路仿真软件来模拟信号在实际电路中的传播,从而调整设计以达到预期的PIN_delay。电路仿真工具提供了参数化的模型,能够模拟不同环境下的信号传播情况,帮助设计者预测和优化信号完整性问题。

#### 2.2.2 不同信号路径的PIN_delay考量

在电路设计中,不是所有的信号路径都同等重要。关键路径(Critical Path)是电路中决定系统性能和时序的路径,其上的PIN_delay尤其需要精细控制。由于信号的延迟会受到负载、信号频率和传输介质的影响,因此关键路径上的PIN_delay必须仔细设计以避免性能瓶颈。

为了管理不同信号路径的延迟,电路设计者通常会应用各种延迟平衡技术。例如,可以在较短的路径上添加额外的负载,或者在较长的路径上使用具有更短延迟的组件,以确保所有路径的PIN_delay匹配,从而提高整体电路的时序容限。

电路设计者还必须在设计中预留一定的延迟余量,以适应电路在实际操作过程中由于温度变化、电压波动或制造差异等原因引起的延迟变化。只有通过严格的PIN_delay分析和控制,才能确保信号完整性,减少电路故障的可能性。

在下一章节,

0

0