【Allegro性能提升】:PIN_delay调优对高速接口性能的影响,性能飞跃

发布时间: 2024-11-29 02:30:13 阅读量: 18 订阅数: 38

参考资源链接:[Allegro添加PIN_delay至高速信号的详细教程](https://wenku.csdn.net/doc/6412b6c8be7fbd1778d47f6b?spm=1055.2635.3001.10343)

# 1. PIN_delay与高速接口性能基础

在现代IT系统中,随着数据传输速率的不断提高,高速接口的设计与优化变得日益重要。本章将探讨高速接口设计的核心概念之一:PIN_delay(引脚延迟),以及其对整体系统性能的影响。

## PIN_delay参数解读与分析

### 2.1 PIN_delay的定义和作用

PIN_delay是指信号在传输路径上从源到目的地的传播时间。它在高速接口设计中起着至关重要的作用,因为随着数据速率的提升,信号的传播延迟成为限制系统性能的重要因素。

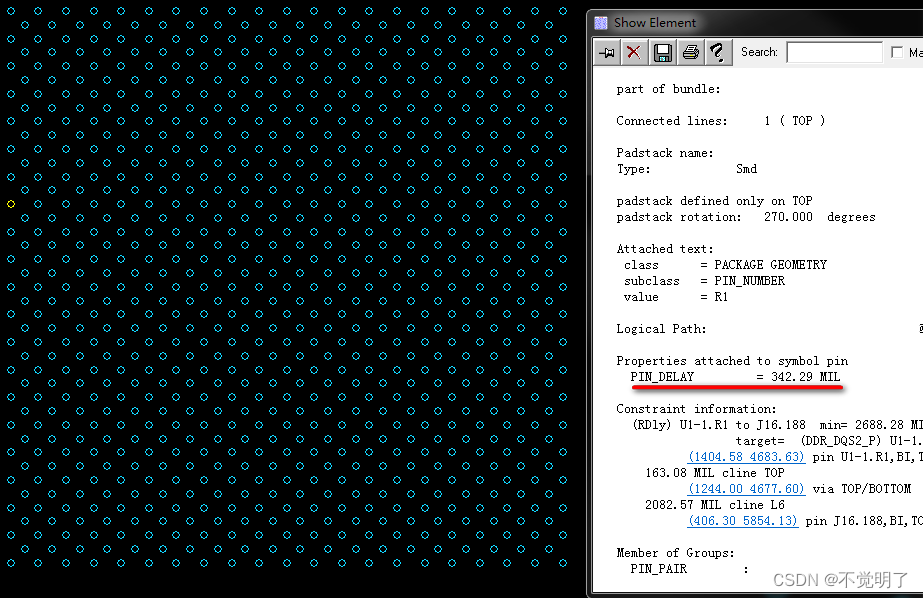

### 2.2 PIN_delay的测量与评估

准确测量和评估PIN_delay对于保证系统可靠性至关重要。本节将介绍测量PIN_delay的现场技术、工具,以及如何从收集的数据中得出性能评估。

```mermaid

graph LR

A[开始] --> B[测量PIN_delay]

B --> C[数据采集]

C --> D[数据分析]

D --> E[性能评估]

E --> F[结束]

```

在下一章节中,我们将深入探讨PIN_delay的理论极限,以及如何在实际应用中计算和优化这个参数。

# 2. PIN_delay参数解读与分析

## 2.1 PIN_delay的定义和作用

### 2.1.1 参数在高速通信中的角色

PIN_delay,即输入/输出延迟,是高速接口设计和分析中的一个关键参数。它描述了在输入或输出操作中,信号从一个时钟域传递到另一个时钟域时所需的时间延迟。在集成电路、计算机网络、存储设备和高速通信系统中,PIN_delay对于确保数据同步、降低误码率以及提升整体系统性能至关重要。

在实际高速通信系统中,信号在传输过程中的延迟不仅受到物理介质的影响,还受到电路设计、集成电路制造工艺和接口技术等因素的共同作用。延迟的存在会导致信号失真、通信效率下降、甚至引起系统不稳定等问题。因此,深入理解PIN_delay,分析其产生的原因和影响,是优化高速接口性能不可或缺的一步。

### 2.1.2 PIN_delay的理论极限与计算

PIN_delay的理论极限受到物理和电气限制的制约,例如介质的电磁特性、电路元件的开关速度等。在理论上,PIN_delay可以通过公式进行计算:

```

PIN_delay = T_prop + T_setup + T_hold

```

其中:

- `T_prop` 表示信号在介质中传播的时间。

- `T_setup` 表示信号在目标时钟域中达到有效状态所需的建立时间。

- `T_hold` 表示信号在目标时钟域中保持有效状态的保持时间。

而在实际的高速通信系统中,PIN_delay的计算还需要考虑到电路板的布局布线、电气特性、负载特性等多种因素。为了得到准确的PIN_delay值,通常需要结合仿真工具进行模拟分析,或者通过专业的测量设备进行现场测试。

## 2.2 PIN_delay的测量与评估

### 2.2.1 现场测量技术与工具

为了精确测量PIN_delay,通常需要使用先进的测量技术与工具,包括但不限于:

1. **时域反射计(TDR)**:TDR通过发送脉冲并测量其反射的时间,从而确定信号传播路径的阻抗不连续性和延迟。

2. **高精度示波器**:配合特定的探头和夹具,高精度示波器能够捕获和分析高速信号的变化,准确测量信号的上升沿和下降沿时间。

3. **矢量网络分析仪(VNA)**:VNA测量信号在特定频率范围内的幅度和相位,可以用于评估介质特性对PIN_delay的影响。

这些工具能够提供详尽的数据分析,为工程师提供PIN_delay的实际测量值,以及进行后续的系统性能评估。

### 2.2.2 数据分析和性能评估方法

测量得到的数据通常需要经过一系列的处理和分析,才能用于性能评估。数据分析的方法主要包括:

1. **时域分析**:通过TDR和示波器得到的时域信号可以直接反映出信号延迟的情况。

2. **频域分析**:VNA测得的频域响应可以转换为时域响应,从而分析信号在传输过程中的延迟特性。

性能评估方法则可能包括:

- **信号完整性分析**:分析信号在不同条件下是否能保持其完整性,例如通过检查信号的抖动、噪声以及电磁干扰等参数。

- **误码率测试(BERT)**:评估在实际通信条件下,数据传输的准确性,从而间接评估PIN_delay对通信性能的影响。

通过这些数据分析和性能评估方法,工程师可以获取PIN_delay的准确数值,并且对系统的通信性能进行全面的了解,为进一步的调优提供依据。

# 3. PIN_delay调优实践

## 3.1 调优策略与方法论

### 3.1.1 PIN_delay调优的理论依据

在高速接口的设计和实现中,PIN_delay是决定信号完整性和性能的关键参数之一。调优策略必须基于对高速数字系统中信号传输延迟的深刻理解,以及对延迟、信号质量和系统性能之间关系的充分考

0

0