【PIN_delay调校策略】:优化Allegro设计的信号路径延迟,提升性能的秘诀

发布时间: 2024-11-29 02:19:07 阅读量: 34 订阅数: 38

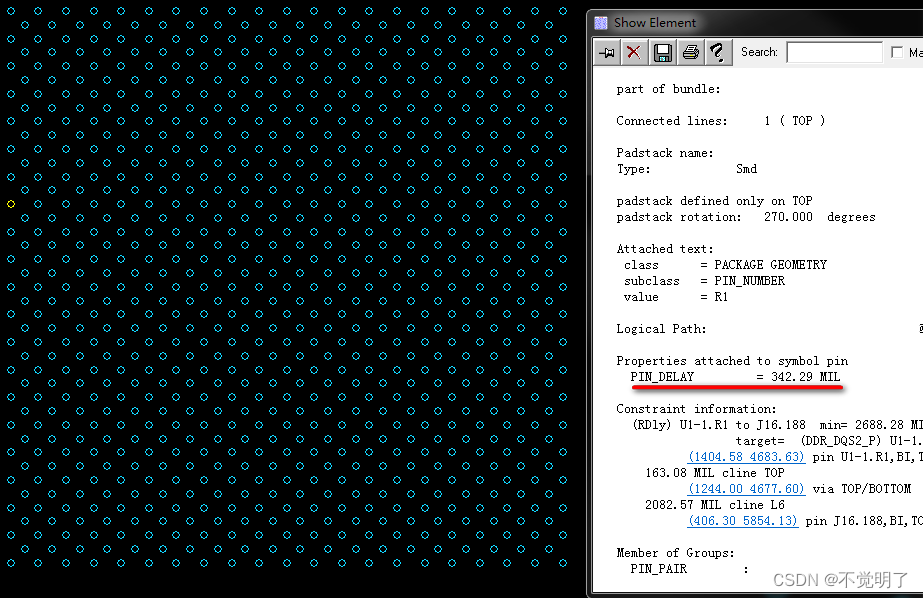

allegro高速信号添加PIN_delay的详细步骤

参考资源链接:[Allegro添加PIN_delay至高速信号的详细教程](https://wenku.csdn.net/doc/6412b6c8be7fbd1778d47f6b?spm=1055.2635.3001.10343)

# 1. PIN_delay调校策略概述

在高速电路设计中,**PIN_delay**是确保信号完整性和系统性能的关键因素之一。本章节旨在为读者提供一个对PIN_delay调校策略的全面概述,内容将涉及调校的目的、重要性和基本方法。通过对PIN_delay的理解和优化,工程师能够有效减少信号在传输路径中的延迟,从而提高整体电路的性能。

## 1.1 PIN_delay调校的重要性

PIN_delay直接关联到电路板上特定引脚的信号延迟时间。在高速电路设计中,延迟的控制对于避免信号失真、保持数据完整性至关重要。一个精确的调校流程能够确保电路在预期的工作频率下稳定运行,这对于高性能计算和通信系统尤其重要。

## 1.2 基本调校方法

基本的PIN_delay调校方法通常包括参数调整、仿真测试和实际硬件验证。调整可以通过修改设计参数来完成,包括走线长度、过孔数量和位置等。接下来,利用专业软件进行仿真测试,观察信号质量并做出必要的优化。最后,通过制作原型板并进行实际测试来验证调校效果。

通过这一系列步骤,可以确保信号路径延迟被精确控制,从而满足设计要求和性能标准。接下来的章节将深入探讨信号路径延迟的理论基础,为深入理解调校策略提供支持。

# 2. 信号路径延迟的理论基础

### 2.1 信号传输延迟的原理

在电子系统中,信号传输延迟是指信号从一点传播到另一点所需的时间。在高速电子电路设计中,这个时间的长短直接影响到系统的性能。

#### 2.1.1 电磁波在介质中的传播

电磁波在介质中的传播速度是有限的,它取决于介质的介电常数。信号沿传输线传播时,由于电磁波的传播速度低于光速,因此存在延迟。这个延迟可以通过以下公式近似计算:

\[ t_{delay} = \frac{L \sqrt{\varepsilon_{r}}}{c} \]

其中,\( L \) 是信号传输路径的长度,\( \varepsilon_{r} \) 是介质的相对介电常数,\( c \) 是光速。

#### 2.1.2 传输线理论简介

传输线理论是研究在传输线上传播的电磁波的科学。在传输线上,信号的传播不仅仅依赖于导体,也涉及到周围介质的电磁特性。阻抗匹配是传输线理论中的一个核心概念,它能够确保信号能量的最大化传输和最小化反射。

### 2.2 延迟的影响因素分析

信号路径延迟不仅受到传输介质的电磁特性的影响,还与电路工作环境密切相关。

#### 2.2.1 材料和介质的特性

不同材料的电磁特性差异会导致信号在不同介质中的传播速度不同。介电常数、磁导率和损耗因子是影响信号延迟的关键材料参数。

#### 2.2.2 温度和电压波动的影响

温度的升高通常会导致介质介电常数的增加,进而导致信号传播速度的下降,延迟增大。电压波动可以通过影响介质参数间接影响信号延迟。

### 2.3 PIN_delay在信号路径中的作用

在高速数字电路设计中,了解和控制信号路径上的延迟是至关重要的,而PIN_delay是一种调节信号路径延迟的有效方法。

#### 2.3.1 PIN_delay的定义和功能

PIN_delay是指特定的电子元件(如连接器、插座或IC引脚)引入的固有延迟时间。此延迟时间会直接影响信号的传输速度。

#### 2.3.2 与信号完整性(SI)的关系

信号完整性关注的是信号在传输路径中保持其原始质量的能力,而PIN_delay是影响信号完整性的重要因素之一。通过对PIN_delay的调节,可以优化信号波形,减少信号失真。

```mermaid

graph LR

A[开始] --> B[设计高速电路]

B --> C[分析PIN_delay影响]

C --> D[调节PIN_delay]

D --> E[模拟测试信号完整性]

E --> F[优化设计]

F --> G[实际布线]

G --> H[测试实物性能]

H --> I{性能是否满足要求}

I -->|是| J[结束]

I -->|否| C[回到分析PIN_delay影响]

```

以上流程图展示了PIN_delay在信号路径中的调校过程。从设计高速电路开始,通过分析PIN_delay对信号完整性的影响,进而调节PIN_delay,模拟测试信号完整性并进行优化。经过一系列测试和调整后,电路设计进入实际布线阶段,最终测试实物性能,如果性能满足要求,则设计完成。如果性能不满足要求,则需回到分析PIN_delay影响的阶段进行进一步调校。

# 3. Allegro设计中的PIN_delay调校技巧

## 3.1 Allegro设计环境概述

### 3.1.1 设计流程和关键步骤

在设计印刷电路板(PCB)时,使用Allegro这类设计软件已成为业界标准。Allegro PCB Designer是由Cadence公司开发的一款专业的PCB设计工具,它提供了一个全面的环境,用于进行从概念设计到制造输出的整个流程。在这一流程中,PIN_delay调校是确保信号完整性的重要步骤之一。

以下是Allegro设计流

0

0