【缓存与内存层次结构】:2路组相联Cache的定位与优化

发布时间: 2024-12-26 05:58:52 阅读量: 14 订阅数: 14

白色宽屏风格的芭蕾舞蹈表演企业网站模板.rar

# 摘要

缓存是提高计算机系统性能的关键技术之一,尤其在现代处理器架构中,Cache的设计和优化对于整体性能有着决定性的影响。本文首先概述了缓存与内存层次结构的基本概念,详细介绍了Cache的工作原理和数据定位机制,以及不同Cache结构的性能特点。文章深入分析了2路组相联Cache的内部结构和性能优势,并探讨了优化策略,包括数据放置、预取策略、替换算法、映射函数设计原理及缓存一致性协议。通过案例分析,本文展现了2路组相联Cache在现代处理器中的应用,并讨论了实际优化实践中的挑战与解决方案。最后,文章展望了未来的研究方向,包括新型Cache技术的潜在进步和内存层次结构的改进路径。

# 关键字

缓存;内存层次结构;Cache性能;2路组相联Cache;优化策略;缓存一致性

参考资源链接:[头歌计算机组成原理:2路组相联Cache设计详解](https://wenku.csdn.net/doc/33n6jjkxyg?spm=1055.2635.3001.10343)

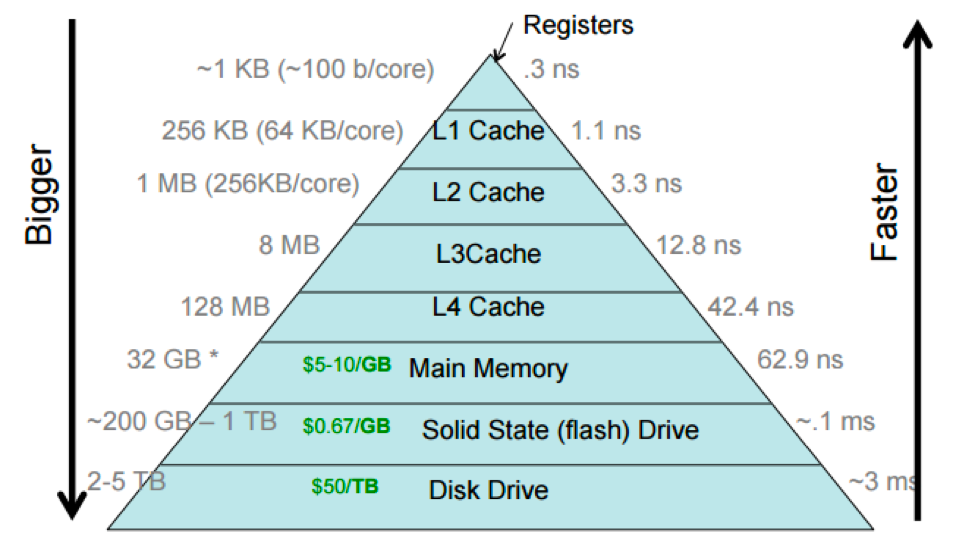

# 1. 缓存与内存层次结构概述

在当今的信息时代,内存层次结构已成为现代计算机架构设计中的核心组件之一。缓存(Cache)作为其中最快速的存储层次,扮演着至关重要的角色。它能够显著提高数据访问速度,减少处理器因等待数据从主内存传输而造成的空闲时间。本章将为您概述缓存的基本概念,以及它如何融入内存层次结构中,为之后章节深入探讨各类Cache的工作原理和技术细节奠定基础。

# 2. Cache的工作原理与数据定位

### 2.1 Cache的基本概念和结构

#### 2.1.1 Cache的定义和重要性

在现代计算机系统中,Cache是至关重要的组件,它是CPU与内存之间的一种小容量、高速缓冲存储器。由于处理器速度和内存访问速度之间存在显著差异,Cache的作用是减少这种速度差异带来的性能影响,通过存储最频繁访问的数据以提供快速的数据访问。Cache通过利用局部性原理,即程序倾向于重复访问最近访问过的数据和地址附近的区域,从而极大提升了处理速度和效率。

#### 2.1.2 Cache的层次结构

Cache通常存在于多级缓存层次结构中,包括一级缓存(L1 Cache)、二级缓存(L2 Cache)和三级缓存(L3 Cache)。L1 Cache通常与CPU核心集成,具有最小的容量,但访问速度最快。L2 Cache容量较L1大,速度稍慢,而L3 Cache通常更大容量,速度更慢,但覆盖范围更广,可以缓存更多的数据供CPU核心群组访问。

### 2.2 Cache的数据定位机制

#### 2.2.1 直接映射Cache的数据定位

直接映射Cache(Direct-Mapped Cache)中,主内存被分为大小相同的块,每个内存块只能映射到Cache的一个特定位置。这种机制简化了Cache的管理,但也导致了较高的冲突失效率。在这种设计中,每个内存地址通过位运算直接映射到Cache中的一个确定位置,如果多个内存块都映射到同一个Cache行,则会导致冲突替换。

```mermaid

flowchart LR

A[内存地址] -->|计算索引| B[Cache索引]

B -->|映射| C[Cache行]

D[主内存块] -->|映射| C

```

#### 2.2.2 组相联Cache的数据定位

组相联Cache(Set-Associative Cache)是对直接映射和全相联(Fully Associative Cache)的一种折中方案。在这种机制中,Cache被分成多个组,每个组由多个行组成。每个内存块可以映射到一个特定组中的任意一行,这样就降低了冲突失效率。组相联Cache的组织通常用组数和每组行数来描述,如2路组相联、4路组相联等。

#### 2.2.3 全相联Cache的数据定位

全相联Cache(Fully Associative Cache)允许每个内存块映射到Cache中的任意位置。这种设计提供了最大的灵活性,理论上具有最低的冲突失效率,但是增加了查找数据位置的复杂度和成本。通常用一个内容寻址存储器(CAM)来实现地址查找,这使得全相联Cache在实现上更为复杂。

### 2.3 Cache性能分析

#### 2.3.1 命中率和失效率

Cache的命中率是衡量Cache性能的关键指标之一,指请求的内存数据在Cache中找到的比率。命中率越高,意味着CPU访问Cache的成功率越高,CPU等待内存数据的时间越短。失效率是指无法在Cache中找到请求数据的比率,与命中率互补,失效率越低越好。

#### 2.3.2 命中时间的影响因素

Cache的命中时间受多种因素影响,包括Cache的组织结构、内存块大小、替换策略以及Cache的大小等。结构越复杂,命中时间越长;内存块越大,数据局部性可能越好,但增大了每次访问的数据量。替换策略决定了在Cache满时哪个数据块被替换出去,不同的替换策略会导致不同的命中率。Cache的大小直接影响到它能存储多少数据,较大的Cache通常能提高命中率,但也会增加成本和设计复杂度。

# 3. 2路组相联Cache的内部结构与特性

## 3.1 2路组相联Cache的结构分析

### 3.1.1 组相联Cache的组成单元

组相联Cache的结构是一种介于直接映射Cache和全相联Cache之间的缓存结构。这种结构尝试平衡了两者之间的利弊,通过将Cache分割成多个组,并在每个组内采用相联的方式存储数据。在2路组相联Cache中,每个组包含了两个Cache行,每行可以存储一个数据块。

与直接映射Cache相比,组相联Cache通过增加组内相联度,减少了数据块的冲突失效概率,因为一个特定的主存块可以在一个组内的两个行中任选一个存储。这提供了更灵活的数据存储方式,但同时也带来了更高的硬件复杂度和成本。

### 3.1.2 行替换策略和标记存储

在组相联Cache中,每个组都包含多个行,而行替换策略决定当发生缓存缺失时,哪个行将被新的数据块替换。最常见

0

0