硬件工程师必读:2路组相联Cache设计的关键考量与实践

摘要

本论文深入探讨了Cache的基本知识、工作原理,特别是2路组相联Cache的理论框架和设计实践。在基础理论部分,本文详细解释了Cache的结构、分类以及不同映射技术的基本原理。第二章则专门分析了2路组相联Cache的关键参数,包括地址映射算法和替换策略,以及它们对性能的具体影响。在设计实践章节,本论文着重于Cache设计工具的选择、仿真环境搭建以及缓存行替换策略的硬件实现,并提供了性能评估和优化策略。随后,本论文探讨了2路组相联Cache在多级缓存架构中的应用,并分析了Cache一致性协议和能耗优化问题。最后,本文展望了未来Cache设计的发展趋势,指出了新型存储技术、多核处理器以及人工智能与大数据处理带来的挑战和机遇。通过系统地阐述,本文为Cache设计和优化提供了全面的理论和实践指导。

关键字

Cache;组相联;地址映射;性能优化;多级缓存;一致性协议

参考资源链接:头歌计算机组成原理:2路组相联Cache设计详解

1. Cache基础知识与工作原理

缓存(Cache)是计算机存储体系中一个关键概念,它在CPU与主存之间扮演着重要的角色。Cache的目的是减少处理器访问主存储器的平均延迟时间。它利用程序的局部性原理,即一个程序在执行过程中,将会频繁地访问一小部分的数据。因此,这些数据和指令被临时存储在Cache中,以便快速访问。

1.1 工作原理概述

Cache的工作基于快速缓存的原理。它采用更小、更快的存储设备来保存最近被处理器访问的数据或指令。当处理器发起一个读取请求时,系统首先会检查该数据是否存在于Cache中。如果存在,就直接从Cache中读取(称为“命中”);如果不存在,则从主存中获取该数据(称为“失效”)并将数据复制到Cache中,以便下次可以快速访问。

1.2 命中率与失效

Cache的性能通常通过命中率来衡量,即处理器在Cache中找到所需数据的次数与总访问次数之比。高命中率意味着处理器需要访问主存的次数较少,这通常可以显著提高整体系统的性能。相反,低命中率则表明需要频繁地访问较慢的主存,这将导致系统性能下降。

Cache的设计和优化工作通常集中在提升命中率和降低访问延迟上。这涉及到缓存行的大小、数量以及映射策略等因素的精细调整。下一章节将探讨2路组相联Cache的理论框架,这是我们优化命中率和访问速度的重要途径。

2. 2路组相联Cache的理论框架

2.1 Cache的结构和分类

2.1.1 Cache的基本组成部分

Cache,即缓存,是计算机体系结构中的一个关键组件,旨在减少处理器与主存储器之间的速度差距。Cache通常由快速的SRAM(静态随机存取存储器)组成,它位于CPU和主内存之间,提供了更快的数据访问速度。

Cache的几个基本组成部分包括:

- 缓存行(Cache Line):这是Cache存储数据的基本单元,通常由几个连续的字节组成。缓存行的大小影响着存储效率和缓存管理的复杂性。

- 标记(Tag):标记用于存储缓存行中数据的地址信息,以便能够快速定位到主内存中的原始数据位置。

- 有效位(Valid Bit):指示缓存行中的数据是否有效。

- 替换状态位(Replacement State Bits):例如在组相联和全相联Cache中,用于记录缓存行的使用情况,帮助实施替换策略。

2.1.2 直接映射、全相联与组相联的比较

Cache根据其映射机制可分为直接映射、全相联和组相联三种类型:

-

直接映射Cache(Direct Mapped Cache):每个主内存块只能被映射到一个特定的缓存行,易于实现,但冲突率较高。

-

全相联Cache(Fully Associative Cache):任何主内存块可以被存储到任何缓存行中,灵活性高,但搜索时间长,实现复杂度高。

-

组相联Cache(Set Associative Cache):结合了直接映射和全相联的优点,将缓存划分为多个组,每个组内有多个缓存行。每个主内存块可以映射到一个特定组中的任意一行,这样既减少了冲突概率,也控制了搜索时间。

2.2 2路组相联Cache的关键参数

2.2.1 行(Block)和组(Set)的概念

在2路组相联Cache中,一个组内含有两个缓存行。数据的映射过程是这样的:CPU发出的数据地址首先被分成三个部分,标记(Tag)、组索引(Set Index)和块偏移(Block Offset)。块偏移用于选择组内的具体字节,组索引用于确定数据应该存储在哪个组中,而标记则用于后续比较,确定该组中哪个缓存行包含了请求的数据。

2.2.2 替换策略与命中率

缓存行的替换策略在组相联Cache中起到至关重要的作用,常用的替换策略有最近最少使用(LRU)和先进先出(FIFO):

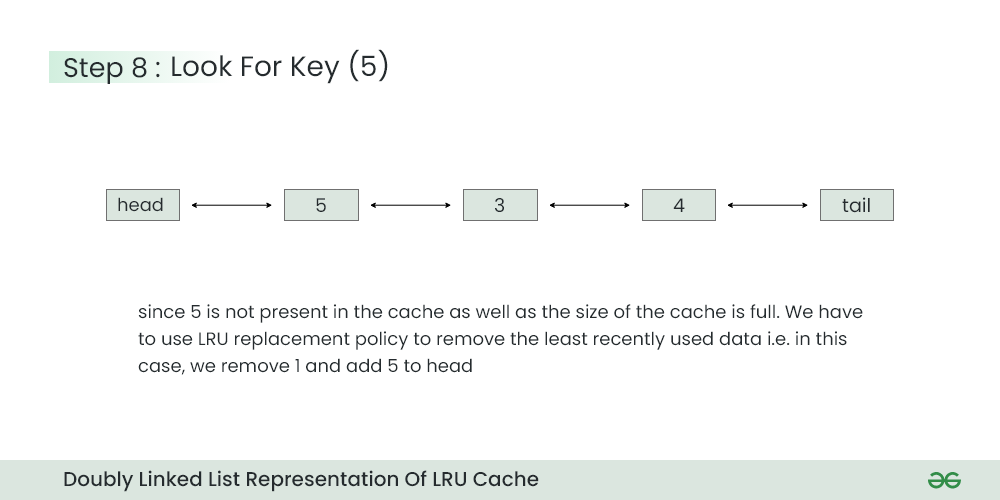

- LRU策略:替换最近最少被访问的缓存行,这个策略假设最近被访问的数据将来被访问的可能性较大。

- FIFO策略:替换最早进入缓存的行,实现起来比较容易,但不总是最高效。

命中率是指CPU访问Cache时,所需数据已经存在于Cache中的比例。合理的替换策略能够提高命中率,减少延迟。

2.2.3 缓存大小对性能的影响

缓存的大小直接影响到性能。一个较大的缓存可以存储更多的数据,从而提高命中率,但同时也可能导致更长的访问时间。Cache大小与访问延迟、成本和功耗之间需要找到一个平衡点。

2.3 2路组相联Cache的地址映射算法

2.3.1 地址映射的基本概念

地址映射是指将主内存地址映射到Cache中的过程。Cache使用地址映射算法将内存中的数据块映射到不同的缓存行,从而实现快速访问。

2.3.2 直接映射和组相联映射的实现

-

直接映射:通过主内存地址中的索引位直接确定缓存行位置,然后比较标签位确定是否命中。

-

组相联映射:每个组有多个缓存行,需要比较组内所有缓存行的标签来确定是否有命中。这里涉及到了更复杂的比较逻辑。

在实际实现中,地址映射算法需要硬件支持,包括地址译码器和比较器等。

接下来的章节将会具体介绍Cache设计实践,包括使用模拟工具和硬件描述语言进行Cache设计和仿真的步骤,以及缓存行替换策略和性能优化的具体实施方法。

3. 2路组相联Cache设计实践

3.1 Cache设计工具和仿真环境

在设计2路组相联Cache时,选择合适的工具和搭建一个高效的仿真环境是至关重要的。设计工具不仅能够