【STM32F429项目加速秘诀】:外扩SDRAM在大型应用中的优化实践

发布时间: 2024-12-19 19:42:04 阅读量: 4 订阅数: 8

# 摘要

本文旨在深入探讨STM32F429项目中如何利用外扩SDRAM技术实现性能加速。首先介绍SDRAM的基础知识,包括其工作原理和与STM32F429的接口技术。随后,分析硬件连接要点及初始化配置,强调硬件设计和电路布局对信号完整性的影响。在性能优化方面,文章详细讨论了缓存机制、动态内存管理以及高速数据处理技巧,并通过案例分析展示在图像处理、实时数据记录和音频流处理中如何应用这些优化技术。最后,文章提供了在编程实践中调试和性能分析的方法,并展望了高级SDRAM技术及其在STM32F429性能扩展中的未来应用方向。

# 关键字

STM32F429;SDRAM;硬件连接;性能优化;缓存机制;动态内存管理;信号完整性;调试工具;性能分析;技术展望

参考资源链接:[STM32F429外扩SDRAM编程入门与常见错误排查](https://wenku.csdn.net/doc/646db6e3543f844488d7f35e?spm=1055.2635.3001.10343)

# 1. STM32F429项目加速概述

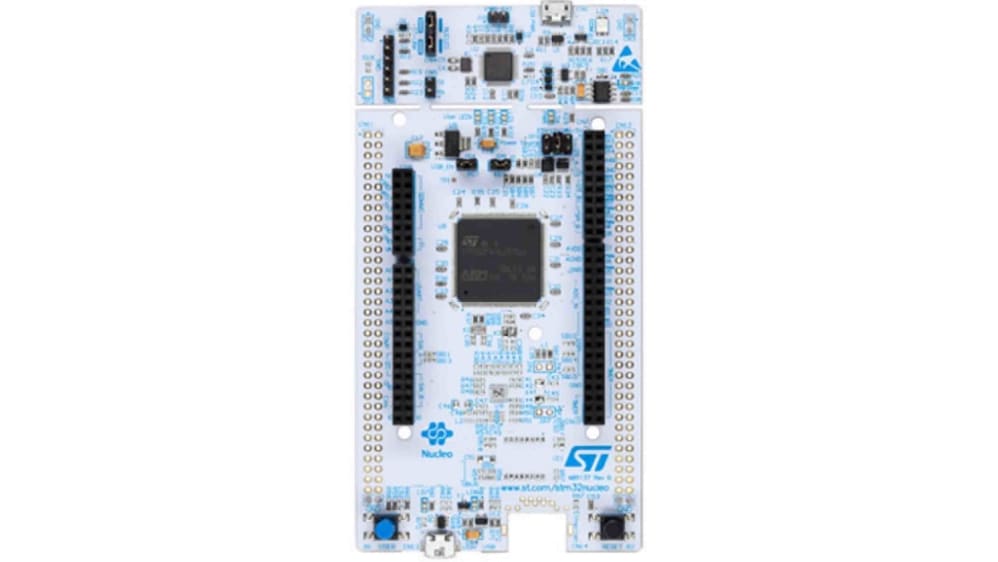

在本章中,我们将开启对STM32F429项目加速之旅的序幕。STM32F429微控制器因其强大的性能和丰富的外设成为嵌入式开发的热门选择。为了进一步提升性能,特别是在处理大型数据集和复杂算法时,扩展SDRAM存储器成为提高系统响应速度和处理能力的关键。

## 1.1 项目加速的重要性

在现代嵌入式系统设计中,能够快速有效地处理数据至关重要。随着应用的复杂性增加,内置RAM的容量往往无法满足所有需求,这就需要外扩SDRAM以增加可访问的存储空间。这不仅可以加速数据读写过程,还能通过缓存机制提高CPU利用率和系统整体性能。

## 1.2 STM32F429的性能优势

STM32F429作为高性能的Cortex-M4核心微控制器,其内部集成了FSMC(Flexible Static Memory Controller),为外扩存储器提供了便利。通过正确配置FSMC以及细致的时序调整,STM32F429能够以接近处理器内部速度运行外部SDRAM,显著提升了运行速度和数据吞吐量。

## 1.3 本章总结

在本章中,我们介绍了项目加速的重要性和STM32F429微控制器的优势。这为接下来章节中对外扩SDRAM技术的深入探索和实践案例分析奠定了基础,敬请期待后续内容,我们将一起深入探讨如何实现STM32F429项目的高效加速。

# 2. 外扩SDRAM技术基础

### 2.1 SDRAM的工作原理

#### 2.1.1 SDRAM的内部结构和工作模式

同步动态随机存取存储器(SDRAM)是基于时钟信号同步的DRAM,能够在时钟的上升沿或下降沿进行数据传输,相比传统的异步DRAM有更高的性能。SDRAM的内部结构由存储阵列、地址寄存器、数据寄存器、列地址缓冲区、行地址缓冲区、控制逻辑和时钟信号管理等部分组成。存储阵列是SDRAM的核心部分,由大量的存储单元构成,每一个存储单元可以存储一个比特的数据。

工作模式方面,SDRAM支持多种命令,例如自动刷新(Auto Refresh)、自刷新(Self Refresh)、预充电(Precharge)和激活(Active)等。这些命令共同工作来实现数据的读取和写入。预充电命令用来关闭打开的行并准备读写新的行,激活命令用来打开特定的行以准备读写操作。读写操作完成之后,通常需要一个预充电命令来关闭行。

```mermaid

graph TD

A[SDRAM开始] --> B[执行预充电]

B --> C[激活行]

C --> D[读取或写入数据]

D --> E[结束本次操作]

E --> F[判断是否需要进行下一次读写]

F -- 是 --> C

F -- 否 --> G[执行预充电]

G --> H[进入自刷新模式或断电]

```

#### 2.1.2 SDRAM与STM32F429的接口技术

STM32F429使用灵活的静态存储控制器(FSMC)来支持外部存储器的接口。FSMC支持NOR Flash、PSRAM、SDRAM、NAND Flash等类型的存储器。对于SDRAM,FSMC通过特定的接口协议来控制SDRAM的操作,包括数据、地址、控制信号和时序的管理。

SDRAM与STM32F429接口时,数据总线、地址总线和控制信号线的连接是必需的。数据总线宽度影响了数据传输的速率,而地址总线则决定了SDRAM的最大容量。控制信号线包括读写控制信号、片选信号、时钟信号、刷新信号等。FSMC通过这些信号线来控制SDRAM的状态,从而实现数据的准确读写。

### 2.2 外扩SDRAM的硬件连接

#### 2.2.1 硬件设计注意事项

在设计STM32F429与SDRAM的硬件连接时,有几个关键的设计事项需要注意:

1. 电源管理:SDRAM需要稳定的电源和地线连接。布局时应尽量缩短电源线和地线的长度,以降低电源噪声的影响。

2. 信号完整性:SDRAM工作频率较高,因此在电路板布局时,要尽量减少信号走线的长度和分支,确保信号完整性和时序的一致性。

3. 去耦电容:SDRAM的电源引脚旁边需要放置适当的去耦电容,以滤除供电噪声,提高电源稳定性。

#### 2.2.2 电路板布局和信号完整性分析

电路板布局对SDRAM的性能有着决定性的影响。在布局时应遵循以下原则:

- 遵循SDRAM厂家提供的布局指南,以确保信号时序和电源稳定性。

- 将SDRAM模块放置在尽可能靠近处理器的位置,以减少走线长度和信号传播延迟。

- 将高速信号线(例如数据线和时钟线)与其他低速控制信号线隔开,以减少干扰。

- 使用差分信号线来传输时钟信号,以增强信号的抗干扰能力。

- 使用多层板设计,至少需要一个完整的地平面来作为信号回流路径,这样有助于保持信号的完整性。

### 2.3 外扩SDRAM的初始化和配置

#### 2.3.1 STM32F429的FSMC配置方法

STM32F429的FSMC配置需要通过一系列的寄存器操作来完成。下面是一个基本的FSMC配置步骤:

```c

// 使能FSMC和FMC时钟

RCC->AHB3ENR |= RCC_AHB3ENR_FSMCEN;

RCC->AHB3ENR |= RCC_AHB3ENR_FMCEN;

// 配置FSMC为SDRAM模式

FSMC_Bank1->BTCR[FSMC_SDRAM Bank] = FSMC_BCR1_MWID_16b | FSMC_BCR1_MWAIT | ...;

// 选择SDRAM的时序参数,根据SDRAM的实际规格进行设置

FSMC_Bank1->BTCR[FSMC_SDRAM Bank] = (SDRAM_Timing | FSMC_BCR1_CAS | FSMC_BCR1_NB);

// 设置SDRAM刷新计数器

FSMC_Bank1E->SDRTR = SDRAM.RefreshCount;

```

在这段代码中,我们需要根据SDRAM的规格手册选择合适的配置参数。`FSMC_BCR1`寄存器用于配置SDRAM接口的模式和一些控制位,如内存宽度、等待状态、自动预充电等。`SDRTR`寄存器用于设置自动刷新的周期。

#### 2.3.2 SDRAM控制器的时序调整和测试

SDRAM的时序调整对性能至关重要。通常情况下,时序参数包括:

- CAS延迟(Column Address Strobe Latency):从CAS信号发出到数据可读的时间。

- 行周期时间(tRC):两个连续的激活命令之间的最短时间。

- 行预充电时间(tRP):从预充电命令到下一个行激活命令的最短时间。

- 行到行延迟时间(tRRD):从一个行激活命令到下一个行激活命令的最短时间。

在实际使用中,需要通过编写测试程序,对SDRAM执行读写测试,并根据测试结果微调时序参数,以确保最佳的性能和稳定性。这通常需要对SDRAM控制器的初始化代码进行多次迭代优化。

```c

// 以下伪代码用于调整SDRAM时序并进行测试

for (int cas_delay = 2; cas_delay <= 5; ++cas_delay) {

for (int tRC = 10; tRC <= 18; ++tRC) {

// 设置时序参数

SetSDRA

```

0

0