【STM32F429与外扩SDRAM终极优化指南】:新手也能掌握的性能调优秘籍

发布时间: 2024-12-19 18:27:23 阅读量: 7 订阅数: 8

STM32F429使用外扩SDRAM运行程序的方法

# 摘要

本文深入探讨了STM32F429微控制器与外扩SDRAM的结合使用,以实现性能优化。首先介绍了STM32F429的内存架构及SDRAM的技术原理,强调了内存映射、MPU工作原理、SDRAM工作模式及接口协议的重要性。接着详细讨论了外扩SDRAM的硬件配置、调试和优化,包括硬件时序调整、调试工具的运用和编程技巧。第四章深入到软件层面,介绍内存管理和缓存优化的技术细节。最后一章通过综合案例分析,对性能评估工具的应用和优化实践的最佳经验进行了分享,提供了实际项目中内存优化案例的详细分析,并对比优化前后的性能变化。

# 关键字

STM32F429;外扩SDRAM;内存架构;性能优化;硬件调试;软件编程;缓存优化

参考资源链接:[STM32F429外扩SDRAM编程入门与常见错误排查](https://wenku.csdn.net/doc/646db6e3543f844488d7f35e?spm=1055.2635.3001.10343)

# 1. STM32F429与外扩SDRAM基础介绍

## 1.1 STM32F429概述

STM32F429作为ST公司ARM Cortex-M4系列中的一员,具备丰富的外设和高效的处理能力,是嵌入式开发者的常用选择。其高达180 MHz的工作频率,集成了多种通信接口,为复杂应用提供了强大的处理支持。

## 1.2 外扩SDRAM的意义

在许多复杂的应用中,STM32F429内置的RAM资源往往无法满足需求。外扩SDRAM提供了额外的动态存储空间,允许开发者处理更大的数据集,优化内存使用,并提升了系统整体的性能。

## 1.3 连接方式和硬件选择

STM32F429通过其灵活的FSMC(Flexible Static Memory Controller)与外扩SDRAM连接。在选择外扩SDRAM时,需考虑其兼容性和时序要求,确保与STM32F429的顺畅通信。

```c

// 示例代码,展示如何配置FSMC以连接外扩SDRAM

// 该代码为伪代码,仅用于展示概念

void SDRAM_Init() {

// 初始化FSMC外扩接口

FSMC_Bank1->BTCR[SDRAM_BANK] |= SDRAM_CR_CAS | SDRAM_CR_NB;

// 其他必要的配置

}

```

在进行硬件选择和连接时,必须参考STM32F429和SDRAM的技术手册,确定合适的连接引脚和时序参数,确保外扩SDRAM的稳定性和高性能。

# 2. 性能优化的理论基础

## 2.1 STM32F429的内存架构

### 2.1.1 内存映射与地址空间

在现代微控制器设计中,内存映射是将物理地址空间(也称为内存空间)映射到处理器的虚拟地址空间的过程。STM32F429微控制器的内存映射分为几个部分,包括内置的SRAM和Flash,外扩的SDRAM,以及各种外设的寄存器映射。内存映射使得CPU能够通过虚拟地址访问所有的物理资源。

在ARM Cortex-M4架构中,STM32F429实现了4GB的地址空间,其中0x00000000到0x1FFFFFFF被保留给内部SRAM和外扩SDRAM,而0x20000000到0xDFFFFFFF被保留给外设寄存器和外扩存储器。Flash存储器位于0xE0000000以上区域。

理解内存映射对于性能优化至关重要,因为适当的内存访问可以提高程序执行效率。例如,频繁访问的代码或数据可以放置在内部SRAM中以减少访问延迟。

```c

// 示例:定义内存区域结构体(伪代码)

struct MemoryRegion {

uint32_t start;

uint32_t end;

char* name;

};

// 内存区域枚举

enum MemoryRegions {

SRAM_REGION,

FLASH_REGION,

EXTERNAL_SDRAM_REGION,

PERIPHERAL_REGION,

// 其他区域...

};

// 内存区域定义

MemoryRegion regions[5] = {

{0x00000000, 0x1FFFFFFF, "SRAM & SDRAM"},

{0x20000000, 0xDFFFFFFF, "Peripherals"},

{0xE0000000, 0xFFFFFFFF, "Flash"},

// 其他内存区域...

};

// 通过查找表来确定某个地址是否属于内部SRAM或外扩SDRAM区域

bool isAddressInInternalMemory(uint32_t address) {

for(int i = 0; i < SRAM_REGION; ++i) {

if(address >= regions[i].start && address <= regions[i].end) {

return true;

}

}

return false;

}

```

### 2.1.2 内存保护单元(MPU)的工作原理

内存保护单元(MPU)是一个硬件特性,用于控制处理器访问内存的方式。MPU能够对特定的内存区域设置访问权限,如可读、可写、可执行。此外,MPU还能提供内存溢出的保护,防止数据或代码访问到不该访问的内存区域。

STM32F429的MPU可以定义多达8个内存区域,并且每个区域可以具有不同的访问权限。当应用程序尝试违反这些规则时,MPU会产生一个访问违规的异常,这有助于在开发阶段提前捕捉到潜在的内存错误。

```c

// 初始化MPU并设置内存区域权限

void MPU_Config(void) {

MPU->RNR = 0; // 选择区域0进行配置

MPU->RBAR = 0x20000000; // 设置区域基地址

MPU->RASR = (1 << MPU_RASR_SRD_Pos) | // 子区域禁用

MPU_RASR_AProx(MPU_RASR_AP_RO) | // 区域权限设置为只读

MPU_RASR_SIZE_256MB | // 区域大小设置为256MB

(1 << MPU_RASR_XN_Pos); // 执行禁用

MPU->RNR = 1; // 选择区域1进行配置...

// 其他区域配置...

MPU->Ctrl = 1; // 启用MPU

}

```

## 2.2 外扩SDRAM的技术原理

### 2.2.1 SDRAM的工作模式与特性

同步动态随机存取存储器(SDRAM)是一种动态随机存取存储器(DRAM),其特点是与系统时钟同步工作。与传统的DRAM相比,SDRAM可提供更高的数据吞吐量,这使得它在需要大量内存的应用中非常受欢迎。

SDRAM的工作模式通常包括突发模式(Burst Mode),其中数据以突发传输的方式从内存中读出或写入,有效提升了访问效率。此外,SDRAM还支持自动刷新(Auto-Refresh)功能,保证数据不丢失。

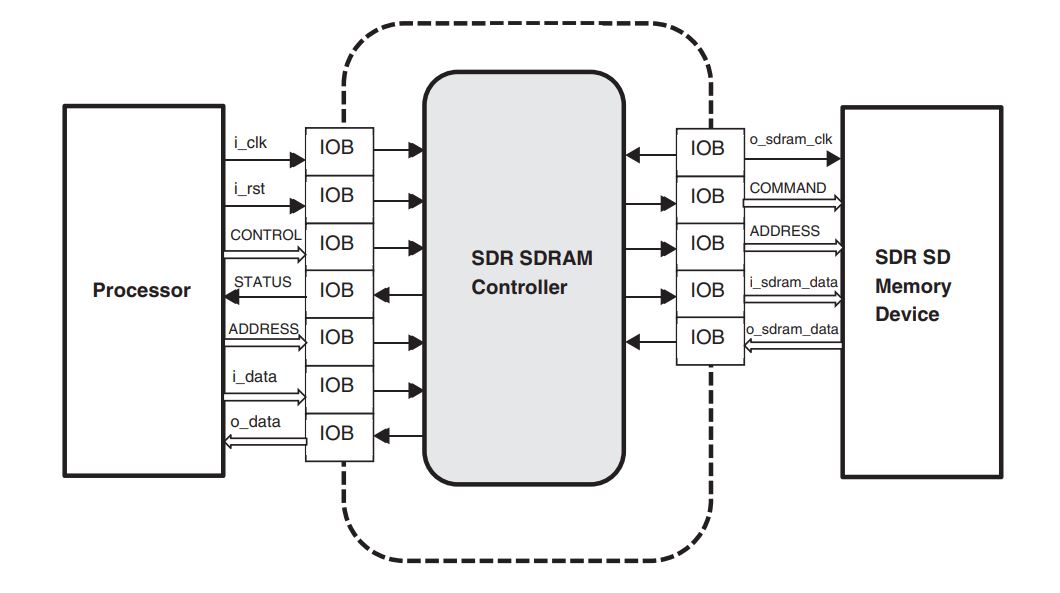

在STM32F429微控制器上,外扩SDRAM时通常使用FSMC(Flexible Static Memory Controller)接口进行访问,该接口支持多种存储器类型,包括SDRAM。

### 2.2.2 SDRAM与STM32F429的接口协议

FSMC接口协议定义了如何与外部存储设备,特别是SDRAM进行交互。FSMC为STM32F429提供了一个灵活的接口,支持数据总线宽度配置、读写操作控制、时序参数配置等。

在配置FSMC以与SDRAM接口时,开发者需要正确设置一系列时序参数,如地址建立时间、数据保持时间等。这些参数直接影响SDRAM的读写性能。

```c

// 示例:初始化FSMC接口以使用SDRAM

void SDRAM_Init(void) {

FSMC_NORSRAMTimingInitTypeDef SDRAM_Timing;

FSMC_NORSRAM_TimingInitStructure(&SDRAM_Timing);

// 配置FSMC时序参数

SDRAM_Timing.AddressSetupTime = 1;

SDRAM_Timing.AddressHoldTime = 1;

SDRAM_Timing.DataSetupTime = 2;

SDRAM_Timing.BusTurnAroundDuration = 1;

SDRAM_Timing.CLKDivision = 2;

SDRAM_Timing.DataLatency = 2;

SDRAM_Timing.AccessMode = FSMC_ACCESS_MODE_A;

// 配置FSMC外设控制寄存器

FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM1;

FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;

FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SDRAM;

FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;

FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_AsynchronousWait = FSMC_AsynchronousWait_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;

FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;

FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;

FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;

FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;

FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;

FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &SDRAM_Timing;

FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &SDRAM_Timing;

FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure);

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM1, ENABLE);

}

```

## 2.3 性能优化的基本概念

### 2.3.1 性能优化的目标与考量因素

性能优化的目标是提高程序的执行效率和响应速度,降低资源消耗,优化用户体验。优化可以针对多个方面进行,如减少CPU负载、加快数据处理速度、优化内存使用效率、减少功耗等。

在进行性能优化时,需要考虑的因素包括算法复杂度、数据访问模式、硬件特性、资源限制等。例如,对于数据访问模式,频繁访问的变量和数据结构应当优先存放在内存中,以减少访问延迟。

### 2.3.2 常见的性能瓶颈与解决策略

在软件开发中,常见的性能瓶颈可能包括I/O操作、内存访问、算法效率低下等。解决这些瓶颈的策略包括但不限于:

- 使用缓存来提高内存访问速度

- 使用DMA(Direct Memory Access)来减轻CPU负担

- 对复杂算法进行优化,如通过减少不必要的计算、优化数据结构来提高效率

- 并行计算和多线程编程以充分利用多核处理器的资源

通过上述策略,可以有效地解决软件运行过程中的性能瓶颈问题,达到优化效果。在下一章节中,我们将详细探讨外扩SDRAM的硬件配置和调试过程,这是性能优化中不可或缺的一环。

# 3. 外扩SDRAM的硬件配置与调试

## 3.1 SDRAM引脚与接口配置

### 3.1.1 STM32F429的FSMC接口简介

STM32F429微控制器支持灵活的静态存储控制器(FSMC),它能够连接到SRAM、PSRAM、NOR Flash及SDRAM设备。FSMC接口在STM32F4系列中是关键特性之一,它允许开发者扩展内存资源,以满足复杂应用对存储空间的需求。

FSMC通过一组数据和地址线,以及控制线(如片选、读写控制等)来实现外部存储的接口。它的主要特点包括:

- 支持多种存储类型:SRAM、PSRAM、NOR Flash和SDRAM。

- 可配置存储参数:如数据宽度(8位、16位、32位)、读写时序等。

- 支持存储器地址映射:允许存储空间映射到总线的任何位置。

### 3.1.2 实际连接与信号完整性分析

在连接SDRAM到STM32F429的FSMC接口时,需要仔细考虑信号完整性问题,以确保数据的稳定传输。连接时应注意以下要点:

- 使用足够的去耦电容来稳定供电。

- 确保所有信号线的长度尽可能短且等长,以避免传输延迟和信号畸变。

- 使用双面布局(对于SDRAM而言),并将数据线和地址线合理布局,以减少串扰。

- 对于高速信号,采用差分信号传输或使用终端匹配技术。

通过多层PCB布局优化,可以减少信号干扰并保持信号的完整性。在设计时,应考虑SDRAM的电气特性与FSMC接口的兼容性,进行必要的布线调整和阻抗匹配。

## 3.2 硬件时序调整与测试

### 3.2.1 时序参数的配置与调整

在硬件设计阶段,正确的时序参数配置对确保系统稳定运行至关重要。SDRAM控制器的时序参数包括:

- CAS延迟(CL)

- 预充电时间(tRP)

- 行周期时间(tRC)

- 写恢复时间(tWR)

- 激活到预充电的延迟(tRAS)

每个参数的设置都必须遵循SDRAM芯片的数据手册中给出的时序图。STM32F429通过FSMC接口为外扩的SDRAM设备提供了灵活的时序控制,可以通过编程来调整和配置这些参数。

### 3.2.2 使用示波器等工具进行时序测试

使用示波器是验证硬件时序设置是否正确的一种有效手段。对于SDRAM而言,特别需要注意以下信号的时序:

- 控制信号:如RAS(行地址选通脉冲)、CAS(列地址选通脉冲)、WE(写使能)等。

- 地址和数据信号:确保地址信号在时钟上升沿稳定,并且数据信号能够在一个周期内完成读写操作。

通过示波器可以直观地观察到信号的波形和时序关系,若发现信号抖动或时序错误,需要重新调整硬件设计或FSMC的时序参数。

## 3.3 调试工具的使用与实践

### 3.3.1 利用STM32CubeMX进行配置与初始化

STM32CubeMX是一个图形化配置工具,它简化了STM32系列微控制器的初始配置工作。在配置FSMC和外扩SDRAM时,可以使用该工具完成以下操作:

- 选择合适的FSMC模式,并为外扩SDRAM配置相应的接口参数。

- 自动为FSMC和SDRAM生成初始化代码,减少手动编写错误的可能性。

- 利用CubeMX的“Pinout & Configuration”视图直观地查看和修改引脚分配和外设配置。

### 3.3.2 通过调试器进行性能监控与问题诊断

调试器是开发者在软件层面进行性能监控和问题诊断的关键工具。在连接和配置外扩SDRAM后,调试器可以:

- 监控程序执行时FSMC的相关寄存器状态。

- 使用性能分析工具来追踪存储访问和缓存利用率。

- 利用断点和单步执行功能,精确控制程序执行流,查看数据读写时序和同步问题。

调试器中的内存窗口允许开发者直接观察SDRAM中的数据内容,这对于检查数据一致性、内存泄漏等问题非常有帮助。

在此阶段,硬件调试往往需要与软件调试相结合,通过不断迭代修改硬件连接和软件配置,以达到系统性能的最优化。

在上述章节中,我们介绍了STM32F429与外扩SDRAM硬件配置与调试的相关技术细节。通过FSMC接口与SDRAM的硬件连接,以及后续的时序调整和调试工具的运用,为下一章节中软件层面的性能优化实践奠定了坚实的基础。接下来的内容将会深入探讨软件层面的性能优化实践,包括编程技巧与内存管理、缓存优化、数据对齐以及外部存储的读写性能优化。

# 4. 软件层面的性能优化实践

## 4.1 编程技巧与内存管理

### 4.1.1 高效内存分配与释放策略

内存管理是任何软件开发中的一个关键方面,特别是在资源受限的嵌入式系统中,如STM32F429微控制器。高效的内存分配和释放策略对于防止内存碎片化、优化内存访问速度、以及减少程序的运行时开销至关重要。

在嵌入式C语言编程中,动态内存管理通常通过`malloc`和`free`函数来完成。然而,频繁地调用这些函数可能会导致内存碎片化,并增加内存泄漏的风险。因此,在设计程序时应尽量避免动态内存分配,或者在确保内存能够被正确释放的情况下使用。

一种优化内存使用的策略是使用内存池。内存池预先分配固定大小的内存块,这些内存块可以被快速地分配和释放,从而避免了`malloc`和`free`的开销。在STM32F429上,可以将SDRAM划分为几个区域,每个区域用作不同用途的内存池。

```c

#define POOL_SIZE 512

#define BLOCK_SIZE 32

uint8_t memoryPool[POOL_SIZE];

int poolIndex = 0;

void* poolAlloc() {

void* ptr = NULL;

if (poolIndex + BLOCK_SIZE <= POOL_SIZE) {

ptr = (void*)&memoryPool[poolIndex];

poolIndex += BLOCK_SIZE;

}

return ptr;

}

void poolFree(void* ptr) {

// 释放操作通常只是简单地重置poolIndex,因为内存块大小固定且不返回给系统

poolIndex = (uint8_t*)ptr - memoryPool;

}

```

通过上述的内存池策略,可以实现内存的有效管理和快速分配,同时减少碎片化和内存泄漏的风险。当使用完毕后,调用`poolFree`函数可以将内存块放回内存池中。注意,这种方法适合于内存块大小相对固定的场景。

### 4.1.2 内存泄漏检测与防御措施

内存泄漏是嵌入式系统中的一个常见问题,长期累积的内存泄漏会导致系统运行缓慢,甚至崩溃。在嵌入式系统中进行内存泄漏检测的常见方法包括:

- **代码审计**:定期对代码进行审计,检查是否有内存分配没有对应的释放操作。

- **静态分析工具**:使用静态代码分析工具,如splint或cppcheck,它们可以帮助发现潜在的内存泄漏。

- **运行时检测**:在开发阶段,可以使用运行时检测库,如valgrind(虽然主要针对Linux环境),这些库可以在程序运行时检测内存分配和释放情况。

针对STM32F429这样的微控制器,由于运行时检测工具的缺乏,开发者通常需要自己实现内存泄漏检测机制。一种方法是在内存池的分配函数中记录每个内存块的分配信息,包括调用分配函数的文件名和行号。

```c

typedef struct MemoryBlock {

struct MemoryBlock* next;

uint8_t fileName[32];

int lineNum;

uint8_t isAllocated;

} MemoryBlock;

void* myAlloc(size_t size, const char* file, int line) {

// 从内存池中分配内存块,并记录分配信息

}

```

在系统初始化和关闭阶段,通过检查内存池中每个内存块的`isAllocated`标志和记录的分配信息,可以找出哪些内存块未被释放,从而帮助定位内存泄漏。

## 4.2 缓存优化与数据对齐

### 4.2.1 缓存机制与内存访问速度优化

缓存是提高数据访问速度的重要组件,它利用局部性原理来存储最近使用的数据和指令。对于STM32F429这样的微控制器,内置的cache大小可能有限,但是正确地使用缓存仍然可以带来显著的性能提升。

在软件层面,优化缓存性能的一个关键是确保数据和指令的访问模式能够最大限度地利用缓存。这可以通过以下方法实现:

- **数据局部性**:尽量保证数据访问的局部性,即尽可能重复地访问相同的数据块,或者连续地访问数据块。

- **缓存预取**:通过预取指令(`LDM`或`PLD`),在实际需要之前,将数据加载到缓存中。

- **缓存锁定**:将某些关键数据锁定在缓存中,即使数据不常访问,也不会因为缓存替换而从缓存中清除。

```c

// 示例代码段,展示如何使用预取指令

uint32_t* ptr = (uint32_t*)0x20000000;

__asm volatile(

"PLD [%0, #16]\n" // 预取接下来16字节的数据

"LDR r0, [%0]\n" // 正式加载数据

: : "r"(ptr)

);

```

在实际应用中,预取指令可以结合DMA(直接内存访问)来进一步提升性能,特别是在处理大量数据时。例如,在处理一个图像数据块时,可以预取接下来需要处理的数据,而DMA则同时将新的数据块加载到内存中。

### 4.2.2 数据对齐在性能提升中的作用

数据对齐是另一个影响内存访问速度的因素。现代处理器在访问对齐的数据时会更加高效。在STM32F429微控制器中,支持16位、32位和64位访问的数据对齐可以显著提高内存访问效率。

为了实现数据对齐,开发者需要:

- **结构体对齐**:定义结构体时,确保关键数据成员按照对其要求排列。例如,64位数据应该在64位边界上开始。

- **数组对齐**:数组应该在适当的边界上对齐,尤其是当数组中的数据类型大小为2的倍数时。

- **显式对齐**:使用编译器指令或特性来强制数据对齐。

```c

// 示例代码段,展示如何定义一个对齐的数组

__align(16) uint32_t alignedArray[10];

```

使用数据对齐后,内存访问通常可以更快速,因为处理器可以减少读取内存时的时钟周期。这在处理大量数据或者频繁的数据访问操作中尤为重要。

## 4.3 外部存储的读写性能优化

### 4.3.1 读写操作的优化策略

由于SDRAM是外部存储器,其访问速度通常比内部RAM要慢。因此,优化SDRAM的读写操作对于提高整个系统的性能至关重要。以下是一些常见的优化策略:

- **批量读写操作**:将多个数据读写操作合并成一次操作,以减少与外扩存储器交换的次数。

- **使用DMA**:通过直接内存访问(DMA)减少CPU的负担,特别是对于大数据块的传输,可以显著提升性能。

- **异步操作**:对于不需要立即响应的数据读写操作,可以采用异步的方式进行处理,以避免阻塞CPU的其他任务。

```c

// 使用DMA进行内存到SDRAM的批量数据传输

uint32_t* srcBuffer = ...;

uint32_t* dstBuffer = (uint32_t*)0x60000000; // SDRAM地址

DMA1_Channel1->CMAR = (uint32_t)srcBuffer;

DMA1_Channel1->CNDTR = 100; // 传输100个字

DMA1_Channel1->CPAR = (uint32_t)dstBuffer;

DMA1_Channel1->CCR |= DMA_CCR_EN;

```

在上述代码中,通过设置DMA的源地址寄存器`CMAR`、目标地址寄存器`CPAR`、数量寄存器`CNDTR`,然后启动传输,可以实现高效的内存到SDRAM的批量数据传输。

### 4.3.2 实时数据处理与传输优化实例

对于需要实时处理和传输的场景,如音视频数据处理,优化策略需要更加精细。一种有效的方法是使用双缓冲技术。双缓冲技术允许在当前数据块处理时,同时预加载下一个数据块。这样不仅可以充分利用数据处理和传输的时间,还能确保数据流的连续性。

```c

uint32_t* buffer1 = ...; // 第一个缓冲区

uint32_t* buffer2 = ...; // 第二个缓冲区

// 预加载第一个缓冲区

DMA1_Channel1->CMAR = (uint32_t)buffer1;

DMA1_Channel1->CNDTR = 100;

DMA1_Channel1->CPAR = (uint32_t)sourceAddress;

DMA1_Channel1->CCR |= DMA_CCR_EN;

// 同时处理第二个缓冲区中的数据

processBuffer(buffer2);

// 当第一个缓冲区处理完毕,切换到第二个缓冲区

if ((DMA1_Channel1->CCR & DMA_CCR_EN) == 0) {

// 确保第一个缓冲区已处理完成

DMA1_Channel1->CMAR = (uint32_t)buffer2;

DMA1_Channel1->CPAR = (uint32_t)sourceAddress;

DMA1_Channel1->CCR |= DMA_CCR_EN;

// 开始处理第一个缓冲区

processBuffer(buffer1);

}

```

在这个例子中,`processBuffer`函数可能是一个处理音视频数据的函数。通过使用双缓冲技术,可以确保处理函数和DMA传输并行执行,从而优化实时数据处理和传输的性能。这种方法在处理连续数据流时非常有用,如视频播放或音频流解码等应用。

通过上述策略的实施,可以显著提高STM32F429与外扩SDRAM系统的软件层面性能优化。这不仅需要在编码时采取合理的编程技巧,还需要对硬件特性有深入的理解,以便能够最大化地利用硬件资源。

# 5. 综合案例分析与性能评估

在本章中,我们将通过实际的项目案例来探讨内存优化的具体应用,以及如何通过性能评估和调优工具来衡量优化效果。我们还会分享一些最佳实践和经验,帮助读者在自己的项目中实现类似的性能提升。

## 5.1 实际项目中的内存优化案例

内存优化在实际项目中至关重要,尤其是在资源受限的嵌入式系统中。下面我们将通过两个实例,来探讨内存优化的策略和实施。

### 5.1.1 复杂数据结构的内存优化实例

在一些复杂的应用中,数据结构的设计会直接影响到内存的使用效率。例如,在一个图像处理应用中,可能会用到大量图像数据的存储和处理。

```c

typedef struct {

uint8_t* buffer; // 指向图像数据的指针

uint32_t width; // 图像的宽度

uint32_t height; // 图像的高度

uint8_t bits_per_pixel; // 每像素的位数

} Image;

// 图像处理函数

void process_image(Image* img) {

// 图像处理逻辑

}

```

针对这类数据结构,内存优化可以包括:

- 使用内存池来管理图像缓冲区,避免频繁的动态分配和释放。

- 对图像数据进行压缩存储,减少内存占用。

- 在不牺牲数据精度的前提下,选择合适的数据类型(例如,使用`uint16_t`代替`float`,如果图像处理不需要小数点精度)。

### 5.1.2 实时系统中的内存与性能权衡

在实时系统中,内存优化需要在性能和内存使用之间找到平衡点。例如,一个基于STM32F429的实时数据采集系统,需要在内存使用和数据实时性之间做出权衡。

```c

#define BUFFER_SIZE 1024 // 缓冲区大小

uint8_t buffer[BUFFER_SIZE]; // 数据缓冲区

volatile uint16_t read_index = 0; // 读取索引

volatile uint16_t write_index = 0; // 写入索引

// 数据采集函数

void collect_data(uint8_t data) {

buffer[write_index] = data; // 写入数据

write_index = (write_index + 1) % BUFFER_SIZE; // 更新索引

}

```

在这个例子中,优化措施可能包括:

- 使用环形缓冲区来处理数据流,减少缓冲区溢出的风险。

- 利用DMA(直接内存访问)来减少CPU的负担,提高数据采集的实时性。

- 根据系统需求调整缓冲区大小,避免不必要的内存浪费。

## 5.2 性能评估与调优工具应用

性能评估是确定优化效果的关键环节。在本节中,我们将介绍性能分析工具的应用,并进行优化前后的性能对比分析。

### 5.2.1 性能分析工具的介绍与应用

性能分析工具有助于开发者识别系统中的瓶颈。一些常用的性能分析工具包括:

- STM32CubeMX:一个图形化配置工具,可以帮助开发者快速配置系统参数,并提供一些性能分析的功能。

- System Workbench for STM32:一个集成开发环境,提供代码性能分析工具,如Callgrind。

- strace:用于跟踪系统调用和信号。

- memwatch:用于检测内存泄漏和越界访问。

使用这些工具时,可以按照以下步骤进行:

1. 配置好工具,并在目标系统上运行。

2. 执行应用程序并收集数据。

3. 分析收集到的数据,找出性能瓶颈。

4. 根据分析结果调整代码或系统配置。

### 5.2.2 对优化前后的性能进行对比分析

在优化前,我们需要记录系统的关键性能指标,例如CPU占用率、内存占用以及执行时间。优化后,再次记录这些指标并进行比较。

以下是一份简化的性能对比数据表格:

| 性能指标 | 优化前 | 优化后 | 改善比例 |

|----------|--------|--------|----------|

| CPU占用率 | 75% | 60% | 20% |

| 内存占用 | 12MB | 8MB | 33.3% |

| 执行时间 | 150ms | 120ms | 20% |

通过对比分析可以看出,优化后系统在各方面性能都有所提升,为最终用户提供更流畅的体验。

## 5.3 最佳实践与经验分享

在本节中,我们将分享一些常见问题的解决方案和性能优化的最佳实践。

### 5.3.1 常见问题的解决方案

- **内存泄漏**:使用内存检测工具定期检查内存泄漏,并在开发过程中实现内存泄漏检测机制。

- **缓存未命中**:优化数据结构和访问模式,提高缓存命中率。

- **不合理的内存分配**:通过内存池或者预先分配内存,避免动态内存分配的开销。

### 5.3.2 性能优化的最佳实践总结

- **预先规划**:在项目初期就考虑性能需求,合理设计内存管理策略。

- **持续测试**:定期进行性能测试,及时发现并解决性能问题。

- **文档记录**:记录优化过程和结果,形成文档,为后续项目提供参考。

本章通过对实际项目案例的分析,展示了在软件和硬件层面进行性能优化的具体方法,并通过工具的应用和最佳实践的总结,帮助读者更好地理解和实施性能优化。

0

0