【STM32F429系统升级必读】:集成SDRAM后的新挑战及应对之道

发布时间: 2024-12-19 19:15:09 阅读量: 4 订阅数: 8

正点原子stm32f429 cubemx sdram工程

# 摘要

本文针对STM32F429系统的升级进行了全面的探讨,从SDRAM的理论基础与集成实践,到系统升级过程中遇到的新挑战及其应对策略,最后展望了未来的技术趋势和创新方向。文章首先介绍了SDRAM技术背景及其在STM32F429中的集成和配置,包括硬件连接、初始化设置、性能评估等关键环节。随后,围绕SDRAM在实际应用中的编程基础、数据管理和故障诊断进行了深入分析。接着,重点讨论了系统升级时遇到的稳定性和性能挑战,以及安全漏洞的防范。通过案例研究,总结了系统升级的成功经验和失败教训。最后,文章展望了未来存储技术的发展和系统升级的长远规划,强调技术创新在持续升级过程中的核心作用。

# 关键字

STM32F429;SDRAM集成;系统升级;性能优化;故障诊断;技术创新

参考资源链接:[STM32F429外扩SDRAM编程入门与常见错误排查](https://wenku.csdn.net/doc/646db6e3543f844488d7f35e?spm=1055.2635.3001.10343)

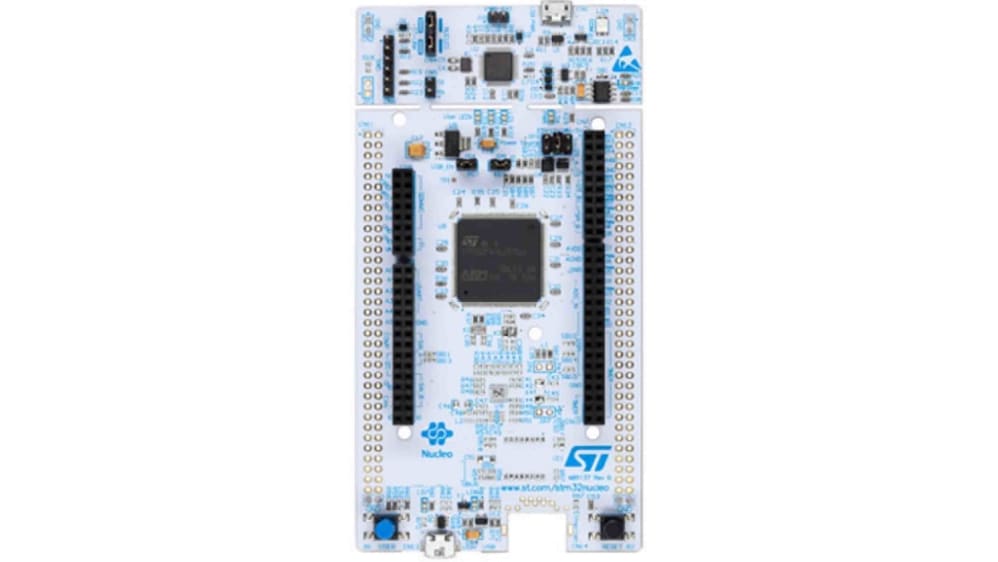

# 1. STM32F429系统升级概述

STM32F429系列微控制器由于其高性能与丰富的功能,广泛应用于多种嵌入式系统。随着技术的不断发展,系统升级成了必要,以满足不断增长的性能需求和新功能的加入。在进行STM32F429系统升级时,开发者通常关注以下几个方面:

- 硬件性能的提升:通过更新的外设接口,高速通信协议支持,以及更优化的电源管理来提升性能。

- 系统软件的优化:包括操作系统的更新,驱动程序的升级以及应用程序的优化,以提高系统整体的稳定性和效率。

- 安全性的加强:随着技术的发展,系统安全显得尤为重要,加强加密算法和安全漏洞的修补是升级过程中的关键部分。

本章将对STM32F429系统升级的背景、目标及初步步骤进行概述,为进一步深入探讨系统升级的细节打下基础。下一章将深入探讨SDRAM集成的理论基础,为系统升级提供必要的理论支撑。

# 2. SDRAM集成的理论基础

### 2.1 SDRAM的技术背景

#### 2.1.1 SDRAM的工作原理

同步动态随机存取存储器(SDRAM)是一种广泛使用的存储技术。它的基本工作原理可以简化为几个关键步骤:

- **时钟同步**:SDRAM中的数据读写都是在时钟信号的上升沿进行,这使得数据传输可以与系统时钟同步,从而提高效率。

- **行和列寻址**:数据存放在内存的行列交叉点上,通过行地址和列地址的指定来定位具体数据。

- **预充电和刷新**:SDRAM需要周期性的刷新来保持数据,这涉及到预充电和刷新操作。

在了解了SDRAM的工作原理后,我们可以进一步分析STM32F429如何与SDRAM结合使用。

```mermaid

flowchart LR

A[SDRAM芯片] -->|时钟同步| B[时钟同步接口]

B --> C[控制逻辑]

C -->|行列寻址| D[数据存储矩阵]

D -->|读写操作| E[数据输出]

C -->|预充电和刷新| F[刷新逻辑]

```

#### 2.1.2 STM32F429与SDRAM的兼容性分析

STM32F429系列微控制器是基于ARM Cortex-M4核心设计的,具备较强的处理能力和丰富的外设接口。它的FSMC(Flexible Static Memory Controller)外设支持多种类型的存储器,包括SDRAM。

为了确保STM32F429与SDRAM的兼容性,需要考虑以下几个方面:

- **接口匹配**:确保STM32F429的FSMC接口能够与SDRAM的电气特性相匹配。

- **时序要求**:分析并设置FSMC的时序参数以满足SDRAM的时序要求。

- **初始化过程**:编写代码在系统启动时对SDRAM进行正确的初始化。

```c

// 代码示例:STM32F429的SDRAM初始化流程(伪代码)

void SDRAM_Init() {

// 初始化FSMC

FSMC_Config();

// 初始化SDRAM控制器

SDRAM_Controller_Init();

// 执行SDRAM自检

SDRAM_SelfTest();

// 设置显示缓冲区

Set_Display_Buffer();

}

```

### 2.2 SDRAM在STM32F429中的配置

#### 2.2.1 硬件连接与初始化

硬件连接是将SDRAM芯片通过FSMC接口与STM32F429微控制器连接起来。初始化过程通常包括设置FSMC的控制寄存器,配置数据宽度,以及设置时钟频率等。

- **FSMC接口设置**:通过FSMC的Bank配置寄存器来设置具体的SDRAM参数。

- **时钟配置**:根据SDRAM的速度等级和时序要求,配置相应的时钟。

```c

// 代码示例:FSMC接口设置(伪代码)

void FSMC_Config() {

// 配置FSMC Bank为SDRAM模式

FSMC_Bank1->BTCR[FSMC_Bank1_Bank] = (FSMC_Bank1_Bank_MemoryType_SDRAM | FSMC_Bank1_Bank_DataAddress_Multiplex | FSMC_Bank1_Bank_MemoryDataWidth_16b);

// 配置时序参数

FSMC_Bank1->BTCR[FSMC_Bank1_Bank + 2] = (/* 时序参数 */);

}

```

#### 2.2.2 配置寄存器与时序调整

正确配置寄存器并调整时序对于实现高性能的SDRAM访问至关重要。这包括读取周期、写入周期、行周期、预充电周期、激活至读/写延迟以及刷新间隔等。

- **读写周期参数设置**:根据数据手册中的时序图表设置读写周期。

- **刷新间隔设置**:根据SDRAM规格书中的数据保留时间来设置刷新间隔。

```c

// 代码示例:SDRAM控制器初始化(伪代码)

void SDRAM_Controller_Init() {

// 设置SDRAM控制器参数

SDRAMC->SDRTR = /* 刷新时间间隔 */;

SDRAMC->SDCR = /* 控制寄存器参数 */;

// 其他必要设置

}

```

### 2.3 SDRAM性能评估

#### 2.3.1 性能测试标准和方法

SDRAM性能评估通常涉及几个关键参数:数据吞吐量、访问延迟和稳定性。测试标准和方法可以包括:

- **吞吐量测试**:使用基准测试软件来测量读写数据的速率。

- **访问延迟测试**:测量从发出访问请求到数据开始传输之间的延迟时间。

- **稳定性测试**:长时间运行以检测系统的稳定性。

#### 2.3.2 性能优化的理论依据

为了进一步提高SDRAM性能,可以考虑以下几个理论依据:

- **数据局部性原理**:通过缓存机制利用数据访问的局部性原理来减少SDRAM访问。

- **异步访问**:通过异步访问来减少时钟周期的空闲等待,提升吞吐量。

- **优化刷新策略**:合理的刷新间隔和策略可以减少对性能的影响。

通过深入理解和运用上述理论,我们可以对STM32F429中的SDRAM进行有效的配置和优化,以期达到最佳的系统性能。接下来,在第三章中,我们将深入探讨SDRAM在STM32F429中的具体应用实践。

# 3. SDRAM集成的实践应用

SDRAM(Synchronous Dynamic Random Access Memory)作为同步动态随机存取存储器,因其高密度、低成本和高速率的特点,被广泛应用于嵌入式系统中,尤其在STM32F429这样的高性能微控制器系统中扮演着关键角色。在深入了解了SDRAM的技术背景、工作原理和与STM32F429的兼容性之后,接下来的章节将深入探讨其在实际应用中的具体实践,包括编程基础、数据管理和故障诊断与修复。

#

0

0