ARM多核处理器架构与并发编程实践

发布时间: 2024-04-14 06:08:38 阅读量: 159 订阅数: 52

# 1. 多核处理器架构解析

在当今信息技术高速发展的背景下,多核处理器架构已经成为了主流。通过将多个处理器核心集成在同一芯片上,实现了更高的计算性能和能效比。分布式处理与并行计算技术的不断进步使得多核处理器能够更好地发挥其优势,实现任务的高效并发处理。多核处理器架构经过多年的演进,从最初的对称式多核处理器发展到了更加灵活的异构处理器架构,更好地满足不同应用场景的需求。多核处理器架构的不断演进,也带来了并发编程方面的挑战,如内存一致性、处理器调度、数据通信等问题需要我们深入研究和解决。

# 2. ARM架构与多核处理器

### 2.1 ARM处理器基础概念

ARM(Advanced RISC Machine)架构是一种精简指令集计算机(RISC)架构,广泛应用于移动设备、嵌入式系统和物联网设备中。ARM处理器以其低功耗、高性能的特点备受青睐。

#### 2.1.1 嵌入式处理器介绍

嵌入式处理器是指集成在各种设备中,用于控制设备功能的微处理器。ARM嵌入式处理器因其低功耗、高效能的特性,在智能手机、平板电脑等设备中被广泛应用。

#### 2.1.2 ARM架构特点分析

ARM架构相较于复杂指令集计算机(CISC)架构,精简指令集计算机(RISC)架构具有指令集简化、执行效率高等特点。ARM处理器具备低功耗、高性能的特性,适用于移动设备等场景。

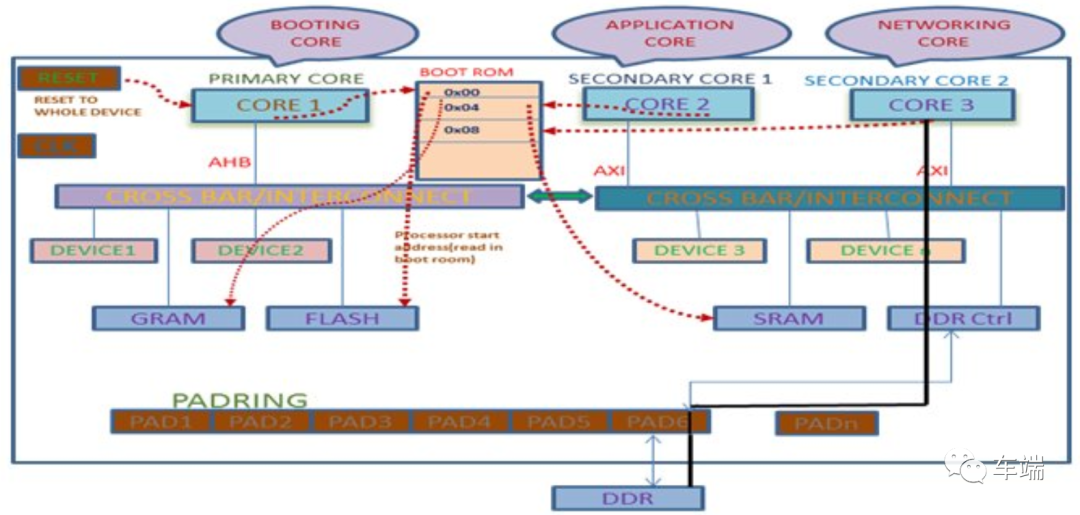

### 2.2 ARM多核处理器设计

ARM多核处理器设计旨在提高处理器的计算性能和能效比,常见的设计包括对称式多核处理器和异构处理器架构。

#### 2.2.1 对称式多核处理器

对称式多核处理器中,每个处理核心可以相互访问共享内存,各核心之间的通讯更为简单高效。这种架构通常用于需要较高计算性能的场景。

#### 2.2.2 异构处理器架构

异构处理器架构将不同类型的处理器核心集成在同一芯片上,如大核心和小核心的组合。大核心用于高性能计算,小核心则用于低功耗场景,通过智能调度实现性能和功耗的最佳平衡。

### 2.3 ARM架构与多核并发编程挑战

ARM架构下的多核处理器面临着诸多并发编程挑战,包括内存一致性与并发控制、处理器调度与负载均衡、数据通信与同步机制等方面的问题。

#### 2.3.1 内存一致性与并发控制

多核处理器中各核心操作共享内存时需要保证内存一致性,避免数据冲突和不一致。并发控制机制如锁、原子操作等是保证数据一致性的重要手段。

#### 2.3.2 处理器调度与负载均衡

在多核处理器系统中,合理的处理器调度能够最大程度地发挥各核心的性能,避免出现负载不均衡导致性能瓶颈的情况。

#### 2.3.3 数据通信与同步机制

多核处理器间需要进行高效的数据通信和同步,采用合适的通信机制如消息队列、共享内存,以及同步方法如信号量、事件驱动等是确保系统并发运行的关键。

# 3. 并发编程基础

### 3.1 并发与并行的概念

并发编程是指程序设计的一种范式,允许多个操作同时进行。与之相对的是并行,即多个操作真正同时执行。并发与并行的区别在于操作是否同步进行。并发编程的优势在于提高系统吞吐量和资源利用率,但也带来了数据安全和性能调优的挑战。

### 3.2 线程与进程

线程是操作系统进行调度的基本单位,进程是程序的运行实例。线程共享进程的内存空间,因此线程间的数据共享更为方便。线程管理涉及线程创建、销毁、同步与互斥。进程间通信

0

0