高可靠系统中的AXI4应用:关键技术与成功案例

发布时间: 2024-12-21 10:48:05 阅读量: 7 订阅数: 12

pg059-axi-interconnect_fpga_pg059_axiinterconnect_AXI_

# 摘要

本文系统地介绍了AXI4协议的基础知识、关键技术、系统可靠性需求、硬件和软件层的应用实践,以及未来发展趋势。AXI4协议是一种广泛应用于集成电路设计的高性能接口协议,以其通信机制、高带宽和低延迟特性为系统可靠性提供了坚实基础。文章详细分析了AXI4协议的关键特性、在硬件设计和软件驱动中的实现方法,以及如何利用错误检测与纠正技术以及系统备份策略提升系统整体的可靠性。同时,本文也探讨了AXI4技术在并行编程和高效数据传输策略中的应用,并对AXI4面临的技术挑战和未来可能的发展方向进行了展望。

# 关键字

AXI4协议;系统可靠性;通信机制;错误检测与纠正;硬件设计;软件驱动

参考资源链接:[ARM AMBA AXI4协议中文版:最新规格与详解](https://wenku.csdn.net/doc/6412b702be7fbd1778d48c31?spm=1055.2635.3001.10343)

# 1. AXI4协议概述与系统可靠性需求

## 1.1 AXI4协议简介

AXI4(Advanced eXtensible Interface 4)是ARM公司定义的一种高性能的片上总线协议,它主要用于SoC(System on Chip)内部不同功能模块之间的通信。作为一个开放的标准,AXI4协议能够满足现代电子系统日益增长的性能需求,特别是对于数据密集型应用。

## 1.2 系统可靠性需求

随着对系统稳定性的要求不断提高,系统可靠性成为了设计中不可或缺的一部分。AXI4协议在设计时考虑到了系统的可靠性需求,通过内置的错误校验和处理机制,保证了数据在传输过程中的完整性和准确性。

## 1.3 AXI4协议与系统可靠性之间的关系

系统可靠性不仅仅依赖于硬件的稳定性,还需要在协议层面上提供保障。AXI4协议通过定义严格的协议规则和机制,如事务标识和响应,确保了即使在高流量和复杂操作下也能维持系统稳定性。

# 2. ```

# 第二章:AXI4协议的关键技术与实现

在深入理解了AXI4协议的基础知识之后,本章节将重点探讨AXI4协议的关键技术与实现细节。我们将从通信机制、特性与优势、以及在系统可靠性设计中的应用三个方面逐一展开。

## 2.1 AXI4协议的通信机制

AXI4协议的通信机制是其作为高性能总线协议的核心,它确保了数据能够高效且准确地在处理器、存储器和其他系统组件之间传输。

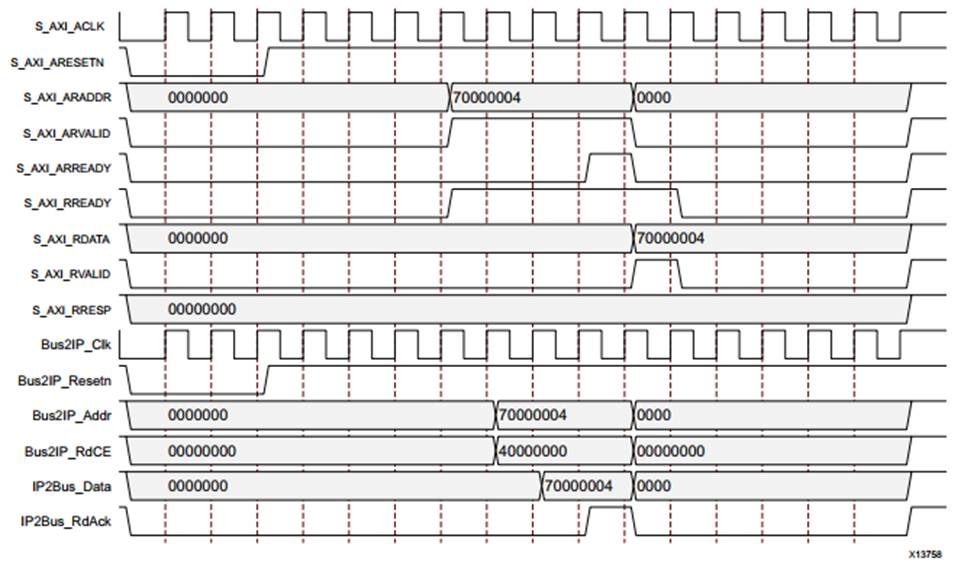

### 2.1.1 地址通道和数据通道的运作

在AXI4协议中,一个事务由地址通道和数据通道共同完成。地址通道用于传递地址信息和控制信息,它携带了读写请求的初始信息,包括目标地址、传输长度、传输类型等。而数据通道负责传输实际的数据内容,它可以是单次的数据传输也可以是突发传输,对应单个数据包或多个连续数据包的发送。

```

// 示例代码:定义一个简单的AXI4地址通道操作

// 参数说明:

// AWID: 地址ID,用于区分多个并发传输

// AWADDR: 目标地址

// AWLEN: 传输长度,表示突发传输中的传输量

// AWSIZE: 传输大小,指定数据宽度

// AWBURST: 突发传输类型,例如固定、递增或环形

parameter integer C_ADDR_WIDTH = 32; // 地址宽度

parameter integer C_DATA_WIDTH = 256; // 数据宽度

typedef struct packed {

logic [C_ADDR_WIDTH-1:0] AWADDR;

logic [7:0] AWLEN;

logic [2:0] AWSIZE;

logic [1:0] AWBURST;

} axi4_address_channel;

```

### 2.1.2 突发传输和流水线传输机制

AXI4支持两种主要的传输机制:突发传输和流水线传输。突发传输适用于连续的数据流,例如,当内存需要读取或写入一系列连续的数据块时,可以使用突发传输以提高效率。流水线传输允许多个传输操作并行进行,通过在地址通道和数据通道上同时进行多个读写操作,大大提高了总线利用率。

```

// 示例代码:展示突发传输操作流程

// 参数说明:

// ARID: 地址ID

// ARADDR: 地址

// ARLEN: 突发长度

// ARSIZE: 突发大小

axi4_address_channel ar_channel;

ar_channel.ARID = 1; // 事务标识

ar_channel.AWADDR = 32'hA000_0000; // 地址

ar_channel.AWLEN = 8'h0F; // 突发长度为16

ar_channel.AWSIZE = 3'b100; // 数据宽度为256位

// 在AXI4协议中,流水线传输是指地址和数据可以在不同阶段重叠,允许系统在一个事务完成之前就开始另一个事务。这种机制对于提高带宽利用率至关重要。

```

## 2.2 AXI4协议的特性与优势

AXI4协议具有多项特性,这些特性是它能够满足现代高性能系统需求的关键所在。

### 2.2.1 AXI4与前代协议的对比

AXI4协议相较于其前代协议AXI3,进行了多处改进。例如,AXI4引入了更灵活的突发传输模式、增加了对流传输的支持,并且允许在没有握手信号的情况下进行连续传输,减少了延迟,提高了效率。

```

| 特性 | AXI4协议支持 | AXI3协议支持 |

|------------|--------------|--------------|

| 突发传输 | 是 | 是 |

| 流传输 | 是 | 否 |

| 无握手传输 | 是 | 否 |

```

### 2.2.2 支持高带宽和低延迟的特性

AXI4协议通过改进数据包格式、增加传输宽度、以及优化传输控制逻辑来提高总线的数据吞吐量,同时减少传输延迟。这些特性使得AXI4成为满足当前和未来系统设计带宽需求的理想选择。

## 2.3 系统可靠性设计中的AXI4应用

为保证系统的稳定性和可靠性,AXI4协议设计了多种机制来应对潜在的错误和故障。

### 2.3.1 错误检测与纠正技术

为了提高数据传输的可靠性,AXI4协议支持多种错误检测与纠正技术,包括奇偶校验和更复杂的ECC技术。这些技术能够检测和(在一些情况下)修正数据传输中出现的错误,保证数据的完整性和准确性。

```

// 示例代码:实现一个简单的奇偶校验逻辑

// 假设我们有一个32位的数据宽度

function logic calculate_parity(input logic [31:0] data);

logic parity_bit;

for (int i = 0; i < 32; i++) begin

parity_bit = parity_bit ^ data[i];

end

return parity_bit;

endfunction

// 在传输数据时,可以计算并附加一个奇偶校验位,接收方在接收到数据后再次进行奇偶校验,以检查是否有错误发生。

```

### 2.3.2 系统备份和故障转移策略

在系统级,AXI4协议支持备份和故障转移策略。例如,它可以与系统中的冗余组件配合,一旦检测到故障即可切换到备用路径,确保系统的持续运行。

```

// 系统备份示例伪代码

// 假设有主备两个路径,主路径失败时,切换到备份路径

if (primary_path_failed) {

switch_to_secondary_path();

}

```

通过这些机制,AXI4协议不仅提高了数据传输的效率,同时也为系统设计者提供了强大的工具来设计和实现稳定、可靠的系统。接下来,我们将探讨AXI4在硬件设计中的具体应用实践。

```

# 3. AXI4协议在硬件设计中的应用实践

随着系统复杂度的不断增加,硬件设计人员需要更加高效和可靠的通信协议来支持日益增长的数据吞吐需求。AXI4(Advanced eXtensible Interface 4)作为ARM公司推出的一种高性能、高带宽的片上互连标准,已成为许多高性能系统设计的核心。本章将详细探讨AXI4协议在硬件设计中的应用实践,包括I

0

0