AXI4协议深度剖析:性能优化与故障排除秘籍(必备技能全解析)

发布时间: 2024-12-21 09:28:22 阅读量: 16 订阅数: 13

AXI4-协议规范解析_axi总线_AXI协议_axi4_AXI4协议_AXI_

# 摘要

本论文对AXI4协议进行了全面的介绍,从基础知识点到性能优化,再到故障排除和实际应用案例分析,最后探讨了该协议的未来发展趋势。首先,我们介绍了AXI4协议的基础知识,并针对性能优化策略进行了深入研究,包括识别性能瓶颈、数据传输效率优化以及提升接口并发处理能力的方法。接着,论文详细讨论了故障排除的技巧,包括故障的识别、诊断、处理以及预防性维护策略。此外,本文还探讨了AXI4在FPGA项目、SoC设计以及高速数据传输系统中的具体应用。最后,对AXI4协议的技术演进、行业发展趋势和持续优化路径进行了展望。

# 关键字

AXI4协议;性能优化;故障排除;应用案例;技术演进;并发处理

参考资源链接:[ARM AMBA AXI4协议中文版:最新规格与详解](https://wenku.csdn.net/doc/6412b702be7fbd1778d48c31?spm=1055.2635.3001.10343)

# 1. AXI4协议的基础知识

## 1.1 AXI4协议简介

高级可扩展接口(Advanced eXtensible Interface,简称AXI)是ARM公司开发的一种高性能、高带宽、低延迟的片上总线协议。AXI4作为该系列协议的最新标准,广泛应用于集成电路设计领域,特别是在高性能系统级芯片(SoC)设计中。它是针对FPGA和ASIC设计中的片上通信而专门设计的,尤其适合高速数据传输的应用场景。

## 1.2 AXI4协议的关键特性

AXI4协议的主要特性包括:

- **流式传输**:支持未对齐的传输,允许数据在地址空间中任意开始和结束。

- **突发传输**:支持数据以突发模式传输,提高数据吞吐量。

- **多通道传输**:支持多个独立的读写通道,允许并发操作,提高效率。

- **错误处理**:提供详细的错误响应机制,以应对数据传输中的错误情况。

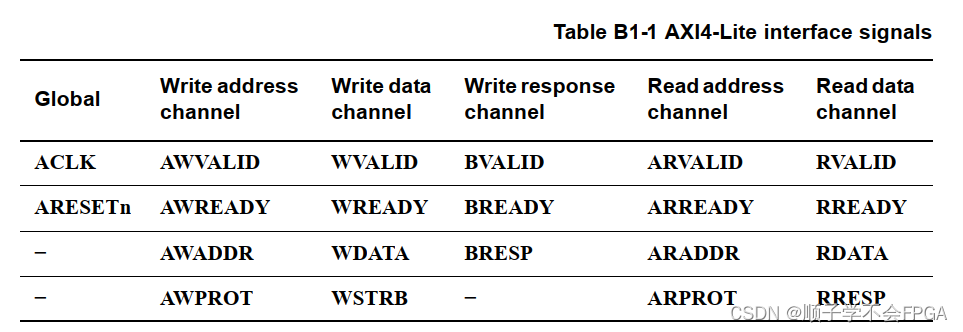

## 1.3 AXI4协议的组成结构

AXI4协议由以下几个关键通道组成:

- **读地址通道(AR)**:用于发起读请求。

- **读数据通道(R)**:用于返回读取的数据。

- **写地址通道(AW)**:用于发起写请求。

- **写数据通道(W)**:用于发送要写入的数据。

- **写响应通道(B)**:用于确认写入成功。

通过这些通道,AXI4实现了复杂的数据传输过程的高效管理。在设计和分析基于AXI4的系统时,深入理解这些通道及其工作方式至关重要。

# 2. AXI4协议性能优化策略

## 2.1 理解AXI4协议的性能瓶颈

### 2.1.1 识别性能瓶颈的方法

在高频率与复杂度的数据交换场景中,AXI4协议的性能瓶颈可能会以多种形态表现出来。比如在FPGA设计中,数据传输可能会出现延迟、吞吐量降低或是功耗上升等问题。识别这些性能瓶颈是性能优化的第一步。

传统性能瓶颈识别主要依赖于模拟仿真与实际硬件测试。利用仿真工具,设计者可以在早期阶段就对AXI4接口的性能进行评估,观察是否有不合理的数据队列延迟或带宽利用不足。而实际硬件测试则更接近最终产品的表现,能提供更真实的性能数据。随着技术的进步,还有其他高级方法如硬件性能计数器(Hardware Performance Counters),JTAG调试,甚至AI驱动的异常检测技术,这些方法能够提供更实时、更准确的性能瓶颈识别能力。

### 2.1.2 性能瓶颈的影响分析

识别出性能瓶颈后,我们需要对它们产生的影响进行分析,以便能够采取适当的措施进行优化。性能瓶颈可能会影响整体系统数据处理的吞吐量,增加处理延迟,影响系统的实时性能,甚至会增加系统的功耗。

一个常见的例子是当AXI4接口的写入通道利用率低时,可能导致写入数据的延迟增加,这会直接影响到数据处理的实时性,特别是在时序敏感的应用中可能成为瓶颈。对带宽利用不足的分析有助于优化缓存策略,减少不必要的内存访问,从而提升性能。

## 2.2 优化数据传输效率

### 2.2.1 传输协议的选择与应用

在AXI4协议中,存在多种传输协议的选择,例如突发传输(Burst Transfers)和单周期传输(Single Cycle Transfers)。对于需要高带宽的应用,突发传输能够减少地址和控制信号的传输次数,从而提高数据传输效率。

使用突发传输时,设计者需要合理规划传输的长度和间隔,以适应系统的需求。例如,在图像处理中,可能需要根据图像数据的大小和处理速度来选择合适的突发长度。代码示例如下:

```verilog

// Verilog代码块

always @(posedge clk) begin

if (burst_start) begin

for (int i = 0; i < BURST_LENGTH; i++) begin

// 在这里进行数据传输的逻辑实现

end

end

end

```

在这个简单的例子中,我们使用了Verilog语言,展示了在一个时钟周期内开始一次长度为BURST_LENGTH的数据突发传输。

### 2.2.2 通道管理与数据缓存策略

通道管理是优化数据传输效率的另一个关键点。合理配置AXI4接口的读写通道数量和类型,可以使数据传输更加高效。例如,为不同的数据流分配独立的读写通道,可以有效减少数据流之间的冲突,提升并发性能。

此外,缓存策略对于数据传输的效率也有着直接的影响。有效的缓存策略能够减少对主存的访问次数,降低延迟。例如,通过预取技术,当读取当前数据的同时,可以从主存中预取下一批数据到缓存中,减少等待时间。

## 2.3 提升接口的并发处理能力

### 2.3.1 并发传输的原理与实践

并发传输是提升接口处理能力的有效手段,尤其是在多任务处理场景中。通过合理地配置AXI4的读写通道,可以在硬件层面上实现数据的并发传输。

实践中,设计者可以通过设置多个读写通道,并让它们独立工作,来提升数据处理的能力。例如,一个通道用于处理视频流数据,而另一个通道用于处理音频流数据,这样可以有效避免相互之间的干扰,同时提升处理效率。

### 2.3.2 流水线技术在AXI4中的应用

流水线技术在提升AXI4接口并发处理能力上有着广泛的应用。通过在数据传输路径中引入流水线级,可以将一次完整的数据处理分解成多个小的处理阶段,让数据在不同阶段并行处理。

例如,可以在AXI4接口中实现一个简单的写入流水线,分为地址阶段、数据阶段和响应阶段。每个阶段可以处理不同的数据传输任务,从而提高整体的数据吞吐量。以下是一个简化的流水线处理伪代码示例:

```c

// C语言伪代码示例

int pipeline_stage = 0; // 流水线当前阶段

void write_transaction(int address, int data) {

switch (pipeline_stage) {

case 0: // 地址阶段

send_address(address);

pipeline_stage++;

break;

case 1: // 数据阶段

send_data(data);

pipeline_stage++;

break;

case 2: // 响应阶段

check_response();

pipeline_stage = 0; // 重置流水线

break;

}

}

```

在实际硬件实现中,流水线的每个阶段通常会由不同的硬件逻辑来处理,并通过状态机等机制来控制流水线的流转。

以上章节详细讲解了AXI4性能优化策略中的关键组成部分,包括识别性能瓶颈、优化数据传输效率,以及提升并发处理能力。在下一章节中,我们将深入探讨AXI4协议在故障排除方面的技巧和方法。

# 3. AXI4协议故障排除技巧

在使用AXI4协议的系统中,故障排除是保障系统稳定运行的关键环节。无论设计多么周密,硬件和软件总可能出现意料之外的问题。因此,深入理解AXI4协议、掌握有效的故障诊断和修复技巧至关重要。

## 3.1 常见故障的识别与诊断

### 3.1.1 故障分类与特征

故障可以分为逻辑故障和时序故障两大类。逻辑故障通常与数据处理和协议规范有关,可能由于逻辑设计错误、资源竞争、数据依赖等问题引起。时序故障则与时钟域、信号同步、路径延迟等问题相关。识别故障特征是故障诊断的第一步,例如:

- **通信错误**:如响应超时、数据不一致、传输序列错乱等。

- **性能下降**:传输速率低于预期、系统吞吐量降低等。

- **资源使用异常**:如资源竞争、过载、死锁等。

### 3.1.2 故障诊断工具与方法

为有效诊断故障,常用的诊断工具和方法有:

- **逻辑分析仪**:用于捕获和分析AXI总线上的信号状态和时序。

- **仿真软件**:使用System Verilog或VHDL等语言进行功能仿真,有助于在硬件实现前发现问题。

- **硬件调试接口**:如JTAG、Debug Core,可以实时监控和调试硬件设备。

- **日志分析**:在软件层面记录关键操作和状态,通过分析日志来追踪问题源。

## 3.2 故障处理与修复流程

### 3.2.1 常规故障的处理步骤

常规故障处理步骤包括:

1. **收集信息**:使用上述工具收集系统的状态信息和日志数据。

2. **分析问题**:根据收集的数据,分析问题出现的可能原因。

3. **建立假设**:根据分析结果建立可能的故障假设。

4. **验证假设**:通过仿真、测试等手段验证各个假设的准确性。

5. **故障定位**:一旦找到可能的原因,通过逐步缩小范围的方法定位问题源头。

### 3.2.2 故障修复后的验证测试

修复后,需要进行严格的验证测试来确保问题确实得到解决,并且修复措施没有引发其他问题。验证测试步骤如下:

1. **单元测试**:对单个模块进行测试,确保其功能正常。

2. **集成测试**:在集成环境中对修复后的模块进行测试。

3. **系统测试**:模拟真实工作场景对系统进行全面测试。

4. **压力测试**:对系统施加超过正常负荷的压力,检验其稳定性和鲁棒性。

## 3.3 防患未然:预防性维护策略

### 3.3.1 定期监控与日志分析

为了防止问题的发生,需要定期监控系统性能和日志信息。可以通过以下方法:

- **实时监控**:使用监控工具实时监测关键指标,如资源使用率、错误率等。

- **日志审查**:定期对日志进行审查,分析异常模式。

- **趋势分析**:分析长期监控数据,预测可能的问题趋势。

### 3.3.2 硬件与软件的维护更新策略

为了保持系统的稳定性和性能,制定适当的维护更新策略至关重要:

- **硬件维护**:定期检查和维护硬件设备,包括清理、升级固件、更换磨损的部件等。

- **软件更新**:根据官方发布的信息及时更新驱动程序、固件和操作系统。

通过有效的故障排除技巧和预防性维护策略,可以确保AXI4协议系统的稳定运行,减少故障发生,提高系统可靠性。在下一章节中,我们将探讨AXI4协议在实际项目中的应用情况,以及如何在具体的工程项目中运用这些故障排除技巧。

# 4. AXI4协议在实际项目中的应用

## 4.1 AXI4协议在FPGA项目中的应用

### 4.1.1 FPGA项目概述与AXI4的角色

现场可编程门阵列(FPGA)是电子系统设计中的重要组成部分,以其灵活性和高性能著称。FPGA可以实现复杂逻辑运算,适合需要高速数据处理和并行计算的应用场景。在这些场景中,AXI4(Advanced eXtensible Interface 4)协议作为高速、高效、灵活的点对点通信协议,成为了连接FPGA内部各种模块的关键接口。

AXI4协议支持突发传输,具备独立的读写地址通道和数据通道,这使得它可以在多主设备环境下实现高效的数据交互。在FPGA项目中,AXI4通常用于连接高性能的处理器核心(如ARM Cortex-A系列)和FPGA逻辑部分。它在FPGA中的角色包括但不限于:

- 高速数据传输:使处理器和FPGA逻辑部分之间可以进行高速数据交换。

- 系统扩展:通过AXI4接口可以方便地扩展更多的外设和功能模块。

- 模块化设计:以AXI4协议为基础的模块可以独立开发、测试并集成到整个系统中。

### 4.1.2 实例分析:FPGA中的AXI4应用案例

为了深入理解AXI4协议在FPGA项目中的应用,我们可以考虑一个常见的图像处理系统。该系统包括一个高性能的处理器核心,多个图像处理模块,以及外部存储接口。在这个案例中,AXI4协议被用于:

- 处理器核心与图像处理模块之间的数据流。

- 图像处理模块与外部存储器之间的高速数据交换。

下面是代码块,展示了一个图像处理模块中使用AXI4协议的简化例子:

```verilog

// Image Processing Unit with AXI4 interface

module ImageProcessingUnit (

// AXI4 Interface

input wire aclk,

input wire aresetn,

// AXI4 Write Address Channel

input wire [31:0] awaddr,

input wire awvalid,

output wire awready,

// AXI4 Write Data Channel

input wire [31:0] wdata,

input wire [3:0] wstrb,

input wire wvalid,

output wire wready,

// AXI4 Write Response Channel

output wire [1:0] bresp,

output wire bvalid,

input wire bready,

// AXI4 Read Address Channel

input wire [31:0] araddr,

input wire arvalid,

output wire arready,

// AXI4 Read Data Channel

output wire [31:0] rdata,

output wire [1:0] rresp,

output wire rvalid,

input wire rready

// ... rest of the signals and logic ...

);

// Image processing logic here

// Write and read channel logic will be implemented here

// according to AXI4 protocol specifications.

endmodule

```

在上述代码中,我们定义了一个名为`ImageProcessingUnit`的模块,它具有AXI4接口。该模块将处理图像数据,并且能够与系统的其他部分通过AXI4进行通信。该模块的实现细节需要遵循AXI4协议的相关规范,包括地址、数据、响应通道的处理。

### 4.2 AXI4协议在SoC设计中的应用

#### 4.2.1 SoC设计概述与AXI4的重要性

系统级芯片(SoC)设计是将处理器、内存、I/O和其他外设集成到单一芯片上的复杂工程。在SoC设计中,AXI4协议的灵活性和高性能为各种组件之间的通信提供了基础。AXI4协议能够满足SoC设计中高性能处理和高效数据传输的需求,特别是在多核处理器和复杂IP(Intellectual Property,知识产权)模块并存的环境下。

AXI4在SoC设计中的角色主要包括:

- 提供高效的IP模块间通信机制。

- 支持多种数据传输模式,包括单个数据传输和突发传输。

- 高级特性,如错误响应和乱序传输,增加了设计的健壮性。

在SoC设计的上下文中,AXI4协议的使用扩展了系统架构的可能性,使得设计者能够利用其协议灵活性来构建高度定制的通信架构。

#### 4.2.2 实例分析:SoC设计中的AXI4实践

以一个多核处理器SoC设计为例,我们通常会看到处理器核心通过AXI4协议与其他多种IP模块相连,包括存储控制器、网络接口、图像处理单元和自定义硬件加速器等。以下是一个简单的例子,描述如何在SoC设计中实现一个AXI4接口的存储控制器:

```verilog

// AXI4 Memory Controller

module AXI4_Memory_Controller (

// AXI4 Interface

// ... (same as previous ImageProcessingUnit)

// Memory interface

output wire [31:0] mem_addr,

output wire mem_en,

output wire [31:0] mem_write_data,

input wire [31:0] mem_read_data,

output wire mem_we

// ... rest of the signals and logic ...

);

// Logic to control memory access through AXI4 interface

endmodule

```

在这个实例中,`AXI4_Memory_Controller`模块代表一个AXI4接口的存储控制器。它负责处理通过AXI4协议与SoC其他模块进行的数据交换,并且控制存储器的访问。这包括发出地址、使能信号、写入数据,并读取数据回传给AXI4主设备。

### 4.3 AXI4协议在高速数据传输系统中的应用

#### 4.3.1 高速数据传输系统特点与挑战

高速数据传输系统如数据中心、存储网络和高性能计算(HPC)环境,对数据传输速度和系统稳定性要求极高。在这些系统中,数据吞吐量和延迟是最关键的性能指标。AXI4协议在这样的环境中扮演着至关重要的角色,因为它支持高频率的传输操作,并且具备了处理突发数据传输的能力。

这些系统面临的主要挑战包括:

- 高带宽需求:随着数据量的增加,系统必须能够提供足够的传输带宽。

- 低延迟通信:对于某些应用来说,延迟是决定性能的关键因素。

- 复杂的数据流管理:处理多路并发数据流,并保证数据的一致性和完整性。

#### 4.3.2 实例分析:高速系统中的AXI4优化技术

为了克服上述挑战,系统设计师需要使用适当的优化技术。例如,在一个数据中心的存储服务器中,为了提高数据处理效率,可以采用AXI4协议的多通道设计来实现数据的并行处理。这样不仅提高了数据吞吐量,也优化了传输延迟。以下是一个简化的代码示例,展示如何实现一个AXI4多通道的通信:

```verilog

// Multi-channel AXI4 communication in High-speed Data Transfer System

module AXI4_MultiChannel_System (

input wire [31:0] channel1_data,

input wire channel1_valid,

output wire channel1_ready,

// ... channel2, channel3, ... inputs and outputs ...

// AXI4 Interface for each channel

// ... AXI4 signals for channel1, channel2, channel3, ...

);

// Logic to handle multi-channel data flow and AXI4 protocol

endmodule

```

在这个代码示例中,我们定义了一个`AXI4_MultiChannel_System`模块,它包含多个数据通道,每个通道都具有独立的AXI4接口。在实际应用中,我们需要为每个通道实现独立的数据处理逻辑,同时满足AXI4协议的要求。这样的设计可以显著提高数据传输效率,特别是在高并发和高带宽需求的应用场景中。

# 5. AXI4协议的未来展望与发展趋势

随着集成电路技术的快速发展,AXI4协议作为高性能接口的重要标准,其未来的发展趋势和技术演进备受行业关注。本章节将深入探讨AXI4协议的技术演进,行业发展趋势,以及持续创新优化的路径。

## 5.1 AXI4协议的技术演进

AXI4协议自发布以来,经历了多个版本的迭代,每次更新都伴随着对性能和灵活性的提升。未来AXI协议的演进将继续在提高数据传输效率、降低延迟和功耗、增加协议的灵活性等方面进行。

### 5.1.1 新版本的AXI协议特性

AXI4的后续版本,例如AXI4-Lite和AXI4-Stream,分别针对低带宽和流式数据传输场景进行了优化。未来的AXI版本可能会更深入地集成AI和机器学习技术的需求,例如提供更高效的广播和多播支持,以及数据压缩机制,以减少对内存和带宽的需求。

### 5.1.2 与其他协议的兼容性分析

随着系统复杂性的增加,不同协议间的兼容性和互操作性变得越来越重要。未来的AXI版本可能会加强与AMBA其它协议,如APB和AHB的兼容性,甚至可能与其他总线或网络协议(如PCIe、USB等)的桥接技术进行整合,以便于构建更为复杂的系统。

## 5.2 行业发展趋势与AXI4的适用性

半导体行业的快速发展为AXI4协议的应用带来了新的机遇和挑战。了解行业的发展趋势有助于我们更准确地评估AXI4协议在未来应用中的适用性和潜力。

### 5.2.1 半导体行业的发展趋势

随着5G、物联网(IoT)、人工智能(AI)、边缘计算等技术的不断发展,半导体行业正在向更高性能、更低功耗、更小尺寸的方向发展。这意味着AXI4协议需要继续优化以适应更小制程、更高集成度的设计需求。

### 5.2.2 AXI4在新应用场景下的适用性探讨

在自动驾驶、数据中心、云计算等新兴应用场景中,对数据处理速度和带宽的要求极为苛刻。AXI4协议以其高速、灵活和易于扩展的特点,能够适应这些场景的需要,但同时需要进一步提升其安全性和可靠性。

## 5.3 持续创新:AXI4协议的持续优化路径

为了保持AXI4协议的竞争力,持续的创新和优化是必不可少的。这一过程中,社区和开源项目将扮演重要的角色。

### 5.3.1 优化路径的探索与实践

探索包括提高协议的能效比、增强协议的测试覆盖和诊断能力,以及引入新的数据传输和管理机制。实践上,这可能意味着需要对现有的FPGA和ASIC设计流程进行优化,以更好地利用AXI4协议的优势。

### 5.3.2 社区与开源项目对AXI4发展的贡献

随着开源硬件和软件的兴起,越来越多的开发者参与到各种硬件设计和协议优化的项目中。社区驱动的开源项目为AXI4协议的测试、应用和优化提供了巨大的推动力。社区可以分享使用经验和最佳实践,开源项目可以提供模块化的硬件设计和协议实现,这些都对AXI4的发展做出了积极贡献。

结合未来技术演进、行业发展趋势以及社区的创新力量,AXI4协议无疑将在未来继续保持其在高性能系统设计中的重要地位,并继续推动半导体行业的进步。

0

0