AXI4与PCIe:通信协议选择指南与性能对比分析

发布时间: 2024-12-21 10:22:37 阅读量: 11 订阅数: 12

基于XDMA核和AXI4协议实现PCIE数据读写(一):工程建立

# 摘要

本文旨在对AXI4与PCIe这两种广泛应用于数字系统设计中的通信协议进行深入探讨。文章首先概述了两种协议的基本概念和理论基础,接着详细解析了它们的关键特征、数据传输机制、性能指标和架构组成。在实践应用方面,文章通过多个实际场景展示了AXI4和PCIe如何被集成到SoC设计、硬件加速器以及高性能计算领域中。性能对比分析章节深入探讨了两种协议在数据吞吐量、延迟、可扩展性、兼容性、功耗和成本效益方面的表现,为实际应用中的选择提供了数据支持。最后,文章提出了选择通信协议的策略,并对未来的协议发展趋势进行了预测,总结了相关领域中的最佳实践和案例研究,为通信协议的未来应用提供了展望。

# 关键字

AXI4协议;PCIe协议;数据传输机制;性能对比分析;通信协议选择;系统集成应用

参考资源链接:[ARM AMBA AXI4协议中文版:最新规格与详解](https://wenku.csdn.net/doc/6412b702be7fbd1778d48c31?spm=1055.2635.3001.10343)

# 1. AXI4与PCIe协议概述

## 1.1 通信协议的演变与重要性

在当今快速发展的信息技术领域,数据传输的效率直接关系到整个系统的性能。随着技术的进步,通信协议也在不断演变,以满足日益增长的性能需求。AXI4(第四代高级可扩展接口)和PCIe(外设组件互连快速版)作为两种主流的通信协议,在众多领域得到了广泛的应用。它们不仅能够支持高带宽和低延迟的数据传输,还能够在硬件设计中提供灵活的互连解决方案。理解这些协议的原理及其在不同场景下的应用,对于优化系统性能至关重要。

## 1.2 AXI4协议基础

AXI4是ARM公司开发的一种高性能的片上系统(SoC)通信协议,它提供了一种简洁的方式来处理IP核间的通信。由于其协议层次的分明和协议头的精简,AXI4已经成为众多高性能芯片设计的首选。它的优势在于提供了高效的读写通道、支持非连续数据传输和传输重排序等特性,这使得AXI4在复杂的硬件设计中能够更加灵活地处理数据流。

## 1.3 PCIe协议简介

PCIe,作为计算机总线接口标准,已经取代了旧式的PCI总线,在现代计算机架构中占据了核心地位。与传统的并行总线技术不同,PCIe使用了点对点的串行连接方式,从而大大提高了数据传输速率,并降低了信号干扰。从PCIe 1.0到当前广泛采用的PCIe 4.0,每次升级都伴随着传输速率的成倍提升,使之能够满足未来技术发展对高带宽的需求。PCIe协议的高扩展性和强大的性能使其成为服务器、数据中心和高性能计算(HPC)领域的核心技术之一。

# 2. 通信协议的理论基础

通信协议是计算机网络中用于设备之间交换信息的标准和约定。它定义了数据如何封装、寻址、传输、解包等过程。本章将深入探讨AXI4和PCIe两种通信协议的理论基础,包括它们的架构、数据传输机制、性能指标以及历史发展和传输特性。

## 2.1 AXI4协议详解

### 2.1.1 AXI4的基本特征和架构

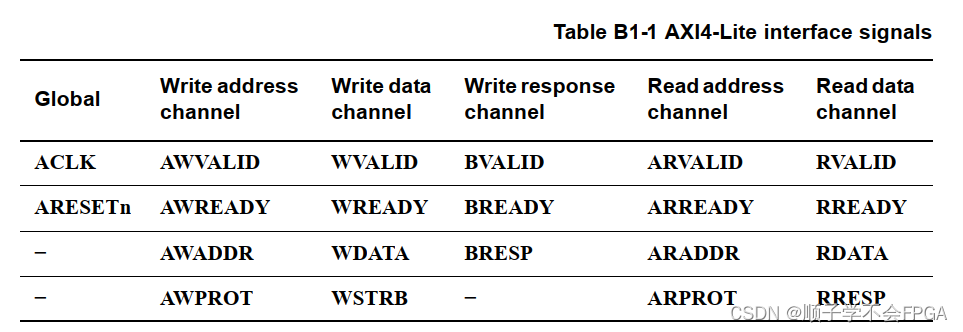

AXI4(Advanced eXtensible Interface version 4)是一种高性能、高带宽的片上通信协议,广泛应用于系统级芯片(SoC)的设计中。AXI4由ARM公司设计,作为其AMBA(Advanced Microcontroller Bus Architecture)系列的一部分,旨在提供高速、低延迟的数据传输。

AXI4的基本架构包括以下几个关键组件:

- **Master Interface**: 发起数据传输请求的接口。

- **Slave Interface**: 接收传输请求并响应的接口。

- **Data Channel**: 用于传输有效载荷数据的通道。

- **Address Channel**: 包含传输数据的起始地址和控制信息的通道。

- **Response Channel**: 用于传输事务完成信号的通道。

每个通道都有独立的信号线,以支持并发数据传输和降低延迟。

### 2.1.2 AXI4的数据传输机制

AXI4支持突发传输和乱序完成事务,以优化数据传输效率。其数据传输机制包括以下几个关键特性:

- **Burst Transactions**: 允许在一个地址传输后连续传输多个数据项,从而减少地址传输的开销。

- **Unaligned Transfers**: 支持非字节对齐的数据传输,增加了数据传输的灵活性。

- **Quality of Service (QoS)**: 通过优先级和流控制机制确保关键数据流能够获得所需的带宽和服务。

- **Split Transactions**: 允许传输被分隔成几个部分,以实现多个主设备间的资源共享。

### 2.1.3 AXI4的关键性能指标

AXI4的设计目标是提供高速的接口,其关键性能指标包括:

- **数据吞吐量**: 通过支持大块突发传输来提高。

- **延迟**: 通过减少协议开销和提供乱序完成的支持来降低。

- **带宽利用率**: 通过优化的传输协议和有效的总线仲裁机制来提高。

- **功耗**: 通过减少不必要的信号切换和设备间的高效率传输来控制。

## 2.2 PCIe协议详解

### 2.2.1 PCIe的历史发展和架构组成

PCI Express(PCIe)是一种高速串行计算机扩展总线标准,旨在替代较老的并行PCI总线。从2002年首次推出至今,PCIe经历了数次版本迭代,包括PCIe 1.0, 2.0, 3.0, 4.0, 5.0,以及未来的6.0版本,每次迭代都在带宽、延迟和效率上有所提升。

PCIe的基本架构包括以下几个层次:

- **Transaction Layer**: 负责处理事务包,包括数据包的构造、路由和错误检测。

- **Data Link Layer**: 确保数据在链路层的正确传输,并提供流量控制。

- **Physical Layer**: 负责物理信号的传输,包括信号的编码、解码和传输介质的相关操作。

### 2.2.2 PCIe的数据传输特性

PCIe使用点对点连接,支持多个高速数据通道,每个通道称为一条“Lane”,每一代PCIe标准都通过增加通道数量和提升每个通道的数据速率来实现更高的带宽。

- **Lane**: PCIe使用一个独特的“Lane”概念,每个Lane由一对差分信号线组成,用于发送和接收数据。

- **Link Width**: 指示连接中Lane的数量,比如x1, x4, x8, x16等。

- **速率升级**: PCIe通过升级每个Lane的数据传输速率来增加整体带宽,例如PCIe 1.0是2.5GT/s,而PCIe 5.0则达到了32GT/s。

### 2.2.3 PCIe的性能参数和优势

PCIe的性能参数不仅体现在其高带宽和低延迟上,还包括了优秀的扩展性和可靠性。PCIe具有以下性能参数:

- **带宽**: 随着标准的升级,PCIe提供从数百MB/s到数十GB/s的带宽。

- **延迟**: 相对于其他总线技术,PCIe具有较低的数据处理和传输延迟。

- **可扩展性**: 支持灵活的Lane数量,便于系统扩展。

- **可靠性**: 提供高级错误检测和纠正机制。

与其他总线技术相比,PCIe具有显著优势:

- **直接连接**: PCIe支持点对点连接,减少了总线仲裁的需要。

- **高带宽**: 随着版本迭代,PCIe的带宽呈指数级增长。

- **电源管理**: PCIe提供更精细的电源管理能力,有助于降低能耗。

本章节的内容详细介绍了AXI4和PCIe两种通信协议的理论基础,包括它们的架构、数据传输机制、关键性能指标,以及各自的历史发展和数据传输特性。通过这些详细的分析,读者可以更好地理解这两种协议如何在硬件设计中发挥作用,以及它们各自的优势和应用场景。

```mermaid

graph LR

A[AXI4]

B[PCIe]

C[SoC设计]

D[服务器和数据中心]

E[高性能计算]

A --> C

B --> D

B --> E

```

请注意,在技术应用与实践的下一章节中,我们将进一步探讨这些协议在实际环境中的应用情况。

# 3. AXI4与PCIe在实践中的应用

## 3.1 AXI4的实际应用场景

### 3.1.1 SoC设计中的AXI4应用

在系统级芯片(SoC)设计

0

0