IMX6ULL第一章:掌握NAND闪存控制器的基本使用

发布时间: 2024-12-16 20:12:59 阅读量: 7 订阅数: 10

imx6ull中文参考手册.pdf

参考资源链接:[NXP i.MX6ULL应用处理器参考手册中文版](https://wenku.csdn.net/doc/3bygm26r9f?spm=1055.2635.3001.10343)

# 1. 掌握NAND闪存控制器的基本使用

在现代电子设备中,NAND闪存控制器扮演着至关重要的角色。作为存储解决方案的核心部件,它管理和优化了与NAND闪存芯片的交互过程。本章将逐步引导读者了解NAND闪存控制器的基本使用方法。

## 1.1 NAND闪存控制器概述

NAND闪存控制器是一种专用集成电路,用于管理和控制NAND闪存的读写操作。它优化数据传输,确保数据完整性,并提供错误检测和纠正功能(ECC)。掌握控制器的使用,是任何涉及高密度存储解决方案项目成功的关键。

## 1.2 控制器的基本操作

要开始使用NAND闪存控制器,首先要进行初始化设置。这包括确定控制器的配置参数,如页大小、块大小和ECC类型。通常,这些设置可以通过硬件接口或软件API进行配置。

```c

// 示例代码:初始化NAND闪存控制器

nandControllerInit(NAND@ControllerConfig *config);

```

上述代码段展示了如何使用假设的C语言API来初始化NAND控制器。`config`是一个结构体,其中包含了所有必要的配置参数。

通过本章的学习,读者将获得足够的知识和工具,来实际操作NAND闪存控制器,并为后续章节中关于控制器的深入讨论打下基础。接下来,我们将深入了解NAND闪存控制器的理论基础,包括它的技术和架构。

# 2. NAND闪存控制器的理论基础

## 2.1 NAND闪存技术概述

### 2.1.1 NAND闪存的工作原理

NAND闪存技术是一种非易失性存储技术,它允许数据在断电后仍然得以保留。NAND闪存的存储单元组成的是二维阵列,而非像NOR闪存那样的树状结构。其基本单元是NAND闪存单元,通过浮栅晶体管(Floating Gate Transistor)实现数据的存储,利用电子在浮栅和控制栅之间的量子隧穿效应实现编程和擦除操作。

工作原理上,NAND闪存单元可以进行位的写入和擦除,但读取操作则以页为单位进行。 NAND闪存的页大小一般为2的幂次方,如512B、2KB、4KB等,块大小则为多个页的总和。在执行写入操作时,必须先擦除整个块,因为NAND闪存结构的限制,它不允许对已写入数据的位进行直接修改。读取操作比NOR闪存慢,但它的高密度存储和成本效益使其成为广泛应用的存储介质,尤其是在固态驱动器(SSD)和嵌入式设备中。

### 2.1.2 NAND闪存与NOR闪存的比较

NAND和NOR闪存都是流行的闪存技术,但在结构和应用上存在显著差异。NOR闪存采用类似于随机存取存储器(RAM)的架构,可以提供快速的随机读取访问,适合存储代码执行,因为它允许单字节访问和执行。NOR闪存的擦写速度相对较慢,成本较高,且密度比NAND低。

NAND闪存提供了更高的数据存储密度,速度快,并且在擦除和写入操作上效率更高。NAND更适合用作大量数据的存储,比如音乐、视频等。但是NAND闪存的随机读取速度较慢,且不能直接执行存储在其中的代码,通常需要一个引导加载器从其他存储设备(如NOR闪存)加载代码到RAM中执行。

## 2.2 NAND闪存控制器的作用与架构

### 2.2.1 控制器在存储系统中的角色

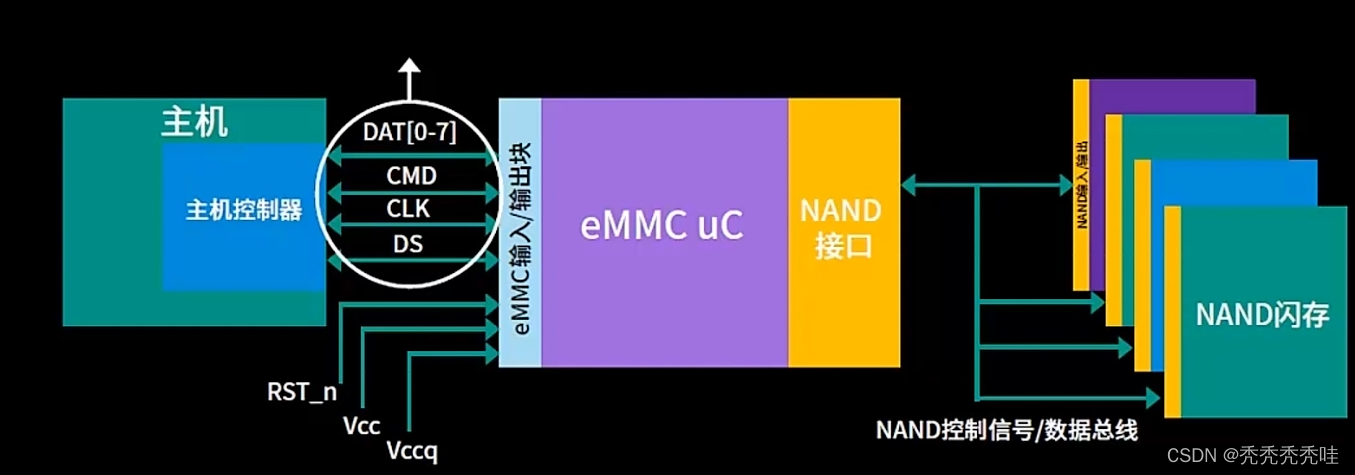

在存储系统中,NAND闪存控制器起到了至关重要的作用。它充当了主机系统与NAND闪存之间的一个智能接口,负责处理所有对NAND闪存的操作命令,管理错误纠正、坏块映射以及页映射等功能。控制器通过硬件电路和固件的配合,极大地提高了NAND闪存的可靠性、性能和寿命。

控制器的主要作用是确保数据正确地写入和读取,处理NAND闪存单元可能出现的位错误,并通过纠错码(ECC)来修正这些错误,从而维护数据的完整性和可靠性。控制器还通过损耗均衡算法来均匀地使用每个块,防止某些块过早磨损,从而延长整个存储系统的寿命。

### 2.2.2 IMX6ULL NAND控制器的内部结构

IMX6ULL是NXP公司的一款流行的微控制器,它包含了NAND闪存控制器的硬件接口。内部结构上,IMX6ULL的NAND控制器包括了命令寄存器、地址寄存器、数据寄存器和状态寄存器等多个寄存器,以及用于管理读写操作和错误检测的硬件电路。

这个控制器支持标准的并行NAND闪存接口,并且具有灵活的块大小和页大小配置。控制器还包括缓冲区,可以用来存储在写入操作中临时写入的数据,以及在读操作中用来暂存从NAND闪存中读取的数据。IMX6ULL的NAND控制器通常还内置了硬件加速器来支持ECC算法的运算,以及支持坏块管理等高级功能。

## 2.3 NAND闪存的接口与性能参数

### 2.3.1 标准NAND接口与电气特性

NAND闪存设备通过一组标准的接口与外部进行通信,这些接口定义了存储设备与控制器之间的电气和信号协议。标准NAND接口包括了数据总线、命令总线、地址总线、控制信号和状态指示信号等。

电气特性方面,NAND接口对信号的电平和时序有严格的要求。例如,标准的并行NAND闪存使用CMOS信号电平,支持多个I/O数据线并行传输数据,提高了数据吞吐率。此外,NAND接口对时序的要求也相当严格,例如对读写操作中的命令、地址和数据的时序都有明确的规定,以确保数据能够准确无误地传输。

### 2.3.2 性能参数及其对系统的影响

NAND闪存的性能参数主要包括读写速度、擦除速度、I/O接口的宽度、页大小、块大小以及存储容量等。这些参数直接影响存储系统的整体性能和效率。

- 读写速度决定了数据可以多快被存取。

- 擦除速度影响了文件删除和更新的效率。

- I/O接口的宽度和页大小决定了并行数据传输的速率。

- 块大小对损耗均衡算法的执行效率和存储空间的管理有重要影响。

- 存储容量自然地影响了能够存储的数据量。

了解这些性能参数对于系统设计者来说至关重要,因为它们将决定使用哪种类型的NAND闪存设备,以及控制器的配置方式。例如,在高性能计算应用中,设计者需要选择高速度的NAND设备并优化控制器配置以减少延迟和提高吞吐量;而在对成本敏感的应用中,则可能更倾向于选择容量大且价格合理的NAND设备。

# 3. NAND闪存控制器的配置与管理

## 3.1 NAND控制器的初始化和配置

### 3.1.1 硬件初始化过程

NAND闪存控制器的硬件初始化是整个NAND闪存系统启动的基础。在这一阶段,控制器将进行自检,确定其硬件功能是否正常,并且准备就绪,以便软件层面可以进行后续的配置和管理。

硬件初始化通常包括以下几个步骤:

1. **上电复位** - 控制器上电后,内部会进行一个复位操作,确保所有寄存器和内部状态机恢复到初始状态。

2. **时钟配置** - 根据系统时钟设置控制器的时钟频率,确保控制器能够与系统同步工作。

3. **GPIO配置** - 配置控制器的通用输入输出(GPIO)引脚,为NAND闪存的接口信号线做好准备。

4. **硬件检测** - 对NAND闪存器件进行硬件检测,如读取ID信息,确认闪存器件的类型和容量。

硬件初始化过程的代码示例(伪代码):

```c

// 伪代码,表示初始化硬件的流程

void nand_controller_hardware_init() {

// 上电复位

reset_controller();

// 设置时钟频率

configure_controller_clock();

// 配置GPIO

setup_gpio();

// 硬件检测

if (!check_nand_device()) {

handle_error("NAND device not found.");

}

// 识别NAND设备信息

identify_nand_device();

}

```

### 3.1.2 软件层面的配置要点

软件层面的配置更加细致,涉及对NAND控制器进行详细设置,以确保其以最佳性能运行。这包括但不限于设置NAND芯片的特定参数、配置坏块管理策略、优化NAND的读写性能等。

软件配置的主要方面包括:

1. **读写时序配置** - 根据NAND闪存器件的特性,设置适当的读写时序,以获得更好的性能和可靠性。

2. **坏块管理** - 激活控制器的坏块管理功能,并设置坏块标记和替换策略。

3. **ECC配置** - 配置错误检测和纠正(ECC)算法的级别,确保数据的完整性。

4. **缓存配置** - 合理配置控制器缓存的使用,提高读写操作的效率。

软件配置的代码示例(伪代码):

```c

// 伪代码,表示软件配置控制器的流程

void nand_controller_software_config() {

// 设置读写时序

set_read_write_timings();

// 启用坏块管理

enable_bad_block_management();

// 配置ECC算法

configure_ecc_algorithms();

// 配置缓存

set_cache_parameters();

}

```

## 3.2 NAN

0

0