【数字IC设计必修课】:从静态到动态功耗,应对新挑战的实战策略

发布时间: 2025-01-03 20:47:40 阅读量: 16 订阅数: 13

# 摘要

数字IC设计的功耗问题是当前半导体行业关注的焦点之一,对于提高集成电路性能和延长便携式设备的电池寿命至关重要。本文从静态功耗和动态功耗两个维度出发,详细讨论了数字IC设计中的功耗问题。通过对静态功耗的机理分析、计算方法和优化技术的研究,以及动态功耗的产生机制、预测分析和控制策略的探讨,文章提出了一系列有效的功耗管理措施。实战案例部分,本文通过分析具体工业级数字IC设计中的功耗挑战,总结了功耗优化流程和方法论,并探讨了在功耗限制下进行创新设计的可能性。最后,文章总结了数字IC设计中功耗管理的现状与挑战,并对低功耗设计技术的发展趋势和未来研究方向进行了展望。

# 关键字

数字IC设计;功耗优化;静态功耗;动态功耗;电源门控;低功耗技术

参考资源链接:[数字集成电路设计 第三章答案 chapter3_ex_sol.pdf](https://wenku.csdn.net/doc/6401aba7cce7214c316e9057?spm=1055.2635.3001.10343)

# 1. 数字IC设计与功耗概述

## 1.1 数字IC设计的重要性

数字集成电路(IC)的设计是现代电子系统的基础,其重要性不容忽视。随着技术的快速发展,对数字IC的要求越来越高,不仅需要具备高性能,还必须在有限的功耗范围内运行。了解数字IC设计和功耗之间的关系,是实现高效、高性能芯片设计的关键。

## 1.2 功耗的分类与影响

在数字IC设计领域,功耗主要分为静态功耗和动态功耗。静态功耗主要来源于晶体管漏电流,而动态功耗则与电路中的信号切换频率相关。过高的功耗不仅会导致芯片温度上升,降低其寿命,还可能引起电源供应问题和电磁干扰。因此,设计时必须充分考虑功耗的影响。

## 1.3 功耗管理策略

有效管理数字IC的功耗需要综合考虑设计、工艺和应用等多方面因素。设计人员在设计初期就要考虑功耗目标,并应用先进的低功耗设计技术和优化手段,如门控电源、多阈值CMOS和动态电压调节等。这有助于确保最终产品在满足性能要求的同时,具有良好的能效比。

# 2. 静态功耗的基础与降低策略

### 2.1 静态功耗的机理分析

#### 2.1.1 静态功耗的定义与来源

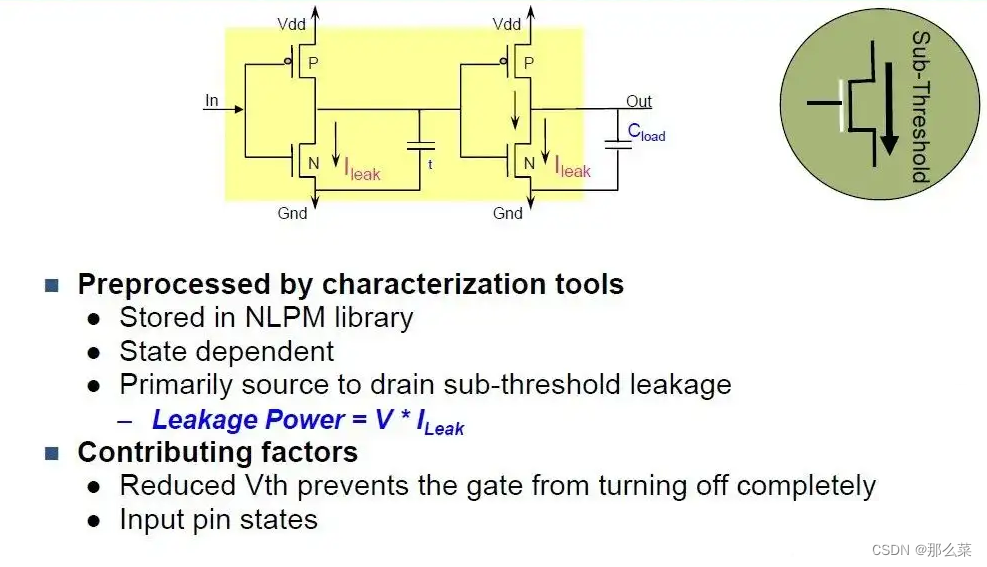

静态功耗,又称漏电流功耗,是在数字电路中,由于晶体管在非活动状态下的漏电流引起的功耗。与由晶体管开关动作产生的动态功耗不同,静态功耗在现代深亚微米工艺中成为了一个重要问题,尤其是在待机模式下。

静态功耗的来源主要是晶体管的亚阈值泄漏、栅漏电流以及PN结反向偏置电流。随着半导体工艺尺寸的减小,晶体管的阈值电压降低,漏电流显著增加,使得静态功耗问题更加突出。特别是对移动设备、物联网设备等需要长期待机的应用,如何有效降低静态功耗成为一个技术难题。

#### 2.1.2 影响静态功耗的关键因素

影响静态功耗的关键因素包括晶体管的物理尺寸、阈值电压、工作温度等。物理尺寸越小,晶体管的漏电问题越严重;阈值电压越低,晶体管在非活动状态下的漏电流越大;工作温度的升高也会导致漏电流的增加。

此外,设计中的一些因素如晶体管的开关状态、电源电压以及电路中晶体管的连接方式也会对静态功耗产生重要影响。例如,未被充分关断的晶体管会形成漏电流路径,导致额外的功耗。

### 2.2 静态功耗的计算方法和评估

#### 2.2.1 静态功耗的理论计算模型

静态功耗的理论计算模型通常以晶体管的漏电流特性为基础。漏电流与晶体管的尺寸、阈值电压、工作电压、工作温度等因素有关,可以使用以下公式进行简化计算:

\[ P_{静态} = I_{leak} \times V_{DD} \]

其中,\( P_{静态} \) 表示静态功耗,\( I_{leak} \) 表示漏电流,\( V_{DD} \) 表示电源电压。更准确的模型会考虑到不同类型的漏电流(亚阈值、栅漏、PN结反向偏置)以及它们之间的相互作用。

#### 2.2.2 实际电路中的静态功耗评估技术

实际电路中的静态功耗评估较为复杂,通常需要借助模拟软件进行。这些软件能够根据电路图和晶体管参数,模拟电路在不同工作条件下的漏电流,从而计算静态功耗。评估流程一般包括以下步骤:

1. 设计电路图,并设置晶体管参数。

2. 使用仿真软件建立电路模型。

3. 在模拟环境中对电路进行静态分析。

4. 测量并记录不同电路节点的漏电流。

5. 将漏电流数据与电源电压相乘得到静态功耗。

### 2.3 静态功耗优化技术

#### 2.3.1 电源门控技术

电源门控技术是一种降低静态功耗的有效手段,通过在芯片上实现电源和地之间的开关,来切断在非活动电路部分的电源,从而减少漏电流路径。其核心思路是在不影响芯片功能的前提下,对不活跃的电路块进行电源切断。

电源门控技术的关键在于合理地设计门控电路,使得在不影响性能的同时,尽可能地降低静态功耗。这就要求在电路设计时必须考虑门控电路的引入对时序的影响,以及如何有效地控制电源门的开启和关闭。

```verilog

// Verilog 示例代码:电源门控控制信号生成模块

module power_gate_controller(

input clk, // 时钟信号

input reset, // 复位信号

input logic_block_enable, // 逻辑块使能信号

output reg power_gate // 电源门控制信号

);

// 控制器状态机的实现,决定何时打开或关闭电源门

always @(posedge clk or posedge reset) begin

if (reset) begin

power_gate <= 1'b0; // 复位时关闭电源门

end else begin

power_gate <= logic_block_enable; // 仅在逻辑块启用时打开电源门

end

end

endmodule

```

#### 2.3.2 多阈值CMOS技术

多阈值CMOS(Multi-Threshold CMOS,MTCMOS)技术通过在同芯片上使用不同阈值电压的晶体管,来降低静态功耗。在MTCMOS设计中,低阈值电压的晶体管用于性能要求较高的关键路径,而高阈值电压的晶体管则用于非关键路径,以此减少整体的漏电流。

高阈值电压晶体管的漏电流相对较低,但开关速度较慢;低阈值电压晶体管则相反。MTCMOS技术的关键在于如何平衡晶体管的开关速度和漏电流,以及在设计中如何有效地在高阈值和低阈值晶体管之间转换。

```verilog

// Verilog 示例代码:多阈值CMOS设计中的晶体管选择

module mtcmos_design(

input clk, // 时钟信号

input logic_path_select, // 逻辑路径选择信号

input [3:0] data_in, // 数据输入

output reg [3:0] data_out // 数据输出

);

// 使用不同阈值的晶体管实现数据路径

// 根据逻辑路径选择信号,选择低阈值或高阈值晶体管路径

always @(posedge clk) begin

if (logic_path_select) begin

// 选择低阈值晶体管路径,高速处理

data_out <= data_in;

end else begin

// 选择高阈值晶体管路径,低功耗处理

// 实现细节略

end

end

endmodule

```

#### 2.3.3 反偏晶体管技术

反偏晶体管技术(Back Biasing)是通过调整晶体管的阈值电压来控制漏电流的一种方法。当在晶体管的衬底和源极之间施加反向偏置电压时,可以增加晶体管的阈值电压,从而减少静态功耗。

通过动态地调节衬底偏置电压,可以在保持性能的同时,减少非活动期间的功耗。然而,这种方法需要在芯片设计中加入额外的电源和控制电路,增加了设计的复杂性。

```mermaid

graph LR

A[开始] --> B[配置电源门控制信号]

B --> C[根据逻辑块启用状态调整门控]

C --> D[采用MTCMOS设计,区分高阈值和低阈值晶体管]

D --> E[动态调整衬底偏置电压以控制漏电流]

E --> F[结束]

```

总结以上,静态功耗的优化是现代数字IC设计中一个重要的技术挑战。通过电源门控、多阈值CMOS技术以及反偏晶体管技术的应用,可以有效降低静态功耗,提高芯片的能效表现。需要注意的是,这些技术的实施需要在电路设计、工艺选择、芯片布局等多个方面进行综合考虑,以确保在不牺牲性能的前提下实现静态功耗的降低。

# 3. 动态功耗的原理与管理

## 3.1 动态功耗的产生机制

### 3.1.1 动态功耗的定义与组成

动态功耗是数字集成电路在运行过程中由于信号切换导致的功耗,主要来源于电路中电容的充放电过程。动态功耗是时钟频率、电容负载以及电压差的函数,可以表示为以下公式:

\[ P_{dynamic} = \alpha \cdot C \cdot V_{DD}^2 \cdot f \]

其中,\( P_{dynamic} \) 表示动态功耗,\( \alpha \) 是开关活动因子,\( C \) 是电路中的等效电容,\( V_{DD} \) 是供电电压,而 \( f \) 是时钟频率。

动态功耗可以进一步分解为由信号切换引起的开关功耗(Switching Power)和由输出驱动引起的短路功耗(Short-circuit Power)。开关功耗与频率成正比,而短路功耗主要发生在CMOS电路中,当PMOS和NMOS同时部分导通时产生。

### 3.1.2 信号切换与充放电过程

在数字IC设计中,信号的切换往往伴随着电路内部电容的充放电。当信号从0变到1或者从1变到0时,电路节点上的电容需要充电到高电平或者放电到低电平。这一过程中,供电电压 \( V_{DD} \) 和地(GND)之间形成了电流路径,导致能量的消耗。

电容的充放电过程可以用简单的RC电路模型来描述,其中R代表电阻(主要是晶体管的导通电阻),C代表电容(包括互连线电容和晶体管门电容等)。在时钟周期内,电容完成充放电,随后在下一个周期开始时重新进行充放电,这一连续的过程在电路中不断重复,形成动态功耗。

## 3.2 动态功耗的预测与分析

### 3.2.1 动态功耗的建模与仿真工具

为了有效地预测和控制动态功耗,开发了多种建模和仿真工具。这些工具通过不同的方法模拟电路在实际运行时的行为,从而估算动态功耗。

建模工具通常使用SPICE(Simulation Program with Integrated Circuit Emphasis)仿真器,它能够对电路进行详细的时域分析。SPICE能够模拟复杂电路的动态响应,并且可以计算出电容的充放电能量,从而得到动态功耗的估算。

仿真工具如Synopsys的PowerArtist和Cadence的Voltus等,它们结合了多种算法和优化技术,能够对电路进行快速动态功耗估算。这些工具能够处理复杂的设计,同时考虑了电路的多种操作模式和条件。

### 3.2.2 动态功耗的实际测量与分析技术

除了仿真工具外,实际测量也是分析动态功耗的重要手段。测量可以使用电流探针、功率分析仪等硬件工具直接对电路板或芯片进行测试。测量技术可以提供实际工作条件下的动态功耗数据,这对于验证仿真结果和优化设计至关重要。

实际测量中,工程师可以通过改变工作频率、电压或者开关活动因子等参数,观察动态功耗的变化情况。这样可以更准确地了解哪些操作条件或设计因素会对功耗产生显著影响。

## 3.3 动态功耗控制技术

### 3.3.1 时钟树优化

时钟树优化是降低动态功耗的有效手段之一。时钟信号是数字电路中的主要能量消耗者,因为它需要在整个芯片范围内分布,且信号切换频繁。

通过优化时钟树设计,可以减少时钟信号的负载电容,减小时钟网络的功耗。此外,引入时钟门控技术可以在不活动的部分电路中关闭时钟信号,从而减少不必要的动态功耗。

### 3.3.2 电压频率调整技术

电压频率调整技术(DVFS,Dynamic Voltage and Frequency Scaling)是一种动态调节芯片工作电压和频率的技术,以适应不同的性能需求和功耗限制。

DVFS根据系统负载实时调整电压和频率,系统负载低时降低电压和频率,系统负载高时则提升电压和频率。这种策略可以显著降低动态功耗,因为功耗与电压的平方成正比。

### 3.3.3 逻辑设计优化

逻辑设计优化同样可以降低动态功耗。具体方法包括使用低功耗标准单元库、减少组合逻辑的深度、优化逻辑门的扇入和扇出等。

低功耗标准单元库提供了特殊设计的单元,这些单元在保持逻辑功能的同时,能够减少功耗。减少组合逻辑深度可以减小电路的传播延迟,减少中间节点的充放电,从而降低动态功耗。

此外,优化逻辑门的扇入和扇出可以减少信号切换的负载,因为扇入和扇出数越多,相应的驱动电容就越大,功耗也随之增加。

```mermaid

graph TD

A[开始优化] --> B[时钟树优化]

B --> C[电压频率调整技术]

C --> D[逻辑设计优化]

D --> E[结束优化]

```

下面是一段示例代码,展示了如何使用DVFS技术在实际电路设计中进行功耗管理:

```verilog

// 伪代码示例:DVFS控制逻辑

module dvfs_controller(

input clk, // 系统时钟

input [3:0] load, // 系统负载指示

output reg vdd_adj, // 供电电压调整信号

output reg freq_adj // 频率调整信号

);

always @(posedge clk) begin

case(load)

4'b0000: begin

// 低负载条件

vdd_adj <= 0; // 减少电压

freq_adj <= 0; // 减少频率

end

4'b1111: begin

// 高负载条件

vdd_adj <= 1; // 增加电压

freq_adj <= 1; // 增加频率

end

default: begin

// 中等负载条件

vdd_adj <= 0; // 保持当前电压

freq_adj <= 0; // 保持当前频率

end

endcase

end

endmodule

```

在实际应用中,DVFS技术通过软件或硬件控制器实现。控制器根据系统负载情况动态地调整电压和频率,以降低功耗。上述代码展示了在不同负载条件下进行电压和频率调整的基本逻辑。

```table

| 功能特性 | 低负载条件 | 中等负载条件 | 高负载条件 |

|----------|------------|--------------|------------|

| 电压调整 | 减少电压 | 保持电压 | 增加电压 |

| 频率调整 | 减少频率 | 保持频率 | 增加频率 |

```

通过上述策略,可以有效地降低数字集成电路在运行过程中的动态功耗,优化整个系统的功耗表现。

# 4. 实战案例:数字IC设计中的功耗优化策略

在现代数字IC设计领域,工程师们面临的一个重要挑战是保证电子设备在提供强大性能的同时,也能够尽可能地降低功耗。这一章节将深入探讨功耗优化的实际案例,并分析其策略和方法。

## 4.1 工业级数字IC设计功耗问题案例分析

### 4.1.1 案例研究:处理器设计中的功耗挑战

处理器作为电子设备的心脏,其性能和功耗比是设计中一个需要权衡的关键因素。在本案例中,我们将探讨一个高性能多核处理器的设计,该处理器在提供强大的计算能力的同时,也面临着严峻的功耗挑战。

处理器设计时,首先要考虑的是电源管理策略。为了降低功耗,采用的策略包括动态电压频率调整(DVFS)、时钟门控和多阈值CMOS技术。DVFS允许在处理任务的轻重之间动态调整核心电压和频率,以达到节能的效果。时钟门控技术通过关闭那些在特定时间内不工作的电路的时钟信号来节约能量。多阈值CMOS技术则是通过使用不同阈值电压的晶体管来降低漏电流和静态功耗。

### 4.1.2 案例研究:移动设备芯片的功耗优化

移动设备由于其便携性和电池供电的特性,对芯片的功耗管理提出了更高的要求。本案例将围绕移动设备芯片的设计,重点关注在保证功能和性能的基础上如何实现更低的功耗。

移动设备芯片设计者通常采用多种策略以实现功耗优化,包括但不限于先进制程技术、精细的功耗控制单元设计以及优化的内存访问策略。先进制程技术可以减小晶体管尺寸,降低工作电压和漏电流。功耗控制单元则负责监控和调整芯片的功耗状态。同时,优化内存访问和缓存设计可以减少不必要的数据读写操作,从而节约能量。

## 4.2 功耗优化流程与方法论

### 4.2.1 从设计到实现的功耗管理策略

功耗管理不应仅仅局限于芯片的物理实现阶段,而应该从设计阶段就考虑进去。在设计初期,工程师需要建立一个全面的功耗模型,以评估不同设计方案的功耗表现。在电路设计阶段,采用低功耗设计技术和工具,如低功耗库、低功耗综合等,可以显著降低芯片的功耗。

在后端实现阶段,需要使用专门的工具来进行功耗优化。例如,通过布局布线优化、单元放置和优化等手段来减少信号的传播距离,降低信号切换导致的动态功耗。同时,保证电路的热设计符合散热要求,避免因过热而导致的功耗增加。

### 4.2.2 功耗分析与优化工具的应用

为了实现有效的功耗管理,使用先进的分析和优化工具是不可或缺的。这类工具不仅可以帮助工程师预测和测量功耗,还可以给出优化建议。

例如,使用功耗仿真工具,可以在电路设计完成前就对功耗进行评估,这包括了静态功耗和动态功耗的模拟。工具如Cadence的PowerArtist和Synopsys的PrimePower提供了从RTL到GDSII的全设计流程的功耗分析能力。此外,工程师还可以通过集成开发环境(IDE)中的功耗视图,直观地了解不同模块的功耗分布,从而有针对性地进行优化。

## 4.3 面向未来:功耗限制下的创新设计

### 4.3.1 新材料与新工艺的探索

新材料和新工艺的发展为解决功耗问题提供了新的途径。例如,使用高迁移率材料如InGaAs替代传统的硅材料,可以有效降低晶体管的功耗。此外,3D集成电路技术通过堆叠多层电路来减少芯片面积,从而降低互连长度和功耗。

另外,纳米线晶体管和石墨烯等新型材料也在研发中,这些材料的导电性能比硅材料高得多,未来有望进一步降低芯片的功耗。

### 4.3.2 异构集成与三维集成电路设计

异构集成是指将不同类型的芯片(如CPU、GPU、内存等)集成在同一封装内,这种方法可以优化数据传输路径,减少延迟和功耗。而三维集成电路设计通过垂直堆叠晶体管和互连结构,可以极大减少芯片内部的数据传输距离,从而降低功耗。

实现异构集成的关键技术包括硅穿孔(TSV)、微凸点(micro-bump)互连等。这些技术有助于提升芯片性能并降低功耗,但同时也带来了设计和制造上的挑战。

通过以上案例分析和方法论探讨,我们了解到了在数字IC设计中,针对功耗优化的一系列策略和技术。这不仅要求工程师们对现有的工艺和材料有深入的理解,还需要不断创新以满足未来技术发展的需求。

# 5. 结论与展望

## 5.1 数字IC设计功耗管理的现状与挑战

在数字IC设计领域,功耗管理一直是一个核心关注点。随着技术的进步,芯片的集成度越来越高,同时功耗也变得日益复杂。当前,设计师们面临着诸多挑战,如如何在满足性能需求的同时降低功耗,以及如何在紧凑的电路设计中实现有效的热管理和电源分配。

目前,我们看到低功耗设计技术有了显著的进步,例如先进的电源门控技术和多阈值CMOS技术的应用,都是在尝试减少静态功耗。然而,这些技术的应用往往伴随着设计复杂性的增加和成本的上升。随着物联网和便携式设备的普及,对于超低功耗设计的需求更是日益迫切,这要求设计团队在功耗管理和性能之间做出更为精细的权衡。

## 5.2 未来趋势与研究方向

### 5.2.1 低功耗设计技术的发展趋势

随着半导体工艺不断向前推进,未来低功耗设计技术将继续朝着更加精细化和智能化的方向发展。比如,在纳米尺度下,量子效应和热效应的影响日益显著,设计者需考虑新的物理效应,探索新型材料如石墨烯,以实现更高的电子迁移率和更低的功耗。

在架构层面,异构集成和三维集成电路设计被认为是缓解互连延迟和降低功耗的有效方法。此外,非挥发性存储技术(如MRAM、RRAM等)的应用也为系统级的功耗优化提供了新的可能性。

### 5.2.2 跨学科合作在功耗优化中的重要性

由于功耗问题的复杂性,跨学科合作变得至关重要。例如,材料科学、电子工程以及计算机科学的交叉合作可以为设计出低功耗高性能的芯片提供更宽广的视角。与此同时,软件优化技术与硬件设计的结合也为降低功耗提供了新的手段。通过软件算法优化任务调度和执行策略,可以有效降低硬件层面的功耗需求。

在未来,我们预见将有更多的研究集中在结合软件层面的功耗管理,使得系统级的功耗优化更加智能化和自动化。同时,随着大数据和人工智能技术的发展,能够处理复杂计算并实现高效功耗管理的算法和架构将变得越来越重要。

### 结语

尽管功耗管理在数字IC设计中已经取得了相当的进展,但是随着技术的进一步发展,这一领域仍然面临着不少挑战。我们需要继续探索和创新,在保持性能的同时进一步降低功耗,以适应不断增长的能源效率和环境可持续性的需求。跨学科合作、新兴材料的应用以及系统级的优化策略,将成为未来功耗管理研究的重要方向。

0

0