【Vivado高级特性深度解读】:设计能力和效率的双重飞跃

发布时间: 2024-12-28 05:03:48 阅读量: 7 订阅数: 9

# 摘要

Vivado是Xilinx公司推出的一款先进的FPGA设计套件,具有模块化设计、IP核集成和高级仿真技术等高级特性,能够有效提升设计效率和质量。本文首先介绍了Vivado的设计方法,包括模块化设计的概念、操作步骤、IP核的定义和作用、以及高级仿真技术的应用。接着,文章详细探讨了Vivado的性能优化策略,包括时序约束、资源优化和功耗优化的理论基础和实践应用。此外,还介绍了Vivado的高级调试技术,如逻辑分析仪和系统分析仪的使用方法。最后,本文展望了Vivado的未来发展趋势,探讨了其在FPGA设计领域的应用前景以及技术升级和改进方向。

# 关键字

Vivado;模块化设计;IP核集成;高级仿真技术;性能优化;高级调试技术

参考资源链接:[Vivado APPN103 PROCISE教程v1.0:章节全面指南与关键设置](https://wenku.csdn.net/doc/5nkafy9r2r?spm=1055.2635.3001.10343)

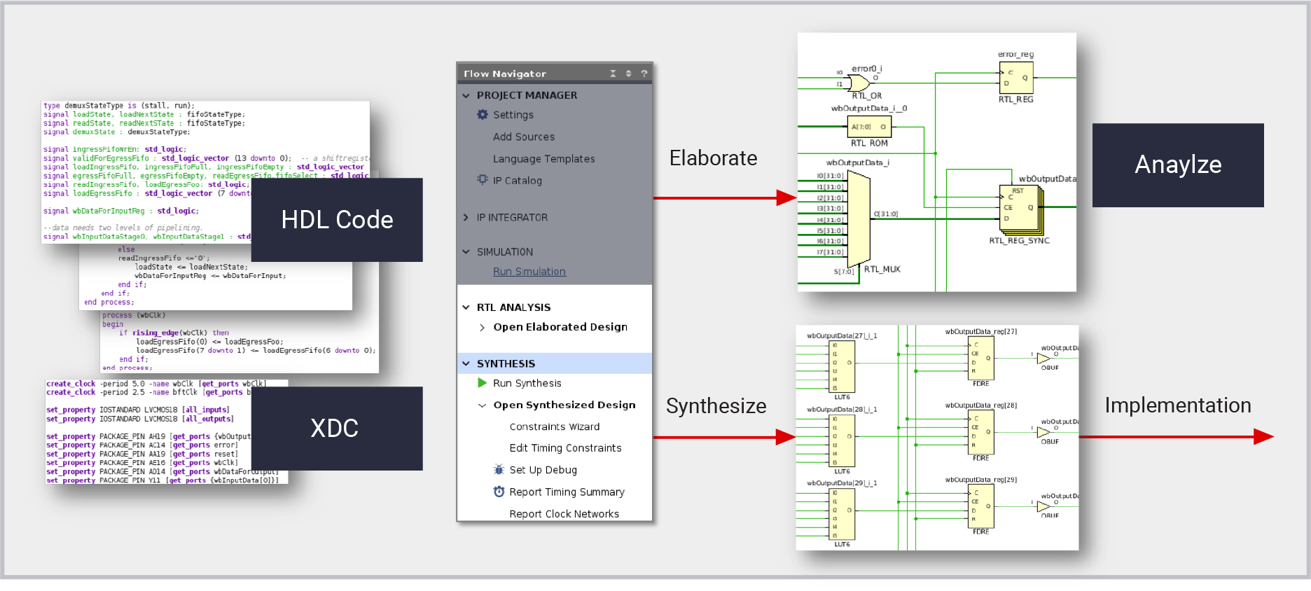

# 1. Vivado高级特性的概述

Vivado是由Xilinx公司开发的一款先进的综合开发环境,它集成了设计、仿真、实现与分析等功能。与以往的ISE工具相比,Vivado采用了基于HDL的全面新一代设计流程,能够显著提高FPGA设计的效率和性能。本章将为读者介绍Vivado的核心高级特性,为深入理解后续章节提供一个坚实的理论基础。

## 1.1 Vivado设计套件的核心优势

Vivado通过其模块化设计、IP核集成、高级仿真、性能优化以及调试技术等多个高级特性,使得FPGA开发流程更加快速、高效和精确。设计人员可以利用这些特性轻松应对复杂的FPGA设计挑战。

## 1.2 Vivado在FPGA设计中的应用范围

Vivado适用于从简单的逻辑设计到复杂的系统级集成设计。它的设计套件支持包括Virtex、Kintex、Artix以及Zynq等多个系列的FPGA产品,因此它在工业、通信、汽车等众多领域都有广泛的应用。

## 1.3 Vivado的未来发展与行业影响

随着电子设计自动化(EDA)技术的不断进步,Vivado也在持续升级,以适应未来的设计需求。从提供更高效的综合算法到优化功耗和时序,Vivado在推动FPGA设计方法的变革中扮演了重要角色。接下来的章节将深入探讨这些高级特性的细节和使用策略。

# 2. Vivado的高级设计方法

## 2.1 Vivado的模块化设计

### 2.1.1 模块化设计的概念和优势

模块化设计是一种将复杂系统分解为多个独立模块的方法,每一个模块完成一个具体的功能,模块间通过定义良好的接口进行通信。在硬件设计领域,模块化设计不仅有助于提高设计的可管理性,还能够通过模块的复用加速整个设计的开发周期。

Vivado支持模块化设计,并将其作为提高设计效率和质量的重要手段。采用模块化设计有以下优势:

- **提高设计的可维护性:** 模块化的代码易于理解和维护,有助于在项目开发过程中快速定位和修复问题。

- **便于团队合作:** 模块化可以让不同的设计团队成员分工明确,同时进行模块设计,大大提升工作效率。

- **设计复用:** 好的模块化设计可以将通用模块集成到不同的项目中,减少重复工作,提高设计效率。

- **可扩展性:** 模块化设计使得系统易于扩展,通过添加或替换模块即可实现系统的升级和功能增强。

### 2.1.2 模块化设计的操作步骤和注意事项

进行模块化设计时,需要遵循一定的步骤和注意一些设计规范。

1. **定义模块接口:** 首先需要明确每个模块的输入输出接口,确保模块间可以准确无误地通信。

2. **划分功能模块:** 根据设计需求将整个设计分解为多个子模块,每个子模块完成一个或几个特定的功能。

3. **设计模块内容:** 独立开发每个模块,对模块内部进行详细设计和实现。

4. **模块集成与测试:** 将各个模块组合起来进行集成测试,确保整体功能符合设计要求。

在进行模块化设计时还需注意:

- **避免模块间的过耦合:** 模块间应该尽可能保持独立,避免相互依赖,降低模块间的耦合度。

- **保持接口一致性:** 保证模块间接口的一致性,如果需要变更接口,应同步更新所有使用该接口的模块。

- **文档的编写:** 详细记录每个模块的功能和使用方法,为后期维护和可能的模块复用提供便利。

## 2.2 Vivado的IP核集成

### 2.2.1 IP核的定义和作用

IP核(Intellectual Property Core)是预先设计并经过验证的电路功能模块,它们可以被直接集成到芯片设计中。IP核类似于软硬件世界的“积木”,允许设计者构建复杂的系统,而不必从零开始设计每一个细节。在Vivado设计环境中,IP核的使用极大提升了设计效率,缩短了产品上市时间。

IP核的主要作用包括:

- **提高设计效率:** IP核的设计和验证通常由第三方或内部专家完成,可以被多次复用,避免了重复劳动。

- **保证设计质量:** IP核通常经过了广泛的验证,可以保证在集成后的工作稳定性。

- **减少研发成本:** 直接使用高质量的IP核可以减少研发时间和人力成本。

- **加快产品上市:** 利用IP核可以迅速完成复杂设计,让产品更快进入市场。

### 2.2.2 IP核的集成和优化方法

在Vivado中集成IP核通常涉及以下步骤:

1. **选择IP核:** 根据设计需求从Xilinx提供的IP目录中选择合适的IP核,或者可以自己创建。

2. **配置IP核:** 对选定的IP核进行配置,设置参数满足设计要求。

3. **生成IP核输出文件:** 根据配置生成对应的HDL文件或者封装的IP核组件。

4. **集成到设计中:** 将生成的IP核输出文件集成到顶层设计中,并按照IP核的接口连接到其他模块。

5. **模拟验证:** 在集成IP核后进行仿真验证,确保设计的正确性。

6. **综合与实现:** 综合和实现整个设计,确保IP核与设计的其余部分协同工作。

为了优化集成的IP核,需要关注以下方面:

- **性能优化:** 根据具体应用需求调整IP核参数,以获得最佳性能。

- **资源优化:** 调整IP核的大小和资源占用,使其适应目标芯片的资源限制。

- **功耗优化:** 如果功耗是关注重点,需要仔细配置IP核的功耗参数,实现功耗的最小化。

## 2.3 Vivado的高级仿真技术

### 2.3.1 高级仿真技术的理论基础

在数字逻辑设计的验证阶段,仿真是一种必不可少的技术。高级仿真技术在传统仿真技术的基础上引入了更复杂的验证手段,如随机测试、断言、形式验证等。

高级仿真技术主要基于以下理论:

- **随机测试(Randomized Testing):** 生成随机数据作为测试输入,能够覆盖更广泛的使用场景。

- **断言(Assertions):** 定义断言用于自动检查仿真运行中某些条件是否满足,可以发现设计中潜在的错误。

- **形式验证(Formal Verification):** 使用数学方法验证设计是否满足特定属性,与仿真相比,形式验证能保证属性在所有可能的输入条件下都成立。

### 2.3.2 高级仿真技术的实践应用

在实际应用中,高级仿真技术涉及的操作步骤和技巧包括:

1. **定义测试计划:** 首先明确测试的目标和范围,确定哪些功能需要被测试,以及对应的测试场景。

2. **编写测试平台(Testbench):** 设计测试平台用来生成输入信号,监视输出信号,并根据断言来验证设计的正确性。

3. **实施随机测试:** 生成随机的输入数据,对设计进行大量的测试,以发现潜在的设计问题。

4. **使用断言验证:** 在测试平台中编写断言,监控设计中的关键信号和条件,以便在违反预期时迅速发现问题。

5. **集成形式验证工具:** 在设计过程中集成形式验证工具,对关键模块进行形式验证,确保其逻辑正确无误。

6. **分析和调试:** 对仿真结果进行分析,当发现不符合预期的行为时,利用仿真工具提供的调试功能进行调试。

以上便是第二章的详细内容。通过模块化设计、IP核集成、以及高级仿真技术的应用,Vivado提供了一整套完整的工具和方法,显著提高了FPGA设计的效率和可靠性。在下一章节,我们将探讨Vivado的性能优化策略,进一步深入理解如何在设计过程中实现性能的极致优化。

# 3. Vivado的性能优化策略

## 3.1 Vivado的

0

0