【Vivado布局布线(LUT)深度解析】:算法背后的秘密

发布时间: 2024-12-28 04:46:57 阅读量: 7 订阅数: 9

基于VGG Simple手写体数字识别 FPGA实现 vivado

# 摘要

本文深入探讨了使用Vivado工具进行FPGA设计中LUT(查找表)的布局布线技术。首先概述了Vivado布局布线的基础知识,然后详细解释了LUT的基础理论,包括其概念、重要性、结构设计以及优化原理。随后,本文介绍了LUT布局和布线的实践技巧,包括布局策略、布线技术和性能分析,以及在布局布线过程中LUT对时序和功耗优化的影响。高级LUT布局布线技术章节讨论了多层次优化技术和LUT在现代FPGA架构中的应用。最后,案例研究与实战章节通过具体实例分析了LUT布局布线的过程,并探讨了自动化与智能技术在实际应用中的潜力。本文为FPGA设计人员提供了一套完整的LUT布局布线方法和策略,旨在优化FPGA设计的性能和效率。

# 关键字

Vivado;布局布线;LUT(查找表);FPGA设计;优化技术;性能分析

参考资源链接:[Vivado APPN103 PROCISE教程v1.0:章节全面指南与关键设置](https://wenku.csdn.net/doc/5nkafy9r2r?spm=1055.2635.3001.10343)

# 1. Vivado布局布线概述

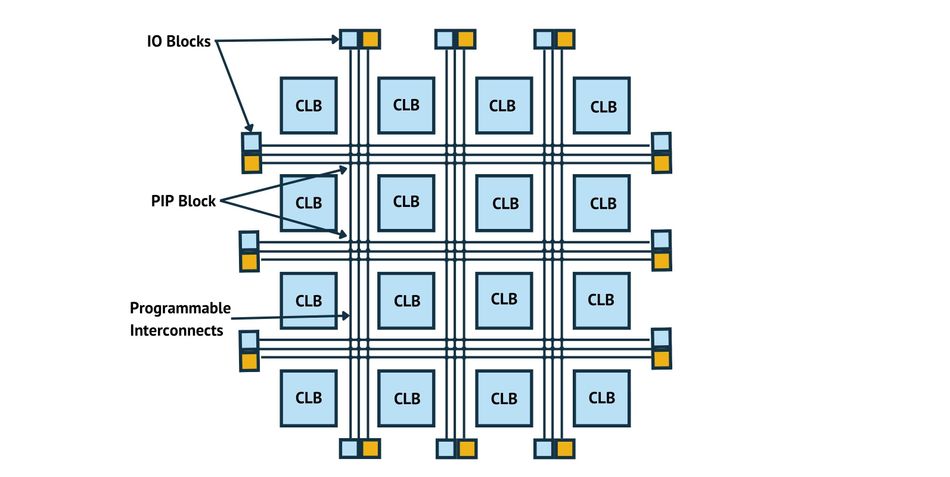

Vivado是由Xilinx公司开发的一款先进综合和实现工具,专注于FPGA和SoC的设计流程,其中包括了布局布线(Placement and Routing)这一关键步骤。布局布线不仅是将设计映射到FPGA硬件资源的过程,更直接影响了最终设计的性能、功耗和可靠性。一个有效的布局布线流程能够保证电路设计在物理芯片上以最优的方式实现,同时满足时序、资源和热特性等多方面的限制。

布局布线过程通常涉及将逻辑单元(如LUTs, 寄存器等)放置到FPGA的物理位置上,并且通过导线将它们正确连接起来。这个过程相当复杂,因为它需要同时考虑成千上万个元件的位置和数百万条路径的布线。为了达到这个目的,Vivado使用了一系列复杂的算法,以优化布局布线的质量和速度。

为了能够更好地理解和应用Vivado布局布线,我们需要先对查找表(LUT)的基础知识有所了解,因为LUT是实现FPGA逻辑功能的核心组件。接下来的章节将深入讨论LUT的概念、结构、优化以及在布局布线中的作用。这将为深入探讨Vivado布局布线提供必要的理论和技术背景。

# 2. ```

# Vivado LUT基础与理论

## LUT的概念与重要性

### 查找表(LUT)的基本定义

查找表(Look-Up Table, LUT)是一种用于实现任意布尔函数的通用数字逻辑元素。在FPGA中,LUT通常被用来实现组合逻辑,它是FPGA实现复杂逻辑功能的基础。LUT的工作原理是将一个或多个输入映射到一个输出。通常,一个k输入的LUT能够存储2^k个可能的输出值。由于其通用性,LUT也支持实现存储功能,如RAM和ROM。

LUT的另一个重要特性是可编程性,允许通过编程来配置查找表中的值。这种可编程性提供了在FPGA内部实现各种逻辑和存储功能的能力,无需改变硬件结构。

### LUT在FPGA中的作用

在FPGA中,LUT是构成逻辑块(Logic Blocks)的基础,这些逻辑块通过可编程互连结构彼此连接。逻辑块通常包含LUT以及用于实现顺序逻辑的触发器。通过编程,LUT可以配置为实现任何逻辑功能,例如逻辑门、解码器、多路复用器或算术函数等。

LUT的使用显著增加了FPGA设计的灵活性,因为同一LUT可以重用多次,在不同的时间实现不同的逻辑功能。这种灵活的重用机制使得FPGA能够在不牺牲性能的情况下,以较小的硬件代价实现复杂电路设计。

## LUT的结构与设计

### LUT的内部结构分析

一个典型的LUT由一个SRAM存储阵列构成,SRAM被用来存储逻辑功能的真值表。对于一个n输入的LUT,有2^n个可能的输入组合,因此LUT包含2^n个存储单元,每个存储单元对应一种输入组合的输出值。

LUT通常还包含一个解码器,用于将输入信号的组合转换为对应的存储单元地址。从解码器到SRAM存储阵列的路径在硬件上是预先固定的,而从SRAM到输出的路径则是可配置的。

LUT的关键性能指标包括延迟、功耗和面积。延迟主要由SRAM读取时间决定,而功耗则受SRAM操作频率和大小的影响。LUT的设计必须在性能、功耗和面积之间找到最佳平衡。

### LUT设计的最佳实践

为了有效地使用LUT,设计者需要了解如何优化其性能。首先,设计者应该尽量减少逻辑级数,因为过多的级数会导致额外的延迟和功耗。其次,应该尝试对LUT进行合并,即将逻辑上相关的函数放入同一个LUT中实现,这样可以减少所需的LUT数量,并改善电路的整体性能。

除此之外,合理地进行资源分配和布局规划也非常关键。Vivado提供了多种设计和优化工具来帮助设计者更好地管理LUT资源。通过合理使用这些工具,设计者能够最大化资源利用率并优化设计性能。

## LUT优化原理

### LUT优化的理论基础

LUT优化的目标是实现更高效的数据流和逻辑功能实现。在理论层面,优化可以通过多种方法实现,包括合并多个小LUT到一个大LUT中,减少逻辑级数以减少路径延迟,以及逻辑重构以减少使用的LUT数量。

LUT优化还涉及到对数据流和信号路径的仔细分析。通过识别关键路径并对其进行优化,可以显著提高设计的整体性能。此外,重复使用LUT来实现多个逻辑功能,可以减少资源的浪费并提高芯片利用率。

### LUT优化在布局布线

```

0

0