【Multisim仿真深度探索】:半加器和全加器构建的奥秘

发布时间: 2025-01-06 11:47:02 阅读量: 10 订阅数: 11

# 摘要

本文从数字逻辑的基础讲起,系统介绍了数字加法器的设计、构建及优化技术。首先,阐述了数字逻辑基础和加法器的基本概念,然后深入探讨了半加器和全加器的设计原理及其在仿真软件Multisim中的实现与测试。文章详细分析了全加器在数字系统中的应用,特别是在算术逻辑单元(ALU)中的作用以及其在复杂运算中的应用案例。最后,讨论了高级数字设计中对加法器进行优化的理论与方法,通过案例研究展示了优化前后的性能对比,为数字逻辑设计提供了深入的见解和实用的优化策略。

# 关键字

数字逻辑;加法器设计;Multisim仿真;ALU集成;故障诊断;电路优化

参考资源链接:[Multisim数电仿真实验:半加器与全加器逻辑功能分析](https://wenku.csdn.net/doc/6401ac10cce7214c316ea802?spm=1055.2635.3001.10343)

# 1. 数字逻辑基础与加法器概念

数字逻辑是构建现代计算系统的基础,其核心在于如何使用逻辑门来实现复杂的逻辑运算。加法器作为数字电路中的基本构件,是理解数字逻辑设计的一个绝好切入点。本章节将由浅入深地介绍数字逻辑的基础知识,并探讨加法器的基本概念及其在数字系统中的重要性。

## 1.1 数字逻辑的组成

数字逻辑主要由基本的逻辑门组成,如与门(AND)、或门(OR)、非门(NOT)等。这些门电路可以组合成更复杂的逻辑功能,为构建各类数字设备提供可能。

## 1.2 加法器的定义和功能

加法器是一种数字电路,用于执行两个数字之间的加法运算。它不仅能够处理单个位的加法,还可以扩展到多位数字的加法处理。加法器是算术逻辑单元(ALU)的关键组成部分,广泛应用于各种数字系统中。

在接下来的章节中,我们将深入探讨加法器的设计和优化,以及它在数字系统中的具体应用。通过对加法器的设计与实现过程的解析,读者将能够更好地理解数字电路设计的原理和实践。

# 2. 半加器的设计与实现

## 2.1 半加器的工作原理

### 2.1.1 逻辑门的功能及应用

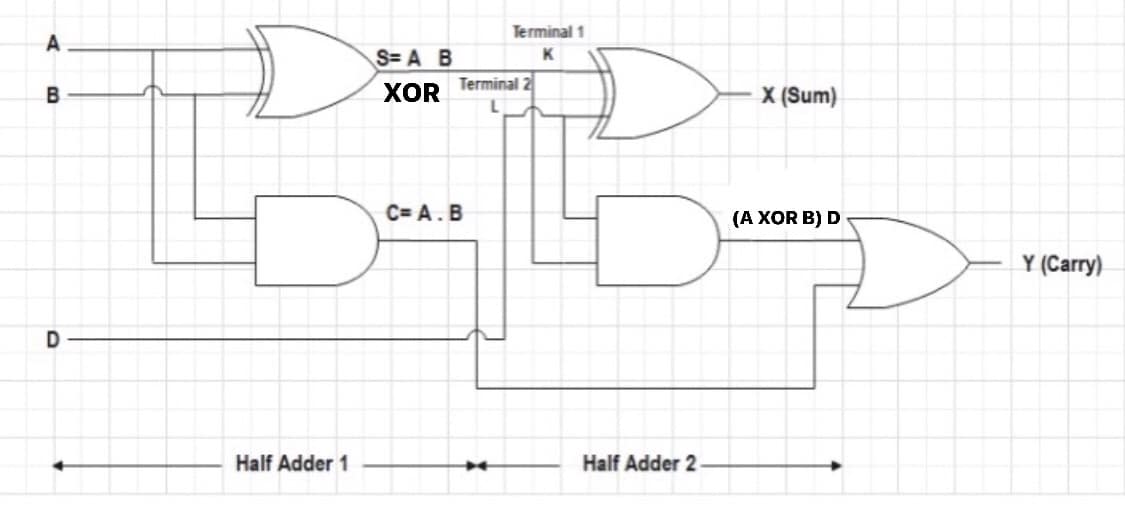

逻辑门是数字电路设计中最为基础的组件,它们实现各种布尔逻辑运算。在半加器的设计中,最常见的逻辑门包括AND门、OR门和XOR门。XOR门(异或门)用于产生半加器的和输出,因为它能够在输入不同时输出1,在输入相同时输出0。AND门用于产生半加器的进位输出,只有当两个输入都为1时才产生输出。

### 2.1.2 半加器的逻辑表达式和真值表

半加器由两个输入组成,分别是A和B,输出为两个:和(S)和进位(C)。其逻辑表达式可以表示为:

- S = A ⊕ B (A XOR B)

- C = A · B (A AND B)

下面是对应的真值表:

| A | B | S (和) | C (进位) |

|---|---|--------|----------|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

## 2.2 半加器的Multisim仿真实践

### 2.2.1 Multisim软件简介及界面布局

Multisim是一款电路仿真软件,用于电路设计和功能验证。界面布局主要包含以下几个部分:

- 元件栏(Component Toolbar):用于选取和放置电路元件。

- 电路工作区(Circuit Workspace):绘制电路图并进行仿真。

- 原理图工具栏(Schematic Toolbar):包含绘图所需的工具和功能。

- 调试工具栏(Simulate Toolbar):执行仿真和监控电路响应。

### 2.2.2 半加器仿真电路的搭建与调试

为了在Multisim中搭建半加器,需遵循以下步骤:

1. 打开Multisim软件并创建新的项目。

2. 从元件栏中找到并放置两个开关,代表输入A和B。

3. 同样从元件栏中找到并放置一个XOR门和一个AND门,分别用于计算和输出和进位。

4. 放置两个LED灯作为输出指示器,一个连接到XOR门输出,另一个连接到AND门输出。

5. 连接好所有元件后,双击开关和LED灯进行配置。

6. 运行仿真,通过切换开关的开闭状态,观察LED灯的变化来验证半加器功能。

## 2.3 半加器的优化与扩展

### 2.3.1 电路优化方法

电路优化是提高电路性能和降低功耗的重要手段。对于半加器来说,优化可以从以下几个方面进行:

- 减少延迟:优化路径,减少关键路径的逻辑门数量。

- 降低功耗:使用低功耗逻辑门,减少不必要的开关动作。

- 减少面积:通过简化电路布局,减少占用的物理空间。

### 2.3.2 半加器到多米诺电路的转换

多米诺电路是一种动态电路,它使用电容来存储逻辑状态,具有速度快,功耗低的特点。将半加器转换为多米诺电路涉及以下步骤:

1. 识别半加器中关键的逻辑门路径。

2. 将这些路径用动态逻辑门替换,如多米诺NAND门。

3. 对电路进行仿真,确保在动态条件下,电路依然稳定工作。

4. 分析电路性能,如功耗和速度,根据需要调整电路设计。

接下来,为了更好地阐述这些优化方法,我们将详细展示优化过程中的实际操作和代码逻辑分析。

# 3. 全加器的构建与分析

## 3.1 全加器的工作原理

### 3.1.1 超前进位的概念与优势

在数字电路设计中,全加器是一种能够实现二进制数加法运算的基础组件,它可以处理三个输入——两个加数位以及一个进位输入,

0

0