【SPI信号回流布线策略】:高速PCB设计的布局艺术

发布时间: 2025-01-09 23:42:16 阅读量: 5 订阅数: 11

EDA-USB_SPI_FLASH-设计与实现.zip

# 摘要

本论文深入探讨了SPI(串行外设接口)信号在高速PCB(印刷电路板)设计中的应用,重点分析了SPI信号的基础理论、布线要求和回流布线的实践技巧。通过对SPI通信协议的解析、电气特性的讨论,以及布线要求的概述,为设计者提供了在高速PCB设计中确保SPI信号质量的基础知识。进一步通过案例研究和实践技巧的介绍,揭示了在实际布线过程中可能遇到的问题及其解决策略。本研究还讨论了设计中遇到的挑战和应对策略,并对高速PCB设计的未来趋势和创新方向进行了展望。

# 关键字

SPI信号;高速PCB设计;通信协议;信号完整性;回流布线;设计挑战

参考资源链接:[高速PCB设计:SPI与信号、电源完整性的挑战](https://wenku.csdn.net/doc/6412b4c8be7fbd1778d40ced?spm=1055.2635.3001.10343)

# 1. SPI信号与高速PCB设计概述

## SPI信号与高速PCB设计的关系

串行外设接口(SPI)是一种常用的通信协议,它允许微控制器(MCU)与各种外围设备进行高速数据交换。在高速印刷电路板(PCB)设计中,如何有效地实现SPI信号的布线至关重要,因为这直接关系到设备的性能和可靠性。

## 高速PCB设计面临的挑战

随着电子设备运行速度的日益加快,高速PCB设计中的信号完整性问题变得更加突出。高速信号传输过程中可能会遇到的电磁干扰(EMI)、串扰、反射和同步问题,都需要在设计阶段考虑并妥善解决。良好的SPI布线策略可以帮助缓解这些问题,保证信号在高速传输时的稳定性。

## SPI信号设计的重要性和影响

正确处理SPI信号的布线不仅有助于提高数据传输效率,还能减少错误和故障的发生。因此,在高速PCB设计中,SPI信号的设计和优化是一个不可忽视的环节。接下来的章节将深入探讨SPI信号的基础理论和实践技巧,帮助设计师有效地实现SPI回流布线,提升高速PCB的整体性能。

# 2. SPI信号的基础理论

## 2.1 SPI通信协议解析

### 2.1.1 SPI协议的工作原理

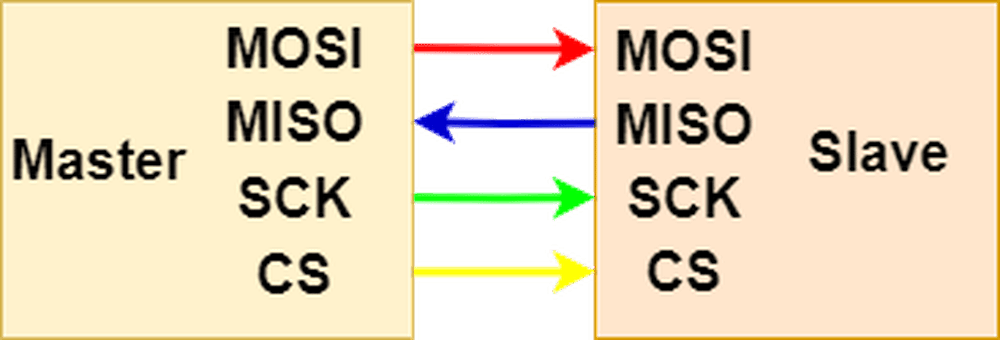

SPI(Serial Peripheral Interface)是一种广泛使用的串行通信协议,它允许一个主设备通过一个单一的主控制器与一个或多个从设备进行通信。SPI通信包括四个信号线:SCLK(Serial Clock)、MOSI(Master Out Slave In)、MISO(Master In Slave Out)和CS(Chip Select)。

SPI协议的工作原理如下:

- **初始化阶段:** 在通信开始前,主设备通过CS信号选择从设备,并将其置为低电平。

- **数据传输阶段:** 主设备开始产生时钟信号SCLK,同时通过MOSI线向从设备发送数据。从设备在相同的时钟信号下通过MISO线向主设备发送数据。

- **结束阶段:** 一旦数据传输完毕,主设备通过将CS信号置回高电平来结束通信。

SPI协议的特点包括:

- **同步通信:** SPI使用时钟信号来同步数据传输。

- **全双工通信:** 数据可以在两个方向同时进行传输。

- **多从设备支持:** 通过控制CS信号,主设备可以与多个从设备通信。

### 2.1.2 SPI的时钟极性和相位设置

SPI协议定义了四种时钟模式,由时钟极性(CPOL)和时钟相位(CPHA)决定:

- **CPOL=0, CPHA=0:** SCLK在空闲状态时为低电平,数据在SCLK的上升沿采样,在下降沿变化。

- **CPOL=0, CPHA=1:** SCLK在空闲状态时为低电平,数据在SCLK的下降沿采样,在上升沿变化。

- **CPOL=1, CPHA=0:** SCLK在空闲状态时为高电平,数据在SCLK的下降沿采样,在上升沿变化。

- **CPOL=1, CPHA=1:** SCLK在空闲状态时为高电平,数据在SCLK的上升沿采样,在下降沿变化。

正确设置时钟极性和相位对于保证数据同步和正确传输至关重要。不同的从设备可能需要不同的SPI时钟模式,设计时需要根据具体的设备数据手册来进行配置。

## 2.2 SPI信号的电气特性

### 2.2.1 信号完整性基础

信号完整性是指信号在传输过程中保持其质量,避免由于电气特性不良而引起的信号失真。对于SPI信号而言,信号完整性主要涉及以下几个方面:

- **信号传输速度:** 高速传输可能导致信号的上升和下降边缘变得模糊,影响数据的准确性。

- **反射:** 信号在传输路径上的不连续点,如连接器或过孔,会产生反射,可能导致信号电平的错误。

- **串扰:** 高速信号线相互靠近时,一条线路的信号可以影响到另一条线路,引起串扰。

- **同步:** 在多信号传输中保持同步是非常重要的,信号之间的时序偏差可能导致数据错误。

### 2.2.2 信号的反射、串扰和同步问题

**反射:** 当信号在传输线的终端遇到阻抗不匹配时,一部分信号会被反射回源端。为了避免反射,设计时需确保整个传输路径的阻抗连续性,通常维持在50欧姆。

**串扰:** 预防串扰的方法包括增加信号线的间距、使用地平面隔离、以及合理设计信号的回流路径。

**同步:** 保持信号同步涉及到时钟管理,包括时钟树的设计和时钟源的选择。在SPI通信中,通常由主设备提供时钟信号,因此保证时钟信号到达所有从设备的同步非常重要。

## 2.3 SPI信号的布线要求

### 2.3.1 布线的基本准则

SPI信号布线应遵循以下基本准则以确保信号完整性:

- **阻抗匹配:** 为了减少信号反射,应保持整个传输线的阻抗连续,通常目标阻抗为50欧姆。

- **布线长度控制:** 确保布线长度尽可能短,以减少信号衰减和延迟,特别是在高速信号传输中。

- **避免环路和长线:** 长的信号线容易引入噪声和串扰,应尽量使用短连接,并避免形成天线效应。

- **信号回流路径:** 确保信号有清晰的回流路径,特别是在多层板设计中,这通常意味着良好的地平面设计。

### 2.3.2 高速信号的回流路径设计

高速信号的回流路径设计是保证信号完整性的重要环节。设计时需注意以下几点:

- **地平面的使用:** 在多层PCB设计中,使用连续的地平面可以为高速信号提供清晰的回流路径。

- **信号层与地平面的配对:** 在信号层与相邻的地平面之间,应尽可能减少距离以提供更好的回流路径。

- **电源平面的考虑:** 如果回流路径跨过电源平面,则应确保电源平面的完整性,避免在信号回流路径上形成意外的阻抗变化。

SPI信号的布线设计是一个复杂的工程,要求设计者不仅要有扎实的电子基础知识,还需要充分理解高速电路的物理特性和实际应用条件。下一章节,我们将探讨SPI信号回流布线的实践技巧,进一步深入理解如何在实际工作中设计和优化SPI信号布线。

# 3. SPI信号回流布线的实践技巧

## 3.1 设计前的准备工作

### 3.1.1 PCB设计软件的选择和配置

在进行SPI信号回流布线之前,选择合适的PCB设计软件至关重要。现代高速PCB设计通常依赖于专业的EDA(电子设计自动化)工具,例如Altium Designer、Cadence Allegro、Mentor Pads等。这些工具不仅支持复杂的电路设计,还具备信号完整性分析、电磁兼容性(EMC)仿真等功能。

选择软件后,配置设计环境以满足SPI信号的特殊需求是下一步。例如,在Alti

0

0