实时神经网络推理:硬件加速器的选择与应用

发布时间: 2024-09-06 08:09:01 阅读量: 310 订阅数: 103

面向卷积神经网络的硬件加速器设计方法.pdf

# 1. 实时神经网络推理简介

## 1.1 什么是实时神经网络推理

实时神经网络推理是指利用深度学习模型在接收到输入数据的瞬间,快速输出处理结果的过程。这一技术在需要快速响应的应用中尤为关键,如自动驾驶、智能监控、实时语音翻译等场景。实时推理的效率直接影响着用户体验和系统的响应速度。

## 1.2 实时推理的重要性

在现代信息技术中,时间成本等同于经济成本。高效率的实时推理可以大大提升机器学习算法的实用性和商业价值。比如,能够在毫秒级别对交易进行风险评估,或将大大减少金融欺诈行为。实现快速响应,要求神经网络模型不仅准确率高,而且执行速度快。

## 1.3 实时推理面临的挑战

实现实时推理并非易事。除了需要优化的算法本身之外,还需考虑硬件的处理能力,以及软件与硬件的协同工作能力。随着模型规模的增大,数据量的增加,对计算资源的要求也随之增加。如何在保证精度的前提下,提高推理速度,是实时神经网络推理要解决的核心问题。在下一章,我们将探讨实现神经网络推理硬件加速的理论基础。

# 2. 神经网络推理硬件加速器的理论基础

### 2.1 硬件加速器概述

硬件加速器是一种专用的处理器,设计用于执行特定的计算任务,以加快运算速度并提高能效。它们通常被集成到计算机系统中,以辅助或替代CPU执行某些计算密集型操作。

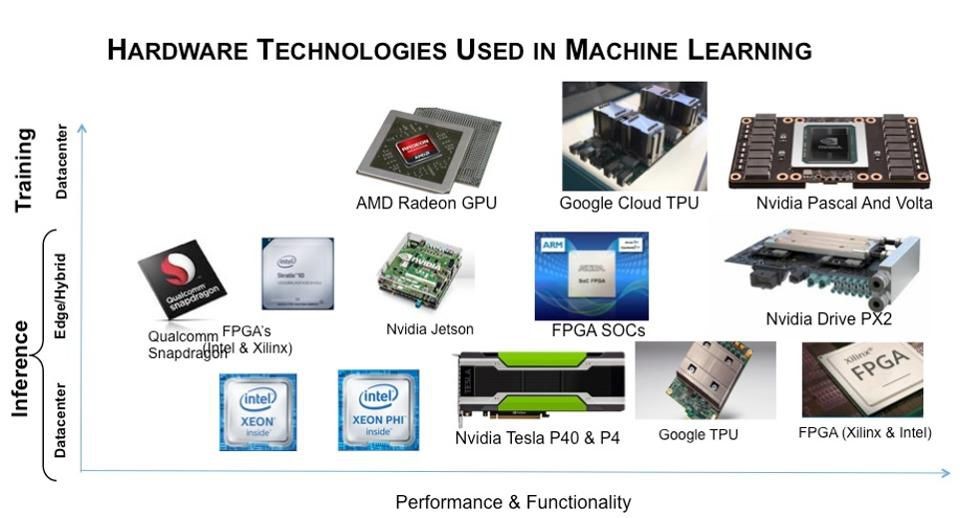

#### 2.1.1 加速器的定义与分类

硬件加速器的定义可以基于它们所加速的应用类型进行分类。例如,GPU(图形处理单元)最初设计用于处理图形和视频渲染任务,现在也被广泛应用于科学计算和机器学习领域。另一种是ASIC(应用特定集成电路),它是为了特定应用而设计的定制化硬件。最后,FPGA(现场可编程门阵列)是介于两者之间的技术,它提供了比ASIC更高的灵活性,同时比GPU或CPU更快地执行某些特定计算任务。

#### 2.1.2 硬件加速器的优势分析

与通用处理器相比,硬件加速器的优势在于其针对特定任务的优化。例如,FPGA能够提供比传统处理器更高的性能和效率,因为它们能够在硬件级别对特定的计算任务进行优化。ASIC提供了最佳的性能和能效比,但其开发成本高且开发周期长。GPU在处理大规模并行任务时表现出色,因此在深度学习和图形处理领域被广泛应用。通过使用这些加速器,计算密集型应用可以在保持较低能耗的同时,实现快速的数据处理和分析。

### 2.2 关键技术探讨

#### 2.2.1 数据并行处理技术

数据并行处理是现代硬件加速器的一项关键技术,特别是对于神经网络推理任务来说至关重要。在数据并行模式中,输入数据被分割成小块,并且每个数据块被并行处理。通过这种方法,多个处理器可以同时处理数据的不同部分,显著减少了计算时间。在神经网络中,这通常意味着单个模型的不同部分可以并行推断多个输入数据。

#### 2.2.2 指令集优化与定制

为了进一步提升性能,许多硬件加速器对指令集进行优化和定制。这使得加速器能够更高效地执行特定的数学运算和数据操作。例如,深度学习专用指令集(如TensorCore在NVIDIA的GPU中)可以加速矩阵运算,这对于神经网络中的权重矩阵乘法至关重要。指令集的优化不仅提高了计算速度,还降低了能耗,这对于构建高效的神经网络推理系统至关重要。

### 2.3 硬件加速器在神经网络中的应用

#### 2.3.1 神经网络模型与加速器的匹配

针对神经网络的硬件加速器设计,需要考虑到模型的特点,如层数、参数量和计算密度。不同的神经网络模型对硬件加速器的要求不同。例如,卷积神经网络(CNN)需要大量的矩阵乘法和加法运算,而循环神经网络(RNN)则更多地依赖于时间序列数据的处理能力。因此,在选择或设计硬件加速器时,需要考虑到这些差异,以保证最佳的性能和资源利用。

#### 2.3.2 能效与性能的权衡

在设计和使用神经网络硬件加速器时,必须在性能和能效之间找到适当的平衡点。虽然GPU提供了极高的性能,但它们在能效方面通常不如专为深度学习任务定制的ASIC或FPGA。在一些需要高性能计算但能源供应有限的场景(如移动设备或远程传感器)中,能效尤为重要。因此,在设计加速器时需要对性能和能效进行综合考量,以满足不同应用的需求。

在此章节中,通过深入探讨硬件加速器的定义、分类、优势、数据并行处理技术、指令集优化以及在神经网络推理中的应用,我们为理解其在实时神经网络推理中的重要性奠定了基础。下一章将分析主流的硬件加速器技术,如FPGA、GPU和ASIC,以及它们在实际应用中的表现。这将为我们提供一个全面的视角来评估在特定场景下哪种加速器能够提供最优的解决方案。

# 3. 主流神经网络推理硬件加速器分析

在这一章节,我们将深入探讨目前主流的神经网络推理硬件加速器,包括FPGA、GPU和ASIC加速器。每个加速器都有其独特的技术特点和应用场景,本章将对这些进行详细分析,揭示它们在神经网络推理任务中的优势和挑战。

## 3.1 FPGA加速器

### 3.1.1 FPGA加速器的工作原理

现场可编程门阵列(Field-Programmable Gate Array,简称FPGA)是一种通过编程可配置的硬件设备。FPGA的工作原理基于其具有可编程逻辑块,这些逻辑块可以根据用户需求重新配置。FPGA可以实现在硬件级别上定义数据处理逻辑,这意味着它们可以高度优化特定算法的执行。

FPGA加速器特别适合实现数据流并行处理和低延迟的实时应用。它们能够提供极高的定制化程度,但同时,编程FPGA比通用处理器复杂得多,需要利用硬件描述语言(如VHDL或Verilog)进行设计。

### 3.1.2 FPGA在推理中的应用案例

在实际应用中,FPGA广泛应用于深度学习推理任务,尤其是当推理过程需要高吞吐量和低延迟时。

0

0