【性能优化】:DMA_Bridge子系统的调试与分析必修课

发布时间: 2024-12-21 10:17:56 阅读量: 7 订阅数: 12

dma_bridge_verilog.rar_Bridge_DMA仿真_dma_dma arb_dma verilog

# 摘要

DMA_Bridge子系统作为现代计算机系统中重要的数据传输和管理组件,其性能直接关系到系统整体效率。本文首先对DMA_Bridge子系统进行了基础介绍和理论分析,包括其工作机制、关键技术与算法,以及性能分析的基本方法。接着,深入探讨了DMA_Bridge子系统可能遇到的性能瓶颈,并提出了性能优化策略,通过具体案例分析了优化过程和效果。文章还提供了DMA_Bridge子系统的调试技巧,帮助开发者高效定位问题。最后,文章展望了DMA_Bridge子系统未来的研究方向和应用前景,强调了其在未来计算机架构中的潜在影响力。

# 关键字

DMA_Bridge子系统;调度算法;缓存一致性;性能分析;性能优化;调试技巧

参考资源链接:[PCI Express v4.1 XDMA 学习笔记:DMA桥接子系统解析](https://wenku.csdn.net/doc/644b7a5afcc5391368e5ee07?spm=1055.2635.3001.10343)

# 1. DMA_Bridge子系统基础介绍

## 1.1 DMA_Bridge子系统概述

DMA(Direct Memory Access)Bridge子系统是现代计算机系统中的关键组件,它主要负责在系统不同组件间提供高速数据传输通道。具体来说,DMA_Bridge允许外围设备直接与主内存进行数据交换,减少了CPU的参与,从而提高了数据传输的效率。

## 1.2 DMA_Bridge的作用

在多核处理器和高速外围设备普遍应用的今天,DMA_Bridge的作用愈发凸显。它不仅降低了CPU的负载,还减少了因数据传输导致的系统延迟,使计算机系统在处理大量数据时更加高效。

## 1.3 DMA_Bridge的应用场景

DMA_Bridge广泛应用于网络通信、存储设备、高性能计算等领域。在这些场景下,DMA_Bridge可以有效地提高数据传输速度,保证系统的稳定性和实时性。

通过以上三个小节的介绍,我们对DMA_Bridge子系统有了一个基础的了解。接下来,我们将深入探讨其工作机制和理论基础。

# 2. DMA_Bridge子系统的理论基础

## 2.1 DMA_Bridge子系统的工作机制

### 2.1.1 DMA_Bridge的工作原理

Direct Memory Access (DMA) 是一种允许硬件子系统直接读写主内存的技术,而无需CPU的干预,从而释放CPU资源进行其他任务处理。DMA_Bridge是DMA技术的一个扩展,主要用于连接不同性能和功能的内存域,比如在多核处理器、SoC(System on Chip)等复杂系统中,各个处理器核心和外设可能需要访问不同的内存区域。而DMA_Bridge恰好为这些不同内存区域之间提供了桥梁。

DMA_Bridge工作原理依赖于几个关键的组件:

- **请求管理器(Request Manager)**: 管理来自不同请求者的内存访问请求。

- **地址转换(Address Translator)**: 将虚拟地址翻译为物理地址,也可能涉及跨不同内存域的地址映射。

- **数据传输控制器(Data Transfer Controller)**: 控制数据从源地址到目标地址的实际移动。

当一个DMA请求到达DMA_Bridge时,请求管理器首先决定请求的优先级,然后数据传输控制器开始执行数据传输,地址转换器负责正确地映射源和目标地址。整个过程,DMA_Bridge负责确保数据的一致性和完整性。

### 2.1.2 DMA_Bridge与CPU、内存的交互方式

DMA_Bridge作为内存访问的中介,其与CPU和内存的交互方式是理解其工作机制的核心。首先,DMA_Bridge与CPU的交互体现在它接收来自CPU的配置和控制指令,这包括初始化传输过程、设置传输参数等。

与内存的交互,则更加技术性。DMA_Bridge在与内存交互时必须遵守内存的访问协议,比如仲裁内存总线的使用权,确保内存操作的时序和同步。此外,当多个DMA请求同时发生时,DMA_Bridge会利用自己的调度算法来优化访问顺序,以提高效率和吞吐量。

在多核处理器系统中,DMA_Bridge能够帮助实现处理器核心间以及处理器核心与外设间的高效通信。例如,当一个处理器核心需要读写一个外设寄存器或内存时,DMA_Bridge会接收到这个请求,然后根据配置的地址映射,将请求转换为对应的物理地址,并控制数据传输。

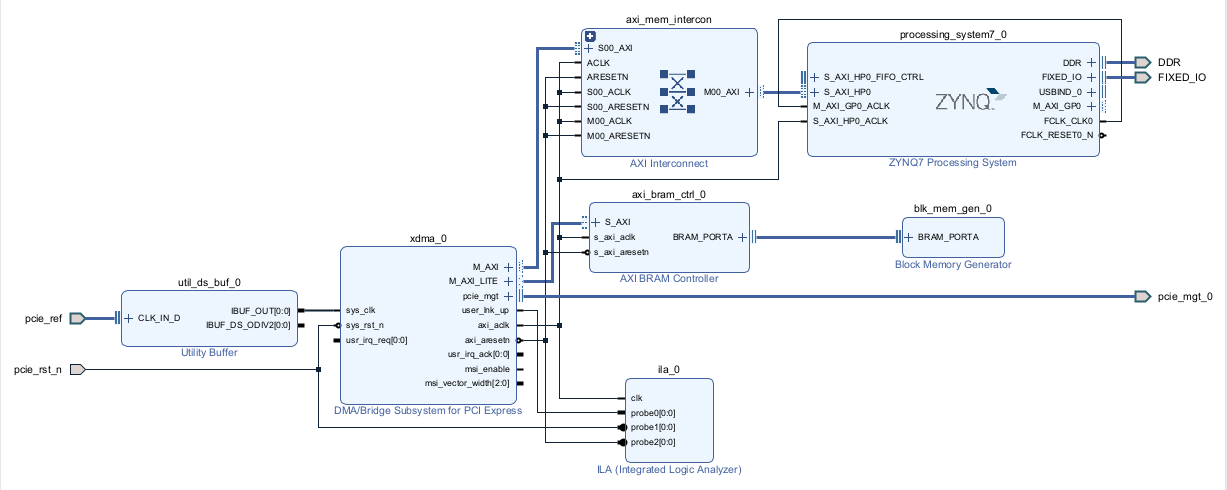

```

图示: DMA_Bridge在CPU、内存和其他外设间的交互

```

```mermaid

flowchart LR

CPU-->|DMA请求|DMA_Bridge

DMA_Bridge-->|地址转换和控制|内存

外设-->|数据读写请求|DMA_Bridge

```

```markdown

在此mermaid流程图中,我们可以看到DMA_Bridge在CPU、内存和其他外设之间的交互。CPU发出DMA请求给DMA_Bridge,然后DMA_Bridge通过地址转换来处理内存。同时,外设也会发起数据读写请求到DMA_Bridge,由其进行相应的处理。

```

## 2.2 DMA_Bridge子系统的关键技术和算法

### 2.2.1 DMA_Bridge的调度算法

DMA_Bridge子系统需要高效地处理来自不同源的大量数据传输请求。调度算法是关键,其影响着系统的吞吐率和响应时间。常见的调度策略包括:

- **先进先出(FIFO)**: 每个请求按照到达的顺序被处理。

- **最短处理时间优先(SPTF)**: 假设拥有最短处理时间的请求将被先处理,从而减少整体等待时间。

- **最短剩余时间优先(SRTF)**: 类似SPTF,但更优先考虑剩余处理时间最短的任务。

调度算法的选择会根据具体的应用场景和需求来决定。例如,在实时系统中,可能优先选择响应时间最短的调度策略。

### 2.2.2 DMA_Bridge的缓存一致性机制

在包含DMA_Bridge的系统中,缓存一致性是一个挑战。因为多个缓存可能含有同一内存位置的副本,这就需要一种机制来确保缓存行的同步。DMA_Bridge通常会使用以下技术来保持缓存一致性:

- **写直达(Write-Through)**: 数据被写入缓存时,同时也会被写入主内存。

- **写回(Write-Back)**: 数据被写入缓存,但在特定条件下才同步到主内存。

- **使无效(Invalidate)**: 在写入操作前,使其它缓存中相同地址的数据失效。

- **更新(Update)**: 在写入时,同时更新所有副本。

每种技术都有其优缺点,系统设计者需要根据工作负载特点选择合适的缓存一致性策略。

### 2.2.3 DMA_Bridge的错误处理机制

错误处理是任何系统设计的关键部分。DMA_Bridge可能面临各种错误,包括数据校验错误、地址错误等。其错误处理机制通常包括:

- **重试机制**: 当检测到传输错误时,自动重试传输过程。

- **错误日志**: 记录错误信息,便于后续的调试和问题诊断。

- **中断通知**: 发送中断信号通知CPU错误发生,由软件进行进一步处理。

- **备用路径**: 当主传输路径出现问题时,能够切换到备用路径进行数据传输。

错误处理机制不仅保障了系统的稳定性,也提供了问题分析和处理的手段。

```markdown

在探讨了DMA_B

```

0

0