【构建高效PCIe v4.1 DMA_Bridge系统】:设计要点全解析

发布时间: 2024-12-21 10:40:12 阅读量: 6 订阅数: 12

基于Xilinx_PCIe_Core的DMA设计.rar_PCIE DMA_XILINX PCIE_XILINX_DMA_dm

# 摘要

随着计算机系统性能需求的不断提升,PCIe总线技术因其高速率和低延迟的特性成为关键的互连技术。本文围绕PCIe总线技术v4.1标准及DMA_Bridge系统的设计与实现展开了详细探讨。首先介绍了PCIe总线技术基础,随后深入分析了基于v4.1标准的DMA_Bridge系统设计理论,探讨了其架构、高效数据传输机制和性能优化策略。在硬件实现方面,文章详细说明了关键硬件组件的选择、接口设计、DMA控制器和PCIe桥接器的具体实现。软件与固件开发实践部分,则讨论了驱动开发、固件编程以及系统集成测试与调试。最后,通过系统性能评估与案例分析,展示了如何优化PCIe DMA_Bridge系统的性能,并对未来发展趋势进行了展望。本文旨在为专业人士提供系统的设计、实现和优化的全面指南。

# 关键字

PCIe总线技术;DMA_Bridge系统;硬件实现;软件与固件开发;性能评估;数据传输机制

参考资源链接:[PCI Express v4.1 XDMA 学习笔记:DMA桥接子系统解析](https://wenku.csdn.net/doc/644b7a5afcc5391368e5ee07?spm=1055.2635.3001.10343)

# 1. PCIe总线技术基础与v4.1标准概述

## 1.1 PCIe总线技术简介

PCIe(Peripheral Component Interconnect Express)总线技术是计算机硬件接口的一种,它支持高速串行计算机扩展总线,广泛应用于主板、图形卡和其他外设。自1992年第一代PCI总线问世以来,这一技术经历了多个版本的迭代,其中PCIe 4.1作为较新的版本,提供了更高的数据传输速率和更低的延迟。

## 1.2 PCIe v4.1标准概述

PCIe v4.1标准的引入,使得单通道的数据传输速率达到了16 GT/s(千兆传输/秒),相比前代v3.0翻了一番,提高了系统的数据处理能力。此外,该标准还优化了电气特性,降低了功耗,同时为了保证向后兼容,v4.1设计了严格的数据协议和信号完整性要求。这使得设计师能够在维持现有系统设计的同时,获得更高的性能。

## 1.3 PCIe技术的应用与发展

PCIe技术的应用范围十分广泛,从消费级的PC扩展卡到高性能计算和服务器的IO扩展,再到移动设备中的无线通讯模块。随着数据处理需求的不断增长,PCIe技术仍在不断地演进和优化。例如,最新的PCIe 5.0标准已在研发中,预期将进一步提升速度至32 GT/s。了解这些基础知识,是深入研究PCIe总线和DMA_Bridge系统设计的坚实基础。

# 2. PCIe DMA_Bridge系统的设计理论

## 2.1 DMA_Bridge系统架构分析

### 2.1.1 DMA_Bridge的基本功能和工作原理

DMA(Direct Memory Access)即直接内存访问,是一种无需CPU干预即可在内存和I/O设备之间直接传输数据的技术。在PCIe系统中,DMA_Bridge作为数据传输的中枢,提供了硬件级别的数据交换功能,使得外围设备能够高效地与系统内存交换数据。

工作原理上,DMA_Bridge首先需要在系统启动时由软件配置,包括源地址、目标地址、传输长度等。当有数据传输需求时,DMA_Bridge会根据配置主动发起内存访问,不需要CPU介入,从而减少CPU负载并提高数据传输效率。在v4.1标准下,DMA_Bridge支持更宽的数据通道和更高的传输速率,使得数据传输的吞吐量得到了显著提升。

### 2.1.2 v4.1标准下DMA_Bridge的关键特性

PCIe v4.1标准是PCIe技术的一个重要更新,它将单通道的传输速率提升到了32 GT/s,与前代标准相比,带宽几乎翻了一倍。对于DMA_Bridge而言,这意味着系统可以在相同时间内传输更多的数据,极大地提升了性能。

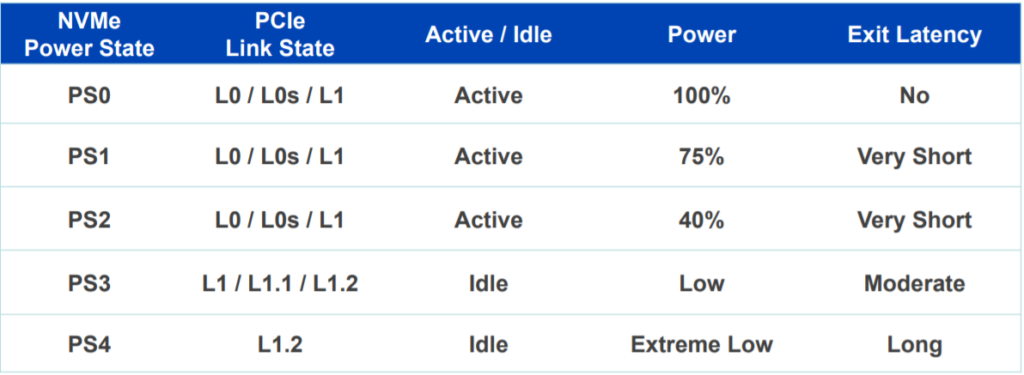

在DMA_Bridge系统设计中,需要特别注意的关键特性包括:增强了的错误检测和纠正机制、改进的电源管理、以及更为灵活的流量控制。这些特性使得v4.1标准下的DMA_Bridge不仅在性能上有所提升,同时在稳定性和功耗方面也获得了优化。

## 2.2 高效数据传输机制研究

### 2.2.1 流水线和缓冲技术在DMA_Bridge中的应用

流水线技术是通过将数据传输分解为多个连续的步骤,并允许同时进行多个步骤来提高效率的一种机制。在DMA_Bridge中,流水线技术的应用可以显著提升数据传输的吞吐率,因为当一部分数据正在被传输到目标地址时,其他的数据传输请求可以在DMA_Bridge中排队等待处理。

缓冲技术则通过在数据路径中设置临时存储区域来应对速度不匹配的问题,即缓存能够存储即将被传输的数据,或是已经从内存中读取但还未被发送到目标设备的数据。这些缓冲区的引入,使得DMA_Bridge可以平滑地处理突发数据请求,大大提升了数据传输的连续性和系统整体的性能。

```mermaid

graph LR

A[开始] --> B[请求传输数据]

B --> C[数据进入缓冲区]

C --> D{是否有待处理数据}

D -- 是 --> E[处理缓冲区中数据]

D -- 否 --> F[进入低功耗状态]

E --> G[传输数据]

G --> H[数据传输完成]

```

### 2.2.2 数据包处理与错误检测机制

在数据传输过程中,数据包的正确处理和错误检测是确保数据完整性的关键。PCIe总线使用了基于信用机制的流量控制方法来保证数据包的有序到达。DMA_Bridge需要实现对数据包的正确解析、排序和校验,同时要能够处理数据包乱序和丢失的情况。

在错误检测方面,DMA_Bridge通常需要支持多种错误检测和纠正码(例如ECC,Error-Correcting Code)以确保数据传输的准确性。在发现错误时,系统可以请求重新发送数据,或者在可纠正范围内自动进行纠正,确保数据传输的可靠性。

## 2.3 系统性能优化策略

### 2.3.1 带宽管理和优化技术

为了充分利用PCIe总线的高带宽特性,DMA_Bridge系统设计必须考虑带宽管理策略。优化技术通常包括对数据流的优先级设置、流量控制以及带宽预留等策略。通过合理安排不同数据流的传输时机,可以有效避免带宽竞争导致的延迟增加。

带宽预留机制能够在一定程度上保证关键任务的传输带宽需求得到满足,从而确保系统在高负载情况下的性能表现。此外,动态带宽调整技术能够根据当前数据传输的实际需要动态调整带宽分配,使得整体带宽使用更加高效。

### 2.3.2 低延迟处理和性能监控方法

在高性能的PCIe DMA_Bridge系统设计中,低延迟是一个非常重要的目标。为了降低数据传输的延迟,设计者需要优化DMA控制器的内部处理流程,减少数据处理和传输的时间。同时,也需要对系统中可能出现的瓶颈环节进行仔细分析和改进,确保数据可以尽快地从源地址传输到目标地址。

性能监控是优化系统性能的重要手段,通过实时监控系统的关键性能指标,如延迟、吞吐量等,可以及时发现问题并采取相应措施。典型的性能监控方法包括周期性采样、事件触发记录以及实时数据流分析等。

通过本章节的介绍,我们对PCIe DMA_Bridge系统的设计理论有了初步的了解。在下一章节中,我们将具体探讨该系统硬件实现的详细过程,包括关键硬件组件的选择、硬件接口设计、DMA控制器及PCIe桥接器的开发等。这将为有兴趣深入研究或实现此类系统的技术人员提供实用的指导。

# 3. PCIe DMA_Bridge系统的硬件实现

0

0