STM32 SPI时钟管理:频率调整与同步问题的终极解决方案

发布时间: 2024-12-28 09:35:25 阅读量: 7 订阅数: 13

基于幼儿发展的绘本在小班幼儿教育中的实践与优化策略

# 摘要

SPI(Serial Peripheral Interface)通信是一种广泛应用于微控制器与外围设备之间的串行通信协议。本文首先介绍了SPI通信的基础知识,详细阐述了SPI总线协议、SPI模式及特性,并分析了时钟极性(CPOL)和时钟相位(CPHA)对通信的影响。接着,文章深入探讨了SPI时钟管理与频率调整理论,提供了频率计算方法和关键参数分析。针对STM32平台,本文展示了SPI初始化配置及频率调整的实战技巧,并提供了同步问题的诊断与解决方法。最后,文章探讨了SPI同步与异步通信的优化策略,包括时钟策略、性能提升手段、异步通信优化策略,以及故障排除与性能监控方法。通过高级应用案例分析,本文展示了SPI在复杂环境下的时钟管理、高精度数据采集系统中的应用,以及跨平台通信的解决方案。本文旨在为工程师提供全面的SPI通信解决方案,提高系统设计与开发的效率和可靠性。

# 关键字

SPI通信;时钟管理;频率调整;STM32配置;同步优化;异步通信

参考资源链接:[STM32 SPI总线通信详解:主从模式与协议分析](https://wenku.csdn.net/doc/70amsibqyw?spm=1055.2635.3001.10343)

# 1. SPI通信基础知识

在串行通信技术中,SPI(Serial Peripheral Interface,串行外设接口)是一种常用的高速、全双工、同步通信接口。它广泛应用于微控制器与各种外围设备之间的通信。SPI通信主要依靠主从设备的四个基本信号线:SCLK(时钟信号)、MOSI(主设备数据输出,从设备数据输入)、MISO(主设备数据输入,从设备数据输出)和SS(从设备选择)来完成。

## 1.1 SPI的工作原理

SPI通信协议允许一个主设备和一个或多个从设备进行数据交换。工作时,主设备通过SCLK线提供同步时钟信号,通过SS线选择一个特定的从设备进行通信,然后通过MOSI和MISO线传输数据。数据通常在时钟信号的上升沿或下降沿被锁存,并在下一个边沿进行采样。

## 1.2 SPI通信的优缺点

SPI接口的一个主要优势在于它的速度,因为它使用独立的发送和接收线路,可以同时进行数据的发送和接收。此外,SPI设备的时钟速率可以非常高,适合高速设备之间的通信。然而,SPI协议也有其缺点,它是一种点对点通信,当有多个从设备时需要多个SS线路,这可能增加硬件的复杂度和成本。

## 1.3 SPI通信的应用场景

SPI常用于对速度要求较高的通信场景,例如存储器、ADC(模数转换器)、DAC(数模转换器)和其他外设。对于要求简单且速度较快的设备通信,SPI是一个很好的选择。在下一章中,我们将深入探讨SPI时钟管理与频率调整的理论,进一步理解如何优化SPI通信以满足不同的性能需求。

# 2. SPI时钟管理与频率调整理论

## 2.1 SPI总线协议详解

### 2.1.1 SPI通信原理

SPI(Serial Peripheral Interface)总线是一种高速的,全双工,同步的通信总线。它被广泛应用于电子通信设备中,如ADC、DAC、EEPROM、Flash和数字信号处理器等。SPI通信原理基于主从架构,主设备通常是一个微控制器(MCU),而从设备可以是诸如传感器、存储器等外围设备。

SPI通信通过四条线来完成数据交换:

- SCLK(Serial Clock):串行时钟线,由主设备控制,用来同步主从设备间的数据传输。

- MOSI(Master Output Slave Input):主输出从输入线,数据从主设备传输到从设备。

- MISO(Master Input Slave Output):主输入从输出线,数据从从设备传输到主设备。

- SS(Slave Select):从设备选择线,用于从设备的片选和复位。

工作流程通常是:

1. 主设备通过SS线选中一个从设备。

2. 主设备在SCLK时钟信号的驱动下,通过MOSI线发送数据到从设备。

3. 从设备同时在MISO线上发送数据给主设备。

4. 如此这般,数据在一个时钟周期内被发送出去,又在下一个时钟周期内被接收。

在数据传输过程中,主设备和从设备的同步是关键。主设备需要确保时钟信号在数据发送前后保持稳定,并且从设备能够在时钟信号的正确边沿读取数据。

### 2.1.2 SPI模式与特性

SPI协议支持四种不同的数据传输模式,这些模式由时钟极性(CPOL)和时钟相位(CPHA)两个参数定义。它们决定了数据在SCLK信号的哪条边沿上采样和/或设置。

- 模式0(CPOL=0, CPHA=0):时钟信号空闲时为低电平,数据在SCLK的上升沿采样,在下降沿设置。

- 模式1(CPOL=0, CPHA=1):时钟信号空闲时为低电平,数据在SCLK的下降沿采样,在上升沿设置。

- 模式2(CPOL=1, CPHA=0):时钟信号空闲时为高电平,数据在SCLK的下降沿采样,在上升沿设置。

- 模式3(CPOL=1, CPHA=1):时钟信号空闲时为高电平,数据在SCLK的上升沿采样,在下降沿设置。

不同的SPI模式适用于不同的硬件设备。因此,在设计SPI通信时,必须根据从设备的硬件手册选择正确的通信模式以保证通信的准确性。

### 2.2 时钟极性和相位的影响

#### 2.2.1 时钟极性(CPOL)的定义及应用

时钟极性(CPOL)定义了SPI总线空闲时的时钟信号电平状态。根据不同的CPOL值,时钟信号可以是高电平或低电平。

- 当CPOL=0时,空闲的时钟信号为低电平。

- 当CPOL=1时,空闲的时钟信号为高电平。

CPOL的选择对于确保主从设备同步至关重要。如果主从设备的时钟极性设置不一致,可能导致数据传输时序不匹配,从而导致通信失败。

#### 2.2.2 时钟相位(CPHA)的选择与分析

时钟相位(CPHA)定义了数据采样和设置是在时钟信号的哪个边沿上进行的。

- 当CPHA=0时,数据在时钟信号的第一个边沿(上升沿或下降沿,取决于CPOL)采样,在第二个边沿设置。

- 当CPHA=1时,数据在时钟信号的第二个边沿采样,在第一个边沿设置。

不同的CPHA值会影响到数据的发送和接收,它决定了数据的采样时机,从而影响数据的准确性。选择合适的CPHA值能够确保数据在稳定的时间窗口内被正确采样。

### 2.3 频率调整理论与公式

#### 2.3.1 SPI时钟频率的计算方法

SPI时钟频率决定了数据传输的速度。在SPI总线系统中,主设备控制时钟频率,必须确保所选频率不会超过从设备允许的最大时钟频率。

时钟频率的计算公式一般为:

\[ f_{SCLK} = \frac{f_{BRP}}{2 \times (BRP + 1)} \]

其中,\( f_{SCLK} \)是SCLK的频率,\( f_{BRP} \)是SPI模块的基础时钟频率,BRP(Baud Rate Prescaler)是一个可编程预分频器的值。

从设备的数据手册通常会规定一个时钟频率范围,主设备必须在这个范围内选择合适的频率。在选择预分频器值时,应该考虑到通信的实时性和数据传输的准确性。

#### 2.3.2 影响时钟频率的关键参数

- 预分频器(BRP):决定了时钟频率的基础值,它从基础时钟频率中分频出实际的SCLK频率。

- 数据大小:在某些微控制器中,一次传输的数据大小可以设置为8位或16位,这可能影响时钟频率的计算和时钟管理策略。

- 传输模式:全双工模式或半双工模式,这可以影响到时钟频率的管理,因为全双工模式同时进行数据的发送和接收。

- 从设备特性:每个从设备可能有特定的时钟频率要求和通信特性,主设备需要根据这些信息调整频率以保证设备间的兼容性。

理解这些参数对于实现高效、稳定的SPI通信至关重要。通过合理配置这些参数,可以优化通信性能和数据传输效率,从而满足应用的具体需求。

## 2.2 时钟极性和相位的影响

### 2.2.1 时钟极性(CPOL)的定义及应用

时钟极性(Clock Polarity, CPOL)是SPI通信协议中决定时钟信号空闲状态电平的关键参数。CPOL参数有两个可能的值,0和1,分别对应于低电平和高电平。

- CPOL=0:表示SPI总线在空闲时钟周期时,时钟信号(SCLK)维持低电平(逻辑0)。

- CPOL=1:表示SPI总线在空闲时钟周期时,时钟信号(SCLK)维持高电平(逻辑1)。

CPOL的选择会影响数据的采样点。在SPI协议中,数据总是在SCLK信号的边沿上采样。具体是上升沿还是下降沿采样,则由时钟相位(CPHA)来决定。为了保证数据通信的可靠性,主设备和从设备必须使用相同的CPOL值。如果CPOL设置不一致,可能会导致数据同步错误,从而影响数据通信的准确性。

CPOL参数的应用场景包括:

- 当CPOL=0时,通常用于需要在SCLK的上升沿进行数据采样的场景。

- 当CPOL=1时,适用于在SCLK的下降沿进行数据采样的场景。

不同的硬件设备可能会对CPOL有不同的要求,因此在设计SPI通信时,必须仔细阅读从设备的数据手册,以确保通信双方的时钟极性设置相匹配。

### 2.2.2 时钟相位(CPHA)的选择与分析

时钟相位(Clock Phase, CPHA)与CPOL配合使用,共同决定了数据的采样点和设置点。CPHA有两个可能的值,0和1,分别对应于数据在时钟信号的第一个边沿采样还是第二个边沿采样。

- CPHA=0:数据采样发生在SCLK的第一次边沿,数据设置发生在第二次边沿。

- CPHA=1:数据采样发生在SCLK的第二次边沿,数据设置发生在第一次边沿。

要确定最佳的CPHA值,必须考虑数据传输的稳定性和同步问题。在SPI通信中,数据的同步和稳定传输对于保持通信的可靠性至关重要。

如果数据在SCLK的上升沿采样,并在下降沿设置(即CPOL=0且CPHA=0),则适合于以下场景:

- 从设备的输出数据稳定时间长,能够确保在时钟上升沿之前稳定。

- 主设备的输入通道对上升沿响应快。

相反,如果数据在SCLK的下降沿采样,并在上升沿设置(即CPOL=1且CPHA=1),则适合于以下场景:

- 从设备输出数据具有较长的稳定时间,确保在下降沿之前稳定。

- 主设备输入通道对下降沿有较好的响应。

在实际应用中,CPOL和CPHA的组合使用要根据具体的硬件特性和应用需求来确定。通过正确配置这两个参数,可以确保主从设备间的数据同步和稳定性,从而实现高效的数据传输。

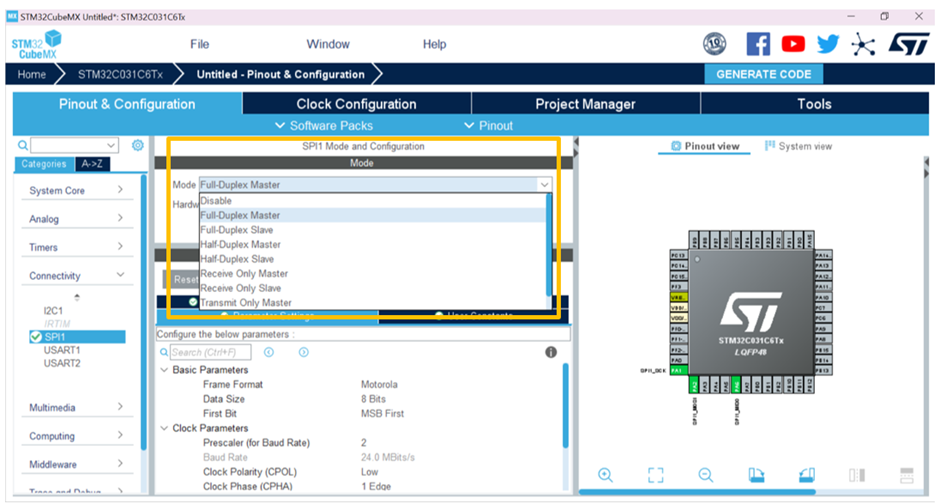

# 3. STM32

0

0