STM32 SPI片选信号管理:多设备通信优化秘籍

发布时间: 2024-12-28 09:40:45 阅读量: 6 订阅数: 12

# 摘要

本文系统地介绍了SPI通信协议的基础知识及其在STM32微控制器中的应用和配置方法。文章从SPI通信协议的简介开始,深入探讨了STM32的SPI硬件特性、寄存器配置、片选信号管理以及多SPI设备通信的实践案例。此外,还探讨了提高多SPI设备通信性能的高级优化技巧,并展望了SPI通信在物联网(IoT)和其他新兴技术中的应用前景。通过本文,读者将获得全面理解SPI协议,以及如何在现代嵌入式系统中有效应用SPI通信技术的知识。

# 关键字

SPI通信协议;STM32;硬件特性;片选信号管理;通信优化;物联网应用

参考资源链接:[STM32 SPI总线通信详解:主从模式与协议分析](https://wenku.csdn.net/doc/70amsibqyw?spm=1055.2635.3001.10343)

# 1. SPI通信协议简介与应用基础

## 1.1 SPI通信协议的概念

串行外设接口(Serial Peripheral Interface, SPI)是一种高速的,全双工,同步的通信总线。与常见的I2C总线相比,SPI拥有更高的通信速率,可实现1位到16位的串行数据传输,广泛应用于微控制器与各种外围设备之间的通信。SPI通信协议由四条信号线组成:主设备的输出从设备的输入线(MOSI),主设备的输入从设备的输出线(MISO),设备选择线(CS),和时钟线(SCK)。

## 1.2 SPI通信协议的应用场景

SPI因其快速的数据传输率和简洁的四线接口,适用于对速度要求较高的应用,例如:SD卡,数字信号处理器(DSP),数字模拟转换器(DAC),以及各种传感器。此外,由于其简洁的硬件要求,SPI非常适合用于微控制器和简单的外围设备之间的连接。

## 1.3 SPI通信协议的优势与限制

优势在于:

- **高速数据传输**:对于要求高传输速度的应用非常有用。

- **全双工通信**:数据可以同时发送和接收。

- **简单的硬件连接**:四条线即可完成通信,硬件设计相对简单。

然而,其也存在限制:

- **扩展性限制**:随着连接设备数量的增加,总线数量迅速增加。

- **兼容性问题**:由于SPI没有统一的标准,不同设备间的SPI可能需要额外的配置。

本章为读者提供了SPI通信协议的基本概念、应用范围以及其优势和限制,为后续章节更深层次的硬件配置和应用实践奠定了基础。在接下来的章节中,我们将深入探讨如何在STM32平台上配置和使用SPI,以及如何管理多SPI设备之间的通信。

# 2. STM32 SPI硬件特性与配置

## 2.1 SPI接口的工作模式和参数设置

### 2.1.1 SPI模式的选择与应用场景

SPI(Serial Peripheral Interface)是一种常用的同步串行通信协议,广泛应用于微控制器和各种外围设备之间的通信。它支持全双工通信,允许数据在两个方向上同时传输。STM32微控制器支持多种SPI工作模式,每个模式都有其特定的应用场景:

- **模式0 (CPOL=0, CPHA=0)**: 时钟信号在空闲状态时为低电平,在时钟信号的上升沿采样数据,在下降沿输出数据。这种模式适合于一些早期的SPI设备,例如某些型号的EEPROM。

- **模式1 (CPOL=0, CPHA=1)**: 时钟在空闲状态为低电平,但数据在时钟的下降沿采样,在上升沿输出。这种模式在一些串行闪存和SD卡通信中非常常见。

- **模式2 (CPOL=1, CPHA=0)**: 时钟信号在空闲状态为高电平,在时钟信号的下降沿采样数据,在上升沿输出数据。这种模式不常见。

- **模式3 (CPOL=1, CPHA=1)**: 时钟在空闲状态为高电平,数据在时钟的上升沿采样,在下降沿输出。这种模式也很少使用。

选择正确的SPI模式取决于所连接的外围设备,因此在设计系统时,了解和遵循外围设备的技术手册至关重要。

### 2.1.2 SPI时钟极性和相位的配置方法

在STM32中,SPI的时钟极性(CPOL)和时钟相位(CPHA)可以通过SPI控制寄存器1(CR1)进行设置:

```c

SPI1->CR1 |= SPI_CR1_CPOL; // 设置时钟极性,1代表高电平,0代表低电平

SPI1->CR1 |= SPI_CR1_CPHA; // 设置时钟相位,1代表第二个边沿采样,0代表第一个边沿采样

```

上述代码块中,`SPI_CR1_CPOL` 和 `SPI_CR1_CPHA` 是STM32标准外设库提供的宏定义,根据需要可以设置为0或1,以匹配外围设备的要求。

### 2.1.3 波特率与数据格式的设置技巧

STM32的SPI接口允许灵活设置通信速率,通过控制寄存器(Baud Rate Register, BR)进行配置,以适应不同外围设备的速度要求。波特率的设置必须保证SPI主机与从设备的波特率匹配,以免通信失败。

```c

uint16_t br = (uint16_t)((SystemCoreClock / 2) / Desired_BAUDRATE);

SPI1->CR1 |= (br << 3); // 将计算好的波特率值设置到SPI_BaudRate字段

```

在上面的代码中,`SystemCoreClock` 是系统核心时钟频率,`Desired_BAUDRATE` 是期望的SPI通信速率。`BR` 字段的设置依赖于具体的STM32系列和型号,因此具体的数值和配置方式需要参考对应的参考手册。

STM32还支持不同的数据格式,例如8位或16位数据长度,可以通过控制寄存器的最低两位进行配置。正确的数据格式设置保证数据在通信过程中不会被错误地解析。

## 2.2 STM32 SPI寄存器详解

### 2.2.1 控制寄存器CR1和CR2的功能与配置

STM32的SPI控制寄存器1(CR1)和控制寄存器2(CR2)用于配置SPI的各种功能。CR1用于设置数据传输的主从模式、波特率、时钟极性和相位、数据格式等。而CR2主要用来设置数据传输时的中断使能、DMA使能、NSS信号的管理方式等。

```c

SPI1->CR1 |= SPI_CR1_MSTR; // 设置SPI为主模式

SPI1->CR1 |= SPI_CR1_BR_0; // 设置波特率分频值的低位

// 其他CR1相关设置...

```

通过CR1和CR2的合理配置,可以实现对STM32 SPI的精细控制,以适应不同的通信需求。

### 2.2.2 状态寄存器SR与数据寄存器DR的读写操作

STM32的SPI状态寄存器(SR)包含了SPI通信过程中的状态信息,例如发送缓冲区是否为空、接收缓冲区是否有数据等。合理利用状态寄存器可以避免通信错误和提高数据处理效率。

```c

if (SPI1->SR & SPI_SR_TXE) { // 检查发送缓冲区是否为空,如果为空则可以发送数据

// 发送数据代码...

}

```

数据寄存器(DR)是数据实际进出SPI总线的通道。在发送数据前,用户需要将数据写入到DR;在接收数据后,应从DR中读取数据。读写操作直接影响数据的传输。

### 2.2.3 接收与发送缓冲区的工作机制

STM32 SPI接口内部含有独立的发送和接收缓冲区,这使得数据可以连续地发送和接收而无需中断CPU。发送缓冲区在向SPI总线发送数据的同时,接收缓冲区可以接收新数据。这些操作在硬件层面自动完成,极大地提高了通信效率。

理解这一工作机制,可以帮助设计出更为高效的数据处理流程,例如在连续的通信任务中,可以同时进行数据的发送和接收,实现数据流的无缝对接。

以上所述就是对STM32 SPI硬件特性的基础认识。深入理解这些寄存器配置和工作机制,对于开发高效可靠的SPI通信应用至关重要。接下来的章节将更加深入探讨多SPI设备的管理与应用案例,为读者带来更为高级的实践技能。

# 3. 多SPI设备的片选信号管理

## 3.1 片选信号的基础知识与作用

### 3.1.1 片选信号的逻辑电平与功能解释

片选信号(Chip Select,简称CS)是SPI通信中的一个关键信号,负责选择当前通信的从设备(Slave)。通常情况下,主设备(Master)需要通过控制片选信号的电平,来选择特定的从设备进行数据交换。在硬件设计上,每个从设备的CS引脚都必须被单独控制,以确保主设备与特定的从设备建立通信。

逻辑电平上,片选信号通常有两个状态,低电平有效和高电平有效。在低电平有效的系统中,主设备将CS置低表示选择该从设备进行通信;在高电平有效的系统中,则需要将CS置高。片选信号的逻辑电平特性需要在硬件设计和软件配置时保持一致,以防止通信错误。

### 3.1.2 片选信号在SPI通信中的重要性

片选信号的重要性在于它确保了SPI总线上的数据交换是在主从设备间准确无误地进行。没有片选信号,主设备无法区分它要与哪个从设备通信,从而导致数据冲突和通信错误。在多SPI设备的系统中,片选信号的管理尤其重要,因为多个设备的存在增加了通信的复杂度。

在多设备系统中,片选信号常与其他信号(如时钟信号SCK、主从信号MISO/MOSI等)同步使用,以确保数据的同步传输和接收。正确管理片选信号是设计可靠、高效的SPI通信系统的关键。

## 3.2 片选信号的硬件管理方法

### 3.2.1 使用GPIO手动控制片选信号的优劣

手动控制片选信号是一种简单的方法,通过通用输入输出端口(GPIO)控制片选引脚的电平。这种方法的优点是操作简单、灵活性高,适合于片选信号不多的情况。缺点是当片选信号数量增多时,占用大量CPU资源用于频繁地切换GPIO电平,导致CPU负担加重,并可能降低通信效率。

```c

// 伪代码示例:手动控制GPIO以切换片选信号

void SetChipSelect(uint8_t device, bool select) {

uint8_t cs_pin = GetCSPin(device);

if (select) {

GPIO_SetLow(cs_pin); // 置低电平以选择设备

} else {

GPIO_SetHigh(cs_pin); // 置高电平以取消选择

}

}

```

在上述示例中,`GPIO_SetLow` 和 `GPIO_SetHigh` 分别用于将指定的GPIO引脚置为低电平或高电平。`GetCSPin` 是一个假定的函数,用于根据设备编号返回对应的GPIO引脚编号。这种方法适用于对性能要求不高、设备数量较少的场合。

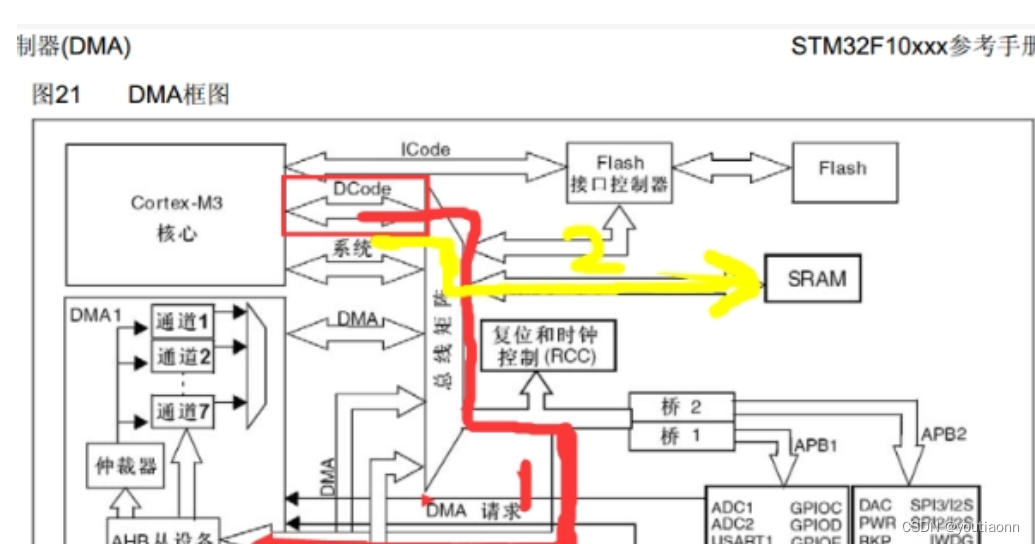

### 3.2.2 利用STM32的DMA和中断功能自动化管理片选信号

为了减少CPU负担,可以使用STM32的直接内存访问(DMA)和中断服务程序(ISR)来自动化地管理片选信号。通过DMA可以在不占用CPU的情况下,快速切换GPIO电平,而中断可以响应外部事件,执行相应的片选操作。这种方式适用于对性能要求较高,片选信号数量较多的场合。

```c

// DMA中断服务程序伪代码示例

void DMA_IRQHandler(void) {

if (DMA_GetITStatus(DMA_IT_TCIFx))

```

0

0