【Quartus快捷键深度体验】:专业FPGA设计师的键盘操控术

发布时间: 2025-01-05 02:16:52 阅读量: 8 订阅数: 8

FPGA控制PS2键盘verilog设计Quartus9.1工程源码+设计说明文件.zip

# 摘要

本文系统地介绍了Quartus软件的功能、界面布局、快捷键基础应用、进阶技巧、定制与个性化以及最佳实践。通过阐述快捷键的类型、分类、项目管理、设计输入、仿真优化、编译流程、设备编程、配置管理、脚本自动化控制等方面,文章旨在提高工程师对Quartus软件的操作效率。同时,本文还探讨了如何通过自定义快捷键设置,形成实用的快捷键策略,并通过案例分析分享了快捷键在复杂项目中的综合应用。此外,文章强调了社区资源与交流的重要性,并提供了分享快捷键使用心得与建议的平台。整体而言,本文为Quartus用户提供了全面的快捷键操作指南,旨在优化FPGA与ASIC设计流程,提升设计效率与项目质量。

# 关键字

Quartus软件;快捷键应用;项目管理;设计输入;仿真优化;自动化控制;快捷键定制;社区分享;FPGA设计;ASIC设计

参考资源链接:[Quartus II高效快捷键指南:提升设计效率](https://wenku.csdn.net/doc/1y6z6fo7ry?spm=1055.2635.3001.10343)

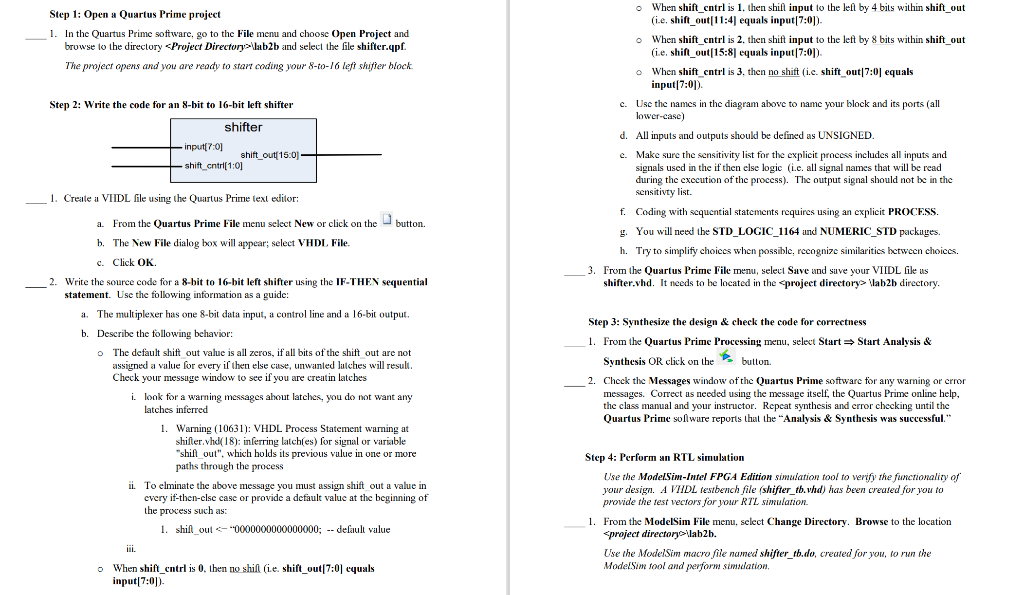

# 1. Quartus软件概述与界面布局

Quartus Prime是Altera公司(现为英特尔旗下公司)推出的FPGA/CPLD编程与设计软件。它广泛应用于电子工程师进行FPGA开发和硬件描述语言(HDL)设计。Quartus软件提供了一系列设计工具,从逻辑设计、综合、仿真、到布局布线和编程,是一套完整的FPGA设计解决方案。

界面布局上,Quartus软件从上至下分别由菜单栏、工具栏、项目导航器、主要工作区及状态信息栏组成。菜单栏提供各种设计处理的功能选项;工具栏则对常用功能进行快速访问;项目导航器则以层次化方式展示项目文件和设计实体;工作区是设计活动的主要区域;状态信息栏显示软件状态和警告信息。

作为设计者,熟悉Quartus界面布局是高效完成设计任务的基础。例如,在设计输入阶段,项目导航器中可以快速浏览设计文件结构,工作区则用于编写和编辑代码或进行图形化的逻辑设计。通过这种布局安排,Quartus为用户提供了灵活、直观的工作环境,方便用户快速适应并提高设计效率。

# 2. Quartus快捷键基础应用

### 2.1 快捷键的类型和分类

在本节中,我们将深入了解Quartus软件中使用的快捷键的分类,以及一些最常用的快捷键。Quartus快捷键可以大幅提高设计效率和项目管理的便捷性。我们将介绍快捷键的类型和分类,这包括了解各种快捷键的功能、如何记忆它们以及如何将它们应用于日常工作。

#### 2.1.1 常用快捷键介绍

Quartus软件的常用快捷键涵盖了从项目创建到编译的各个阶段。例如:

- `Ctrl + S`:保存当前打开的文件。

- `Ctrl + N`:新建项目。

- `Ctrl + O`:打开现有项目。

- `Ctrl + W`:关闭当前打开的文件或项目。

- `Ctrl + Z`:撤销上一操作。

- `Ctrl + Shift + Z` 或 `Ctrl + Y`:重做上一撤销的操作。

这些快捷键是日常工作中最常用的,它们可以帮助用户在不离开键盘的情况下高效地完成任务。

#### 2.1.2 快捷键与菜单命令的对应关系

了解快捷键与菜单命令之间的关系对于提高工作效率至关重要。Quartus软件中的每个快捷键都对应着界面上的一个或多个菜单项。通过熟悉这种对应关系,用户可以更快地找到他们需要的功能。

### 2.2 高效项目管理技巧

在本小节中,我们将深入了解如何利用快捷键进行高效的项目管理。这涉及到新建、打开和保存项目,以及项目文件的快速导航和操作。这些技巧能够显著减少项目管理所需的时间。

#### 2.2.1 新建、打开与保存项目的快捷方式

快捷键在项目创建和管理过程中扮演着关键角色。例如,使用`Ctrl + N`可以快速新建项目,而`Ctrl + O`则用于打开已有项目。对于经常需要保存工作的情况,`Ctrl + S`可以随时保存文件。

#### 2.2.2 项目文件的快速导航和操作

当处理具有大量文件的复杂项目时,快速导航至特定文件变得至关重要。快捷键如`Ctrl + Tab`可以快速在打开的文件之间切换。此外,Quartus软件还支持自定义文件模板,便于快速创建标准文件。

### 2.3 设计输入和仿真优化

设计输入阶段是FPGA和ASIC设计流程中的重要部分。在此阶段,快捷键不仅可以简化设计过程,还可以在仿真阶段加快设计的调试和验证。

#### 2.3.1 设计输入的快捷键操作

设计输入阶段,可以通过快捷键快速插入元件、编辑端口名称等。例如,`Ctrl + Space`可用于弹出自动补全提示,帮助用户更快地完成代码编写。`Ctrl + Alt + D`用于快速生成测试平台。

#### 2.3.2 仿真过程的快捷键加速技巧

仿真过程是验证设计正确性的重要步骤,而快捷键可以在这一步骤中起到加速作用。比如,`F6`和`F5`键可以分别用于启动仿真和单步执行,加快调试过程。

**代码块示例**:

下面是一个Verilog代码块的示例,用于生成一个简单的计数器模块。

```verilog

module counter (

input wire clk, // 时钟信号

input wire reset_n, // 异步复位信号(低电平有效)

output reg [7:0] count // 8位输出计数

);

always

```

0

0