计算机组成原理题库梳理:快速提升解题技巧与方法

发布时间: 2024-12-14 05:29:30 阅读量: 8 订阅数: 14

五邑大学计算机组成原理期末复习题库和期末试卷

参考资源链接:[计算机组成原理课后习题及答案-唐朔飞(完整版).ppt](https://wenku.csdn.net/doc/645f3404543f8444888ac128?spm=1055.2635.3001.10343)

# 1. 计算机组成原理基础概述

计算机科学的核心是计算机组成原理,这门学科深入探讨了计算机系统的构造和工作方式。在第一章中,我们将带领读者从宏观的角度去理解计算机的基本组成部分,为进一步深入探讨硬件组件打下坚实的基础。

## 1.1 计算机系统概览

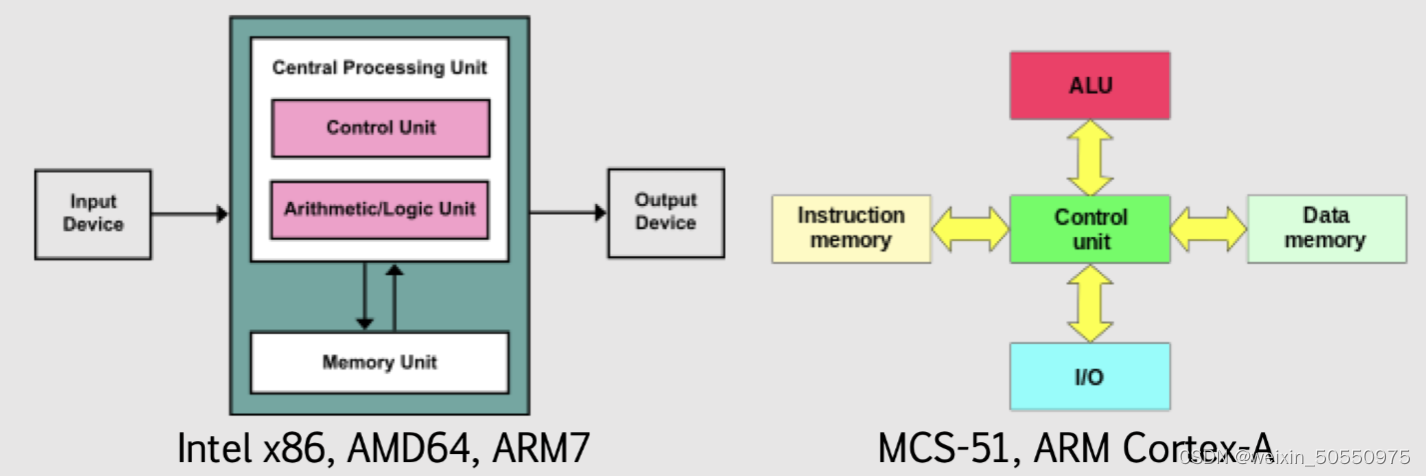

计算机系统是由多个组件构成的复杂结构,主要包括输入设备、输出设备、中央处理器(CPU)、存储器以及内部总线。每个组件都有其特定的功能和交互方式,使得整个系统能够高效、稳定地运行。

## 1.2 信息表示与处理

在计算机内部,一切信息都是以二进制的形式表示的。数据如何被转换为二进制,以及计算机如何处理这些二进制数据,是理解计算机系统运作原理的关键。这涉及到数制转换、编码系统以及数据的存储和处理。

## 1.3 计算机的工作流程

计算机的工作流程可以概括为输入、处理、输出三个主要阶段。用户通过输入设备与计算机交互,CPU对输入的数据和指令进行处理,然后通过输出设备展示结果。这三者之间的协同工作保证了计算机的顺畅运行。

理解了计算机的基本组成原理之后,读者将能够更好地把握后续章节中对处理器、存储系统、I/O系统以及其它高级主题的详细讨论。

# 2. 核心组成部件解析与应用

## 2.1 处理器结构与指令集

### 2.1.1 处理器的基本组成

处理器,也称为中央处理单元(CPU),是计算机系统的核心部件,负责解释和执行程序指令。一个典型的处理器由以下基本组成:

- 算术逻辑单元(ALU):执行所有的算术运算,如加、减、乘、除等,以及逻辑操作,如与、或、非、异或等。

- 控制单元(CU):从内存中提取指令,解释指令,并控制数据流向,协调各个部件以执行指令。

- 寄存器:临时存储指令、数据和地址,高速存储器,距离ALU非常近,以实现快速数据存取。

- 时钟:提供同步信号,确保数据在处理器内部正确地流动和处理。

处理器的这些组件协同工作,形成一个高度优化的指令执行流程,使得计算机能够进行高效的计算任务。

### 2.1.2 指令集架构的理解与分类

指令集架构(ISA)是处理器能够识别和执行的指令集合。ISA的分类主要为两大类:

- 复杂指令集计算(CISC):如Intel x86架构,拥有大量复杂的指令,能够直接处理高级语言的常见任务,但单条指令执行时间可能较长。

- 精简指令集计算(RISC):如ARM和MIPS架构,指令数量较少,结构简单,通常执行时间短,流水线效率高。

选择合适的ISA对于处理器的设计至关重要,因为它直接影响到计算机的性能和能效。RISC架构由于其简化的特性,能够更有效地执行流水线操作,因此近年来在移动设备和嵌入式系统中变得流行。

### 2.1.3 指令执行周期的详细分析

一条指令的生命周期可以分为以下几个阶段:

1. 取指(Fetch):CU从内存中取出指令的地址。

2. 解码(Decode):CU解码指令,理解其代表的操作。

3. 执行(Execute):ALU执行解码后确定的操作。

4. 访存(Access Memory):若指令需要访问内存,执行数据的读或写操作。

5. 写回(Write Back):将执行结果写回寄存器。

每条指令的执行周期涉及到这些阶段,但现代处理器通常通过流水线技术使得每个阶段可以并行处理,从而提高了CPU的吞吐量。

```mermaid

graph LR

A[取指 Fetch] --> B[解码 Decode]

B --> C[执行 Execute]

C --> D[访问内存 Access Memory]

D --> E[写回 Write Back]

```

## 2.2 存储系统的工作机制

### 2.2.1 内存与缓存的工作原理

计算机存储系统的主要目的是快速且高效地提供数据。内存(RAM)是易失性存储,速度快但容量有限。缓存(Cache)是内存与处理器之间的高速缓冲区,用来减少处理器访问主存的延迟。

- 缓存的工作原理基于局部性原理,包括时间局部性和空间局部性。

- 缓存分为不同等级,L1缓存最快但容量最小,而L2缓存容量比L1大,速度稍慢,以此类推。

在存储器的层次结构中,处理器首先访问的是缓存,只有当所需数据不在缓存中时,才会访问内存。

### 2.2.2 存储器的层次化结构

存储系统采用分层次的设计,每个层次拥有不同的访问速度、容量和成本。从上到下,速度逐渐降低,容量逐渐增加,成本也相应降低。

- 第一级(L1)缓存:最快的缓存,直接集成在CPU内部。

- 第二级(L2)缓存:比L1稍慢,通常也是片上缓存。

- 第三级(L3)缓存:可用作系统中所有核心的共享缓存。

- 主存储器(RAM):对所有处理器核心都可访问的存储。

- 辅助存储(如SSD、HDD):提供大容量存储空间,但速度较慢。

这种层次化结构的目的是在速度与成本之间取得平衡。

### 2.2.3 存储管理技术与策略

存储管理涉及几个关键技术与策略,包括分页、分段、虚拟内存等。

- 分页:将主存划分为固定大小的页,虚拟内存系统将程序地址空间分割成页面。

- 分段:将程序和数据分成不同长度的段,如代码段、数据段等,提供更大的灵活性。

- 虚拟内存:允许程序使用比实际物理内存更大的地址空间,通过页表来映射虚拟地址到物理地址。

虚拟内存技术使得系统能够运行更多更大的程序,而分页和分段提供了地址空间的灵活管理和保护。

## 2.3 输入输出系统与接口技术

### 2.3.1 I/O接口的基本概念

I/O接口是连接处理器和外部设备的硬件和软件的集合,负责数据的输入和输出。基本概念包括:

- 设备控制器:管理特定I/O设备,执行数据传输。

- 中断机制:I/O设备完成任务时通知处理器。

- 直接内存访问(DMA):允许外部设备直接访问内存,无需处理器介入。

I/O接口的设计对于系统的整体性能至关重要,需要确保数据能够高效且正确地传输。

### 2.3.2 I/O设备的数据传输方式

I/O设备的数据传输方式主要有三种:

- 程序控制I/O:CPU直接控制数据的传输,效率较低,适用于简单系统。

- 中断驱动I/O:I/O设备在准备好数据后发送中断信号,CPU响应中断并处理数据。

- 直接内存访问(DMA):I/O设备能够在不需要CPU参与的情况下访问内存。

中断驱动和DMA是现代I/O设备常用的方式,以减少对CPU的依赖,提高I/O操作的效率。

### 2.3.3 总线技术在I/O系统中的应用

总线是一组共享的信号线路,用于数据和控制信息的传输。在I/O系统中,总线技术应用包括:

- 系统总线:连接CPU、内存和主要I/O设备,如PCI总线。

- 扩展总线:用于连接其他I/O设备,如USB、SATA等。

总线宽度和传输速率决定了总线的性能。一个高效的总线技术可以支持I/O设备的高速数据传输,而不会成为系统的瓶颈。

```mermaid

graph LR

A[处理器] -->|指令| B[控制单元]

B -->|控制信号| C[存储器]

B -->|控制信号| D[输入输出设备]

C -->|数据| B

D -->|数据| B

```

在以上章节中,我们深入探讨了处理器结构、存储系统和I/O系统的运作机制

0

0