【Quartus高级应用】:参数化设计全加器阵列的策略与技巧

发布时间: 2024-12-14 00:19:00 阅读量: 6 订阅数: 9

EDA Quartus13.0使用 1位全加器仿真.docx

参考资源链接:[Quartus II 实验:1位全加器的原理图设计与仿真](https://wenku.csdn.net/doc/4gb6f4yfgn?spm=1055.2635.3001.10343)

# 1. Quartus软件简介及参数化设计概念

Quartus软件是Altera公司推出的一款全面的FPGA/CPLD设计工具,它以图形化界面和强大的综合能力而闻名。Quartus不仅支持硬件描述语言(HDL)的设计输入,还提供自动化的流程来完成从设计到最终的FPGA编程文件。这一章将引导读者初步了解Quartus的使用,并引入参数化设计的基本概念,为后续章节深入探讨奠定基础。

## 参数化设计概念

参数化设计是一种设计方法,允许设计人员在不更改代码结构的前提下,通过改变参数值来定制化硬件模块的功能或性能。它提高了设计的灵活性和复用性,特别适合于对硬件模块进行系列化设计和快速迭代。参数化设计为FPGA设计人员提供了一个强大而灵活的设计工具,尤其是在处理具有多种配置或性能要求的复杂电路时。

在Quartus环境下进行参数化设计可以带来以下优势:

- **灵活性**:通过参数调整,同一代码模块可以用于不同的应用场景。

- **可维护性**:参数化设计使得硬件设计更加模块化,便于管理和后续维护。

- **性能优化**:参数化的模块可以通过优化参数值来调整性能,满足不同性能需求。

参数化设计与传统设计方法相比,最显著的区别在于其更高的灵活性和重用性。在下一章,我们将深入探讨参数化设计的基础知识,了解其原理和如何在Quartus中实施。

# 2. 参数化设计的基础知识

### 2.1 参数化设计的原理

#### 2.1.1 参数化设计在FPGA开发中的意义

参数化设计是一种让设计模块能够根据参数配置来适应不同需求的方法。在FPGA开发中,由于其灵活的硬件可重配置性,参数化设计尤为重要。利用参数化设计,可以使得同一个模块能够适应不同的应用场景,简化设计流程,提高设计的复用性和灵活性。此外,参数化设计有助于提升开发效率,因为开发者可以在不重新编写代码的情况下,通过调整参数来实现不同的硬件功能,从而缩短了从设计到验证的时间。

#### 2.1.2 参数化设计与传统设计方法的比较

传统的FPGA设计方法往往依赖于硬编码,每增加一种新的配置需求,就需要重新编写或者修改现有的设计代码,这样的方法会导致代码的冗余和管理的复杂性增加。与之相比,参数化设计通过参数来控制模块的功能和行为,使得同一个模块能够实现更加广泛的逻辑功能。从可维护性和可扩展性的角度来看,参数化设计提供了更高的灵活性,减少了代码的重复编写,且使模块易于理解和测试。

### 2.2 参数化设计的语法和结构

#### 2.2.1 参数和端口的声明方式

在参数化设计中,参数的声明是基础。在硬件描述语言(HDL)中,如VHDL或Verilog,参数通常是使用特定的关键字来声明的。在Verilog中,参数可以通过`parameter`关键字来声明,并且可以在模块内部定义参数的默认值。例如:

```verilog

module parametrized_module #(

parameter WIDTH = 8, // 参数WIDTH默认值为8

parameter DEPTH = 16 // 参数DEPTH默认值为16

)(

input [WIDTH-1:0] data_in,

output [DEPTH-1:0] data_out

);

// 模块体

endmodule

```

在上面的代码中,`WIDTH`和`DEPTH`就是参数化的实例,它们控制着数据输入输出的位宽。

#### 2.2.2 实例化参数化模块的技巧

在实例化参数化模块时,可以传递新的参数值以覆盖默认参数。这样做的好处是,可以在不同的实例中复用同一模块,但又可以为每个实例指定不同的参数,从而增加设计的灵活性。

例如,如果想要创建一个输入输出位宽都是4的实例,可以在模块的实例化时指定参数值:

```verilog

parametrized_module #(4, 4) my_instance (

.data_in(data_in), // 传递输入数据

.data_out(data_out) // 传递输出数据

);

```

#### 2.2.3 参数的有效范围和约束条件

参数的有效范围是设计者在声明参数时必须考虑的。在Verilog中,参数只可以在模块定义时声明,并且在模块的实例化时可以被覆盖。它们不能在模块内部的`always`或`initial`块中被重新赋值。参数的约束条件是开发过程中对参数取值的限制,例如位宽参数应该为正整数,这样的约束能够确保模块的正确实现。

### 2.3 参数化设计的高级特性

#### 2.3.1 生成语句(generate)的使用

生成语句(`generate`)是Verilog中一个重要的特性,用于根据参数值动态生成硬件结构。使用生成语句可以针对不同参数值条件来重复实例化相同的模块,或者生成不同数量的模块实例。例如:

```verilog

generate

if (PARAMETER > 10) begin : gen_block

// 如果PARAMETER大于10,则实例化两个模块实例

parametrized_module #(.WIDTH(8), .DEPTH(16)) inst0 (...);

parametrized_module #(.WIDTH(8), .DEPTH(16)) inst1 (...);

end else begin : gen_block_else

// 如果PARAMETER不大于10,则实例化一个模块实例

parametrized_module #(.WIDTH(8), .DEPTH(16)) inst0 (...);

end

endgenerate

```

在这个例子中,`generate`语句根据`PARAMETER`的值来决定是创建一个还是两个实例。

#### 2.3.2 类型转换和类型推断

在参数化设计中,对参数类型的准确处理是至关重要的。类型转换指的是将一种数据类型强制转换为另一种数据类型的过程,这在HDL中通常通过内置函数或系统函数来完成。类型推断是编译器根据上下文推断数据类型的能力,这在参数化设计中可以减少不必要的类型声明,使得代码更加简洁和灵活。

#### 2.3.3 高层次参数化结构设计

参数化不仅仅局限于单个模块内部,还可以应用于更复杂的设计结构。高层次参数化结构设计允许开发者对整个系统的参数进行配置,这样可以在更高层次上调整设计的规模、性能和功耗等属性。这通常涉及到复杂的条件判断和模块实例化逻辑,但可以极大地提升设计的灵活性和可扩展性。

# 3. 全加器阵列设计与优化

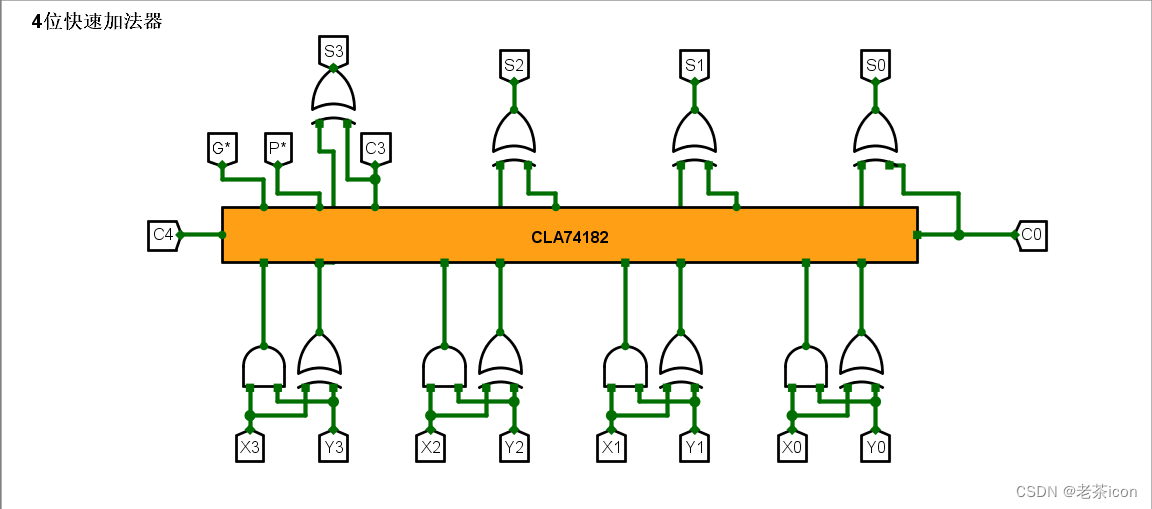

在数字电路设计领域,全加器是构建复杂算术运算的基本单元之一。随着电子设备性能要求的不断提高,如何高效地构建全加器阵列,并对其性能进行优化,成为了一个重要的技术挑战。本章将详细介绍全加器的基本原理和电路实现,参数化全加器模块的设计思路与代码实现,以及阵列结构的构建和优化方法。

## 全加器的基本原理和电路实现

### 二进制加法和全加器的逻辑功能

数字逻辑设计中,全加器是实现二进制加法的基本组件。全加器有三个输入:A、B和进位输入Cin,以及两个输出:和S和进位输出Cout。全加器需要处理三个输入的每一位的加法,同时考虑进位因素。

全加器的逻辑功能可以用以下布尔表达式表示:

- 和 S = A ⊕ B ⊕ Cin

- 进位 Cout = (A ∧ B) ∨ (B ∧ Cin) ∨ (A ∧ Cin)

其中,⊕ 表示异或运算,∧ 表示与运算,∨ 表示或运算。

### 全加器的基本电路设计

全加器的电路设计通常采用基本的逻辑门组合来实现。根据逻辑功能表达式,可以使用两个半加器(Half Adder)和一个或门(OR Gate)来构建全加器。半加器由一个异或门和一个与门组成,用于实现无进位加法。然后将半加器的进位输出与外部进位输入通过一个或门合并,得到最终的全加器输出。

以下是全加器基本电路的示意图:

```

A -----|异或|------|异或|----- S (和)

```

0

0