【I_O扩展与外设设计】:ACU19EG核心板接口设计要点与扩展技巧

发布时间: 2025-01-04 19:50:41 阅读量: 9 订阅数: 9

# 摘要

本论文系统探讨了ACU19EG核心板I/O扩展与外设设计的关键技术要点,深入分析了接口设计、外设扩展技巧以及接口扩展实践案例。文章首先介绍了I/O扩展与外设设计的基础概念,随后详细讨论了核心板接口设计要点,包括接口标准、电气特性、协议与信号定义、布局、布线和信号完整性分析。进一步,论文阐释了核心板外设扩展技巧,涵盖外设选型、兼容性分析、驱动开发与集成以及外设协同工作原理。最后,通过对ACU19EG核心板接口扩展实践案例的分析,提出优化建议并展望了未来发展趋势和挑战,重点关注技术进步、设计理念创新和行业应用拓展。

# 关键字

I/O扩展;外设设计;接口标准;信号完整性;驱动开发;性能优化

参考资源链接:[ALINX Zynq UltraScale+MPSoC ACU19EG核心板开发平台原理图详解](https://wenku.csdn.net/doc/118zjftews?spm=1055.2635.3001.10343)

# 1. I/O扩展与外设设计基础概念

## 1.1 I/O 扩展的重要性

在现代信息技术领域中,I/O扩展是指通过增加接口来提升设备的输入输出能力,这对于满足多样化的应用场景至关重要。合理的I/O扩展不仅能够提高系统的数据处理能力,还能通过增加对外设的兼容性来提升整体性能和用户的工作效率。

## 1.2 外设设计的基础原则

外设设计通常遵循几个基本原则:首先,外设必须与核心板的接口标准相匹配;其次,需要考虑信号的完整性和传输速度;最后,外设的选型应兼顾成本和功能。设计时还需确保外设在物理空间上的合理布局,以保证系统的稳定性与可靠性。

## 1.3 设计流程概述

设计I/O扩展和外设的过程涉及到需求分析、接口匹配、信号定义、布局优化和最终的测试验证。这需要设计师具备丰富的硬件知识,同时也需要良好的软件支持来确保接口驱动的兼容性和稳定性。

通过下面的章节,我们将深入探讨ACU19EG核心板的接口设计要点以及外设扩展技巧,并分享实际案例分析和优化建议,以帮助设计师更好地理解和应用这些核心概念。

# 2. ACU19EG核心板接口设计要点

### 2.1 核心板I/O接口标准

#### 2.1.1 接口电气特性

I/O接口的电气特性是决定核心板与外设兼容性的基础,它包括信号的电平、驱动能力、容抗以及抗干扰能力等参数。对于ACU19EG核心板而言,理解其接口电气特性是设计的关键。

首先,电平标准是衡量接口兼容性的基本准则。常见的电平标准有TTL(晶体管-晶体管逻辑)和CMOS(互补金属氧化物半导体)电平,它们在电压范围、电流驱动能力等方面有明显差异。例如,TTL电平通常在0V到5V之间变化,而CMOS电平可以支持更低或更高的电压范围,如3.3V或1.8V。

其次,信号的驱动能力决定了信号在传输过程中的稳定性和可达性。驱动能力强的接口可以驱动更长的信号线或者更复杂的负载。在设计时,需要考虑信号的驱动电流、负载电容等因素。

容抗是信号传输中一个不可忽视的因素,它与频率成反比,频率越高,容抗越低。设计时,需要确保信号的上升沿和下降沿足够快,以减少高频信号的失真。

抗干扰能力则关系到接口在复杂电磁环境下的表现。在设计中,通常通过屏蔽、滤波以及差分信号传输等技术手段,来提高接口的抗干扰能力。

在实际应用中,ACU19EG核心板的I/O接口应遵守相应的电气特性标准,这样可以确保接口与外设的兼容,同时避免信号质量下降。

```markdown

电平标准示例:

| 标准类型 | 逻辑"1"电压 | 逻辑"0"电压 | 应用场景 |

|----------|-------------|-------------|----------|

| TTL | 2.4V-5V | 0V-0.4V | 通用数字接口 |

| CMOS | 3.3V/1.8V | 0V | 低功耗设计 |

```

### 2.1.2 接口协议和信号定义

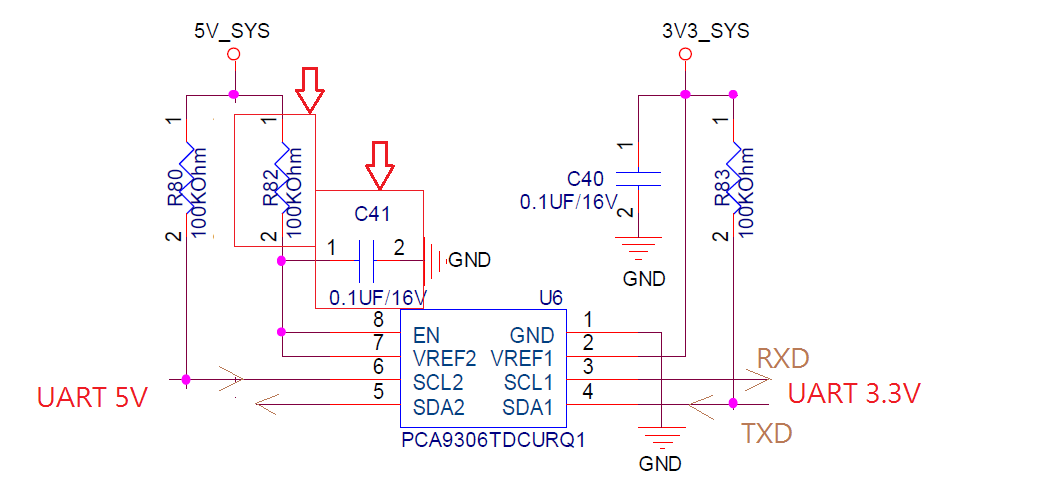

接口协议定义了信号的时序关系、传输模式和通信规则。对于ACU19EG核心板来说,了解和应用正确的接口协议是实现与外设无缝连接的前提。常见的接口协议有SPI(串行外设接口)、I2C(两线式串行总线)、UART(通用异步收发器)等。

在设计中,每个接口协议都有其独特的信号定义。例如,SPI接口定义了四个基本信号线:MISO(主设备输入/从设备输出)、MOSI(主设备输出/从设备输入)、SCLK(时钟信号)、CS(片选信号)。而I2C接口则只有两根线:SDA(数据线)、SCL(时钟线)。

这些信号的定义决定了数据如何在核心板和外设之间传输。协议规范通常还会定义信号的电平要求、时序要求以及数据帧的格式。例如,SPI协议中数据是同步传输的,且主设备提供时钟信号;I2C协议则采用多主总线结构,允许多个主设备在总线上通信。

在设计核心板时,需要详细阅读和遵守相关接口协议规范,这样在对接外设时才能实现正确的信号交互和数据传输。

```markdown

SPI协议信号时序示例:

| 信号名称 | 说明 |

|----------|----------------------------|

| MISO | 主设备从从设备读取数据 |

| MOSI | 主设备向从设备写入数据 |

| SCLK | 时钟信号,由主设备产生 |

| CS | 片选信号,用于选择从设备 |

```

### 2.2 核心板扩展接口的布局和设计

#### 2.2.1 扩展槽和接插件的选择

核心板扩展接口的布局是实现系统功能扩展的关键一环。正确选择扩展槽和接插件对于确保系统稳定性和扩展性至关重要。扩展槽和接插件的选择要考虑电气特性、机械强度、接口密度以及信号完整性等因素。

在设计ACU19EG核心板时,选择合适的扩展槽和接插件是优化布局的第一步。扩展槽的种类繁多,常用的有PCIe、PCI、Mini PCI等。这些扩展槽的选择取决于需要扩展的外设类型,以及核心板的整体设计。

接插件作为连接扩展槽与外设的桥梁,其质量直接关系到信号传输的稳定性和可靠性。例如,USB接口有Type-A、Type-B、Mini USB和Micro USB等多种类型,各自有特定的应用场景和物理尺寸。

扩展槽和接插件的布局设计需要综合考虑电路板的空间利用、信号路径、电源管理以及热管理等众多因素。在空间有限的情况下,设计紧凑型接口并采用高密度封装技术成为必然选择。同时,布局设计还需要考虑电磁兼容性(EMC)问题,以减少信号间的相互干扰。

```markdown

扩展槽和接插件选择指南:

| 类型 | 应用场景 | 特点 |

|------------|-------------------------|------------------------|

| PCIe | 高速数据通信扩展 | 传输速率高,支持热插拔 |

| Mini PCI | 内置无线通信模块 | 体积小巧,连接稳定 |

| USB Type-A | 通用外设连接 | 标准化接口,广泛使用 |

```

#### 2.2.2 布线和信号完整性分析

布线和信号完整性分析是确保接口设计可靠性的必要环节。不合理的布线会导致信号时序问题、信号反射、串扰以及信号衰减等问题,严重影响系统性能。

在进行布线设计时,需要遵循信号传输的基本原则。例如,高速信号线应尽可能短,避免90度转角,适当增加线宽等。这些措施有助于减少信号传播的延迟和衰减。

信号完整性分析则需要借助专业的EDA(电子设计自动化)工具进行。这些工具能够模拟信号在电路中的传播过程,预测可能的信号质量问题。分析结果可以用来调整布局和布线,以优化信号完整性。

此外,设计时还应考虑到电源和地线的布线,因为它们为信号线提供回流路径。一个良

0

0