FPGA时序约束秘籍:避免设计错误与陷阱全攻略

发布时间: 2025-01-06 12:16:46 阅读量: 9 订阅数: 16

小梅哥FPGA时序约束从遥望到领悟详解

# 摘要

本文深入探讨了FPGA时序约束的基础知识、理论与实践、避免设计错误的策略、高级技术以及优化技巧,旨在提升设计者在多时钟域和异步交互等复杂场景下的设计能力。文章首先介绍了时序约束的基本概念,随后分析了其在实际设计中的应用,如时钟网络、Setup和Hold时间等,并详细讨论了约束文件编写、时钟交互和验证方法。在避免设计错误的策略章节中,文章通过案例分析了常见错误及其影响,并提出了一系列预防和改正的方法。高级时序约束技术章节强调了多时钟域处理和异步时钟域交互的挑战和解决方案。最后,文章探讨了优化技巧和行业未来趋势,为FPGA设计师提供了全面的技术支持和视角。

# 关键字

FPGA;时序约束;多时钟域;异步时钟交互;时钟网络;Setup/Hold时间

参考资源链接:[自注意力机制与FPGA时序约束的Transformer模型详解](https://wenku.csdn.net/doc/4ztxfteduj?spm=1055.2635.3001.10343)

# 1. FPGA时序约束基础知识

在FPGA(现场可编程门阵列)的设计中,时序约束是保证电路正确运行的重要因素。本章将介绍时序约束的基本概念,这是任何希望在FPGA设计中达到高质量时序结果的工程师必须掌握的基础知识。

## 什么是时序约束?

时序约束,也称为时序约束(Timing Constraints),是指在FPGA设计过程中,为确保信号能正确地在规定的时间内到达目的地,而对设计进行的一系列限制和规则。这些约束包括定义时钟域、规定信号路径的延迟、设置时钟频率等。正确地应用时序约束能够帮助设计满足时序要求,避免数据丢失或损坏。

## 时序约束的必要性

没有正确的时序约束,设计可能在实际硬件上运行不稳定,甚至完全无法工作。时序约束能够指导布局布线(Place & Route)工具,优化FPGA内部的信号路径,以满足时序要求。它们还能够提供时序分析的基准,从而使工程师能够识别设计中的潜在问题,并采取措施进行改进。

## 理解时序约束的基本类型

在FPGA设计中,最基本的时序约束类型包括:

- **时钟约束**:定义了设计中使用的时钟信号的属性,如频率和占空比,以及不同时钟域之间的关系。

- **输入/输出延迟约束**:确保数据在到达FPGA输入端或从输出端送出之前,能够在规定的时间内稳定。

- **最小和最大延迟约束**:对信号路径的延迟进行限制,避免数据在芯片内传输过快或过慢。

掌握了这些基础知识之后,我们就可以深入探讨更高级的时序约束理论,并在实际应用中提高FPGA设计的性能和稳定性。接下来的章节将详细介绍时序约束的理论与实践,让读者更好地理解时序约束的重要性及其在设计中的实际应用。

# 2. 时序约束的理论与实践

## 2.1 时序约束的理论基础

### 2.1.1 时钟域和时钟网络

在数字设计中,时钟域指的是在特定时钟信号控制下运行的一组逻辑或触发器。正确地管理时钟域是确保设计成功的关键。每个时钟域有自己的时钟信号,并通过时钟网络进行分配。时钟网络设计的效率直接影响了时钟信号的质量和FPGA内部电路的工作稳定性。

时钟域之间的转换(也称为时钟域交叉,CDC)是时序约束中的一个关键话题。理想情况下,同一个时钟域内的信号应该在同一时钟边沿上同步。然而,在实际设计中,通常需要在多个时钟域之间传递数据。不正确的时钟域交叉可能会引起数据冒险和时序问题,比如数据可能在时钟边沿不稳定时被采样,导致逻辑错误。

### 2.1.2 Setup和Hold时间

Setup和Hold时间是时序约束中的基本概念,它们决定了触发器能够正确捕获输入信号的条件。

- **Setup时间**:在触发器的时钟边沿到来之前,输入信号必须稳定地保持在预期的逻辑状态的最小时间长度。如果输入信号改变得太接近时钟边沿,触发器可能无法正确地捕获这一变化,结果可能是逻辑错误。

- **Hold时间**:在触发器的时钟边沿之后,输入信号必须保持稳定状态的最小时间长度。如果输入信号在时钟边沿后很短的时间内改变,可能会引起触发器的误动作。

理解并合理设置setup和hold时间对于避免时序问题至关重要。时序分析工具通常会检查所有信号路径,确保它们满足时序要求。

## 2.2 时序约束的实践应用

### 2.2.1 约束文件编写技巧

在FPGA设计中,约束文件(如XDC文件)用于定义时序要求。编写约束文件需要遵循一定的格式和规则。以下是一些关键的编写技巧:

- **准确性**:确保所有时钟、输入输出延迟、多周期路径等都已明确声明,并且准确反映了设计意图。

- **完整性**:约束文件应覆盖所有需要的时序路径,包括可能被遗漏的异步信号路径。

- **简洁性**:尽量简化约束的编写,避免复杂的条件和冗长的说明,使得约束文件易于理解和维护。

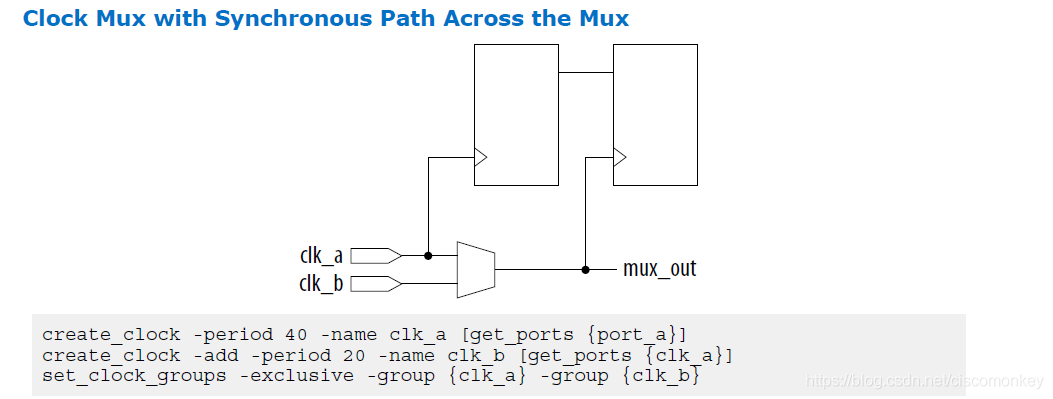

### 2.2.2 时钟约束与时钟交互

在时钟约束中,必须确保所有的时钟信号都有明确的定义,包括时钟频率、占空比和相位偏移等。此外,时钟交互是一个重要的概念,特别是当涉及到时钟门控、时钟分频器或时钟倍频器时。

在多时钟域设计中,需要特别注意异步时钟域的交互。例如,数据从一个时钟域传送到另一个时钟域时,就需要采用诸如双触发器或多时钟域同步器等机制来避免时序问题。

### 2.2.3 约束验证方法

约束文件编写完成后,需要验证其正确性。常用的验证方法包括:

- **静态时序分析(STA)**:使用STA工具对设计进行分析,检查所有路径是否满足setup和hold时间的要求。

- **时钟域交叉分析**:对跨时钟域的数据路径进行专门分析,确保它们是安全的,并且没有潜在的冒险。

- **仿真验证**:通过运行功能仿真和时序仿真来验证约束文件的实际效果,确保电路在各种工作条件下都能正确运行。

通过这些验证方法可以确保时序约束既符合设计要求,也能在实际硬件中正确实现。代码块、表格和流程图将在下文提供以进一步阐述这些概念。

# 3. 避免设计错误的时序约束策略

### 3.1 设计错误案例分析

设计错误在FPGA开发中是不可避免的,但它们对项目的影响是可以降低的。理解错误的类型、原因和后果是预防的第一步。

#### 3.1.1 常见设计错误类型

在FPGA设计中,时序约束错误通常可以分为两类:基本时序错误和高级时序错误。

1. **基本时序错误**,包括未正确设置时钟约束、时钟域交叉错误、以及不匹配的时钟频率等。

- 这些错误往往源于对时钟网络和时钟域交互的不充分理解。例如,一个时钟域的数据没有正确地传递到另一个时钟域,或者为高速时钟分配了错误的时钟频率。

2. **高级时序错误**,可能包括特殊路径约束不足或不当,以及在设计中未考虑的时序异常情况。

- 高级错误通常更难以发现,因为它们可能出现在复杂的设计逻辑中,如多时钟

0

0