【挑战与对策】Cadence Virtuoso SPICE网表导入全解析

发布时间: 2024-12-14 09:27:33 阅读量: 3 订阅数: 6

参考资源链接:[Cadence Virtuoso SPICE网表导入指南](https://wenku.csdn.net/doc/6412b700be7fbd1778d48bc3?spm=1055.2635.3001.10343)

# 1. Cadence Virtuoso SPICE网表导入概述

## 1.1 Cadence Virtuoso SPICE简介

Cadence Virtuoso是电子设计自动化领域内一个广泛使用的集成电路设计软件套件,它提供了从电路设计到验证的全流程支持。SPICE(Simulation Program with Integrated Circuit Emphasis)是一个用于模拟电子电路的软件程序,它以网表(netlist)形式来描述电路的连接关系。通过SPICE网表,设计者能够模拟电路的性能,进而进行分析和优化。

## 1.2 SPICE网表在Virtuoso中的作用

在Cadence Virtuoso中,SPICE网表的导入是一个关键步骤,因为它允许设计者将电路设计以一种标准格式输入到仿真环境中。这一步骤不仅涉及到了从其他设计工具到Virtuoso环境的转换,也涉及到确保电路描述的精确性和完整性,从而保证后续仿真和分析的准确性。

## 1.3 导入流程的重要性

理解并掌握SPICE网表导入流程的重要性在于,它直接影响到电路设计的仿真结果和后续的验证工作。导入流程中的错误可能导致仿真结果偏差,甚至设计失败,因此熟悉导入流程的每一个环节,对于提高设计效率和质量至关重要。

# 2. Cadence Virtuoso SPICE网表结构理论

## 2.1 SPICE网表的组成元素

### 2.1.1 设备模型和参数定义

在SPICE网表中,设备模型是指构成电路的各种元件模型,包括电阻、电容、二极管、晶体管等。每个设备模型都有其特定的参数定义,这些参数定义了元件的电气特性。例如,一个NMOS晶体管模型会有参数如宽度(W)、长度(L)、阈值电压(Vth)等。

**参数定义示例:**

```spice

M1 (D1 D2) 0 NMOS W=1u L=0.5u

```

在这个示例中,`M1`是晶体管的实例名,`D1`和`D2`是连接到晶体管的两个节点,`NMOS`表示是N型MOSFET,`W=1u`和`L=0.5u`分别定义了晶体管的宽度和长度。

**参数的含义:**

- `W`:晶体管沟道的宽度。

- `L`:晶体管沟道的长度。

**表格展示参数对模型的影响:**

| 参数 | 描述 | 影响 |

| --- | --- | --- |

| W | 晶体管沟道宽度 | 影响晶体管电流大小 |

| L | 晶体管沟道长度 | 影响晶体管开启电压 |

| Vth | 阈值电压 | 决定晶体管导通与否 |

正确理解并设置这些参数对于模拟电路的准确性至关重要。在实际操作中,工程师们通常会根据器件数据手册或实验数据来定义这些参数。

### 2.1.2 网络列表和连接性描述

网络列表是SPICE网表中描述元件之间连接方式的部分,它定义了电路中各个节点之间的连接关系。网络列表是通过列出元件之间的连接点来形成的,每一个连接点称为一个节点。

**网络列表示例:**

```spice

* Netlist section

V1 in gnd 5V

R1 in out 1k

C1 out gnd 0.1u

```

在这个例子中:

- `V1`是一个电源,连接在节点`in`和`gnd`之间,提供5伏的电压。

- `R1`是一个1kΩ的电阻,连接在节点`in`和`out`之间。

- `C1`是一个0.1微法拉的电容,连接在节点`out`和`gnd`之间。

**mermaid格式流程图描述连接性:**

```mermaid

graph LR

A[in] -->|V1| B[gnd]

A -->|R1| C[out]

C -->|C1| D[gnd]

```

节点之间的连接性描述实际上定义了电路的拓扑结构,这直接影响电路的行为和特性。正确地表达这些连接关系是电路模拟中至关重要的一步,这要求工程师对电路设计有深入的理解。

## 2.2 SPICE网表的语法规范

### 2.2.1 关键字和语法结构

SPICE网表的语法规范对模拟电路的正确解析至关重要。SPICE网表包含一系列的指令,用以描述电路的组成、参数、模拟条件等。SPICE的关键字包括`V`, `I`, `R`, `C`, `L`, `M`, `D`, `X`等,分别代表电压源、电流源、电阻、电容、电感、MOSFET晶体管、二极管和子电路。

**示例代码块:**

```spice

* SPICE netlist

.model NMOSMOD nmos (level=1 Vto=0.7 kp=1.2e-5 gamma=0.5 phi=0.6)

M1 out in gnd gnd NMOSMOD W=1u L=0.5u

```

**参数解释:**

- `.model NMOSMOD nmos` 定义了一个名为`NMOSMOD`的NMOS晶体管模型。

- `level=1` 指定MOSFET模型的级别。

- `Vto=0.7` 指定阈值电压为0.7V。

- `kp=1.2e-5` 指定跨导参数。

- `M1` 是一个晶体管实例,使用了`NMOSMOD`模型,并设置了其尺寸。

### 2.2.2 版本差异和兼容性问题

SPICE的网表格式从20世纪70年代开始发展,随着时间的推移,SPICE经历了多个版本的更新和发展。不同的SPICE模拟器和版本可能在语法和功能上存在差异,这可能导致在导入和模拟时出现兼容性问题。

**版本差异示例:**

```spice

* SPICE v2g format

R1 1 2 1K

* SPICE v3f format

R1 1 2 value=1K

```

如上所示,SPICE v2g版本使用两个节点编号来定义电阻,而SPICE v3f版本则开始支持使用`value`关键字。

**兼容性问题解决策略:**

为了解决这些兼容性问题,通常需要:

- 确保使用与目标模拟器兼容的网表格式。

- 对于复杂的电路设计,使用版本控制和模拟器测试,来识别和解决潜在的兼容性问题。

- 在进行电路设计时,遵循最佳实践和标准化的编码指南。

## 2.3 SPICE网表的设计意图解析

### 2.3.1 设计者的意图理解

理解设计者的意图是分析SPICE网表的一个重要方面。设计者的意图往往体现在他们选择的元件、设定的参数以及整体的电路布局中。

**意图理解的重要性:**

- 确保模拟结果符合预期。

- 避免在模拟过程中出现错误或偏差。

**理解设计者意图的步骤:**

- 分析电路图:仔细研究电路图,理解每个元件的作用和电路的拓扑结构。

- 询问设计者:在必要时,直接询问设计者或查阅设计文档。

- 验证假设:对理解的设计意图进行仿真验证,确保没有误解。

### 2.3.2 设计约束和性能目标

设计约束包括了设计在频率、功耗、尺寸、成本等方面的限制条件。性能目标则是在这些约束下的预期性能指标,如增益、带宽、稳定性等。

**设计约束示例:**

- 设计者可能要求一个放大器在特定频段内的增益不低于X分贝。

- 设计者可能需要限制电路的工作电压范围以满足电源管理的要求。

**表格展示设计约束和性能目标:**

| 设计约束 | 性能目标 | 描述 |

| --- | --- | --- |

| 工作频率范围 | 增益不小于X分贝 | 保证电路在指定频段内有适当的增益 |

| 功耗限制 | 能效比大于Y | 实现高效能,节能设计 |

| 尺寸限制 | 芯片面积小于Z平方毫米 | 小型化设计以适应紧凑空间 |

这些约束和目标通常在设计初期就确定,并在设计过程中不断迭代优化以确保实现。在SPICE模拟中,这些约束和目标会转换为具体的模拟设置和性能分析的参考标准。

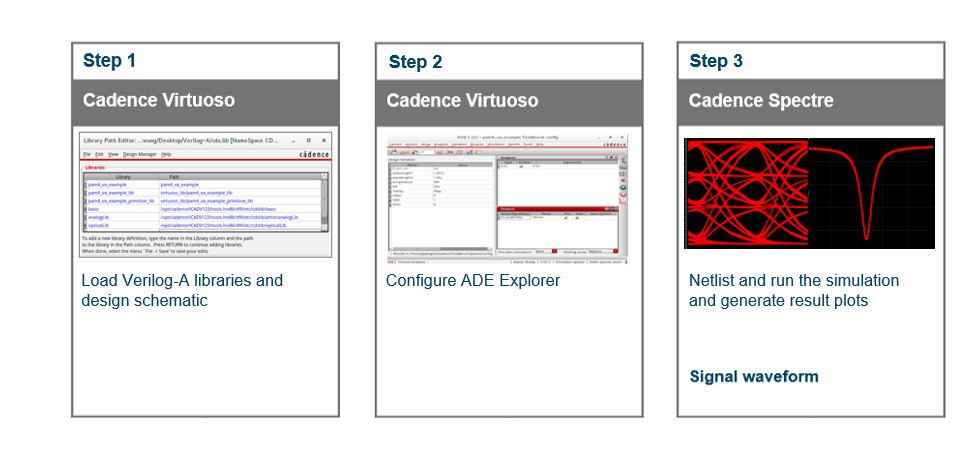

# 3. Cadence Virtuoso SPICE网表导入实践

## 3.1 网表导入前的准备工作

### 3.1.1 环境配置和工具安装

在开始导入Cadence Virtuoso SPICE网表之前,确保你的工作环境已经配置好所需的软件和硬件。对于大多数设计师来说,这意味着需要安装Cadence Virtuoso软件套件,这通常包括Layout编辑器、Schematic捕获工具以及用于仿真和验证的工具,如Spectre或HSPICE。

确保操作系统满足软件的最小系统要求,并且所有相关的许可证文件已经配置好。此外,可能还需要安装特定的仿真模型库,以便正确处理特定的半导体元件。例如,对于CMOS工艺,应安装对应的BSIM模型。

还需检查系统资源,如内存和处理器速度,以确保在进行复杂电路仿真时不会遇到性能瓶颈。建议的硬件配置随着设计复杂度的增加而提高。

#

0

0