1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

AA

BB

CC

DD

HSYNC

L_CTRL_DATA

PHL_CLK

PHL_DATA

PEG_COMP

LVDS_IBG

TXLCLKOUT+

TXLCLKOUT-

TXLOUT0-

TXLOUT0+

TXLOUT2-

TXLOUT2+

TXLOUT1-

TXLOUT1+

INT_TV_Y/G

INT_TV_C/R

INT_TV_COMP

VSYNC

L_CTRL_CLK

CRT_R

CRT_G

CRT_B

+SMDDR_VREF_NB

CLKREQ#_MCH

SDVO_CTRLCLK

DREFCLK

PECLK_3GPLL

DREFSSCLK#

PECLK_3GPLL#

DREFSSCLK

SDVO_CTRLDATA

DREFCLK#

SM_PWROK

MCH_CFG19

MCH_CFG20

SM_RCOMP_VOH

SM_RCOMP_VOL

TSATN#

MCH_CFG13

MCH_CFG12

MCH_CFG16

SM_REXT

SMRCOMPP

SMRCOMPN

PM_EXTTS#0

PM_EXTTS#1

MCH_CFG7

MCH_CFG5

RSTIN#_MCH

MCH_CLVREF

DDPC_CTRLCLK

DDPC_CTRLDATA

MCH_CLVREF

SMRCOMPN

SMRCOMPP

CRT_G

CRT_R

CRT_B

SM_RCOMP_VOL

+SMDDR_VREF_NB

PM_EXTTS#0

PM_EXTTS#1

TSATN#

L_CTRL_CLK

L_CTRL_DATA

LVDS_IBG

INT_TV_Y/G

INT_TV_C/R

INT_TV_COMP

SM_REXT

CRT_IREF

DDPC_CTRLCLK

DDPC_CTRLDATA

CRT_IREF

SDVO_CTRLCLK

SDVO_CTRLDATA

PHL_DATA

PHL_CLK

HDA_SDIN_HDMI

HDA_RST#_HDMI

HDA_SYNC_HDMI

HDA_SDOUT_HDMI

HDA_BIT_CLK_HDMI

PEG_TXP0

PEG_TXP2

PEG_TXP1

PEG_TXN0

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXP3

SM_RCOMP_VOH

CLKREQ#_MCH

SM_PWROK

+SMDDR_VREF_NB

PHL_DATA(22)

PHL_CLK(22)

INT_LVDS_PWM(22)

INT_LVDS_BLON(22)

INT_LVDS_DIGON(22)

TXLCLKOUT+(22)

TXLCLKOUT-(22)

TXLOUT0-(22)

TXLOUT0+(22)

TXLOUT2-(22)

TXLOUT2+(22)

TXLOUT1-(22)

TXLOUT1+(22)

M_CLK_DDR1 (16)

M_CLK_DDR#1 (16)

DELAY_VR_PWRGOOD(4,14,25)

M_CKE1 (16)

M_CS#1 (16)

MCH_BSEL0(3)

MCH_BSEL1(3)

MCH_BSEL2(3)

PM_SYNC#(14)

PM_EXTTS#0(16)

DPRSLPVR(14,25)

H_DPRSTP#(4,12,25)

M_CS#0 (16)

M_CKE0 (16)

M_CLK_DDR#0 (16)

M_CLK_DDR0 (16)

M_ODT0 (16)

DMI_MTX_IRX_P0 (13)

DMI_MTX_IRX_P1 (13)

DMI_MTX_IRX_P2 (13)

DMI_MTX_IRX_P3 (13)

ICH_CL_RST0# (14)

MPWROK (14,18)

MCH_ICH_SYNC# (14)

DREFSSCLK (3)

DREFSSCLK# (3)

DREFCLK# (3)

DREFCLK (3)

PECLK_3GPLL# (3)

PECLK_3GPLL (3)

CL_CLK0 (14)

CL_DATA0 (14)

DMI_MRX_ITX_N0 (13)

DMI_MRX_ITX_N1 (13)

DMI_MRX_ITX_P0 (13)

DMI_MRX_ITX_P1 (13)

DMI_MTX_IRX_N0 (13)

DMI_MTX_IRX_N1 (13)

DMI_MRX_ITX_N2 (13)

DMI_MRX_ITX_N3 (13)

DMI_MRX_ITX_P2 (13)

DMI_MRX_ITX_P3 (13)

DMI_MTX_IRX_N2 (13)

DMI_MTX_IRX_N3 (13)

M_ODT1 (16)

PLTRST#(13,18,19,21)

PM_THRMTRIP#(4,12)

CLKREQ#_MCH (3)

CRT_B(21)

CRT_G(21)

CRT_R(21)

VGAHSYNC(21)

VGAVSYNC(21)

M_CLK_DDR3 (16)

M_CLK_DDR#3 (16)

M_CKE3 (16)

M_CS#3 (16)

M_CLK_DDR2 (16)

M_CLK_DDR#2 (16)

M_ODT3 (16)

M_CS#2 (16)

M_ODT2 (16)

M_CKE2 (16)

PM_EXTTS#1(16)

GFX_VR_EN (29)

GPU_VID4 (29)

GPU_VID1 (29)

GPU_VID2 (29)

GPU_VID3 (29)

GPU_VID0 (29)

HDA_SDOUT_HDMI (12)

HDA_SDIN_HDMI (12)

HDA_BIT_CLK_HDMI (12)

HDA_SYNC_HDMI (12)

HDA_RST#_HDMI (12)

HDMI_HP_IV# (22)

DDCDATA(21)

DDCCLK(21)

SDVO_CTRLCLK (22)

SDVO_CTRLDATA (22)

HDMITX0P (22)

HDMICLKP (22)

HDMITX2P (22)

HDMITX1P (22)

HDMITX2N (22)

HDMITX0N (22)

HDMITX1N (22)

HDMICLKN (22)

DDR3_RST# (16)

HWPG_+1.5V_SUS(18,26)

SUSON(18,26,28)

+1.05V

+1.05V

+1.5V_SUS

+1.5V_SUS

+SMDDR_VREF

+3V

+1.05V

+3V

+3V

+3V_S5

+1.5V_SUS

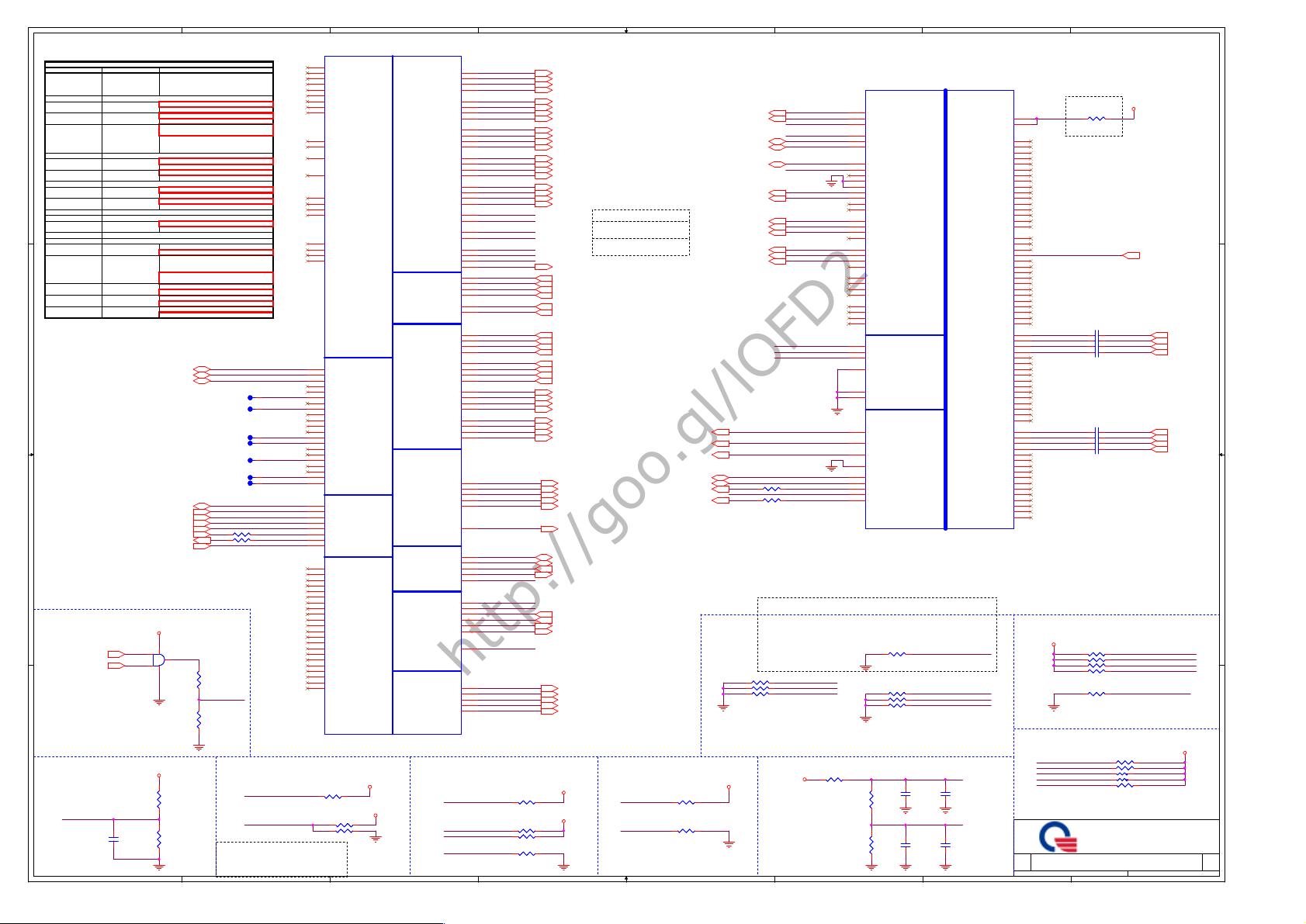

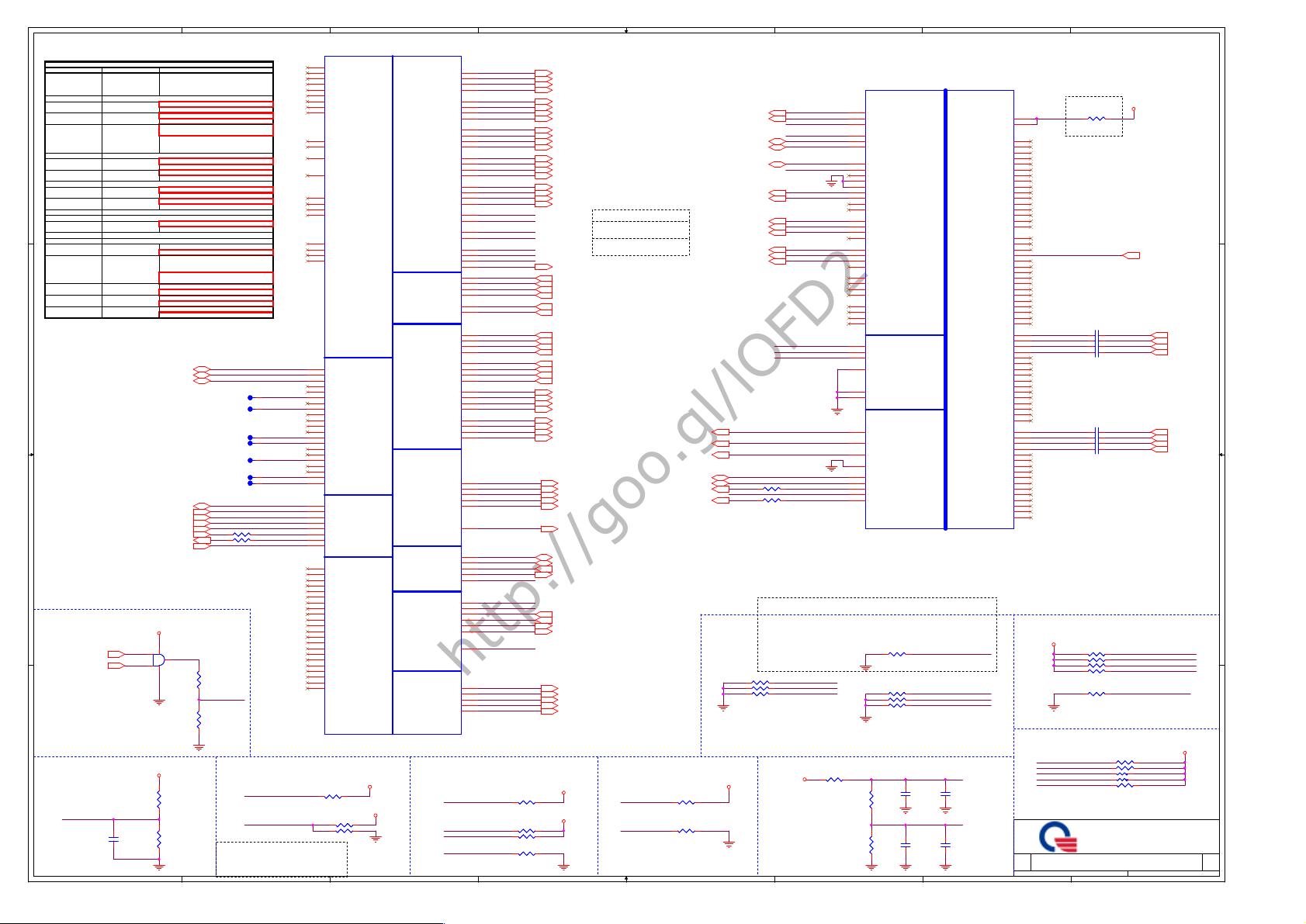

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

Cantiga SFF (DMI/VGA)

1A

7 32Tuesday, September 29, 2009

ZE8

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

Cantiga SFF (DMI/VGA)

1A

7 32Tuesday, September 29, 2009

ZE8

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

Cantiga SFF (DMI/VGA)

1A

7 32Tuesday, September 29, 2009

ZE8

(15mils)

Check list note : CL_REF=0.35V

(20mils)

<Checklist ver0.8>

If TSATN# is not used, then it must be terminated

with a 56-Ω pull-up resistor to VCCP.

CRT setting LVDS setting

Cantiga SFF - DMI/VGA (CLG)

0 = Reverse Lanes

0 = Intel Management Engine Crypto Transport

1 = Intel Management Engine Crypto TLS

Reserved

Pin Name Strap Description Configuration

CFG2:0 FSB Frequency

DDPC_CTRLDATA

CFG10

Digital Display

0 = Digital display (iHDMI/DP) interface absent

1 = Digital display (iHDMI/DP) devide present

Present

enable

0 = Digital DisplayPort (SDVO/DP/iHDMI) or

1 = Disabled

0 = Enabled

PCIE are operational

CFG4:3

Engine Crypto Strap

CFG5

cipher suite with confidentiality

DMI x2 Select

0 = DMI x2

CFG11 Reserved

PCIE Loopback

CFG12 ALLZ 1 = Disabled

0 = ALLZ mode enabled

CFG19 DMI Lane Reversal 1 = Reverse Lanes

0 = Normal operation : Lane Numbered in Order

CFG13 XOR 1 = Disabled

0 = XOR mode enabled

SDVO_CTRLDATA

CFG14 Reserved

CFG15 Reserved

1 = DMI x 4

CFG20

Digital DisplayPort

CFG16 FSB Dynamic ODT

1 = Digital DisplayPort (SDVO/DP/iHDMI) and

1 = Dynamic ODT enabled

(SDVO/DP/iHDMI)

CFG6

0 = Dynamic ODT disabled

ITPM Host Interface

CFG17 Reserved

1 = ITPM disabled

0 = ITPM enabled

000 = FSB1066

010 = FSB800

011 = FSB667

Other = Reserved

SDVO Present

Concurrent with

CFG18 Reserved

0 = No SDVO/HDMI/DP interface disabled

PCIE

CFG8

1 = SDVO/HDMI/DP interface enabled

Reserved

Intel GS40/GS45 Strapping Signals and Configuration

CFG9

PCIE are operating simultaneously via the

PCIE Graphics Lane

Layer Security (TLS) cipher suite with no

PEG port

L_DDC_DATA

confidentiality

Local Flat Panel

0 = LFP Disable

1 = LFP Card Present; PCIE disabled

The recommended pull-up resistor value is 4.02 k Ω ±1%

•

The recommended pull-down resistor value is 2.21 k Ω ±1%.

•

1 = Normal operation : Lane Numbered in Order

(LFP) Present

CFG7 Intel Management

HDMI Port B

Layout notice: Place the resistor

within 500 mils (1.27 mm) of the (G)MCH.

R84:

if the total motherboard route length is less than 12",

the recommended reference resistor value is 1 K Ω ±1%

For longer route lengths between 12" - 15.3" ,

the recommended reference resistor value is 976 Ω ±1%

SM_VREF=0.5*VCC_SM

SM_PWROK only for

DDR3.(DDR2 PD only)

SM_DRAMRST# only

for DDR3.(DDR2:NC)

DDR3 RCOMP DDR3 RCOMP_VOH/VOLDDR3 VREF

At 11/19

change U21 power supply

from +3VSUS to +3V_S5

DDR3 PWROK

+SMDDR_VREF_NB.Default use voltage

divider for poor layout cause +SMDDR_VREF

not meet spec.And Intel circuit PU/PD is

1K,But Check list PU/PD is 10K.

(7/7) intel check list 360543 rev 2.0 CLKREQ# need to 10K pull high to 3.3V

R297 4.7K_4R297 4.7K_4

R95 10K_4R95 10K_4

R94 10K_4R94 10K_4

R347

12.1K/F_4

R347

12.1K/F_4

C70 0.1u/10V_4C70 0.1u/10V_4

R97 10K_4R97 10K_4

C72 0.1u/10V_4C72 0.1u/10V_4

R350 *10K/F_4R350 *10K/F_4

R292 75/F_4R292 75/F_4

R296 56_4R296 56_4

R266

1K/F_4

R266

1K/F_4

C73 0.1u/10V_4C73 0.1u/10V_4

C92 0.1u/10V_4C92 0.1u/10V_4

R269

3.01K/F_4

R269

3.01K/F_4

C74 0.1u/10V_4C74 0.1u/10V_4

R300 2.2K_4R300 2.2K_4

R111

511/F_6

R111

511/F_6

R81 30.1/F_4R81 30.1/F_4

C99 0.1u/10V_4C99 0.1u/10V_4

R301 2.2K_4R301 2.2K_4

R348

10K_4

R348

10K_4

R290 2.4K/F_4R290 2.4K/F_4

T14T14

R295 2.2K_4R295 2.2K_4

T16T16

T9T9

T10T10

R113

BLM18BA750SN1D_6

R113

BLM18BA750SN1D_6

R102 75/F_4R102 75/F_4

R293 10K_4R293 10K_4

C170

0.1u/10V_4

C170

0.1u/10V_4

U21

TC7SH08FU

U21

TC7SH08FU

1

2

4

53

R104 49.9/F_4R104 49.9/F_4

R291 75/F_4R291 75/F_4

R136 100_4R136 100_4

R272 80.6/F_4R272 80.6/F_4

C422

0.01u/25V_4

C422

0.01u/25V_4

PM

MISC

NC

CLK

DMI

CFGRSVD

GRAPHICS VID

ME

HDA

DDR CLK/ CONTROL/COMPENSATION

U18B

CANTIGASFF_1p0

PM

MISC

NC

CLK

DMI

CFGRSVD

GRAPHICS VID

ME

HDA

DDR CLK/ CONTROL/COMPENSATION

U18B

CANTIGASFF_1p0

SA_CK_0

BB32

SA_CK_1

BA25

SB_CK_0

BA33

SA_CK#_0

BA31

SA_CK#_1

BC25

SB_CK#_0

BC33

SA_CKE_0

BC35

SA_CKE_1

BE33

SB_CKE_0

BE37

SB_CKE_1

BC37

SA_CS#_0

BK18

SA_CS#_1

BK16

SB_CS#_0

BE23

SB_CS#_1

BC19

SA_ODT_0

BJ17

SA_ODT_1

BJ19

SB_ODT_0

BC17

SB_ODT_1

BE17

SM_RCOMP

BL25

SM_RCOMP#

BK26

SM_VREF

BC51

CFG_2

G25

CFG_0

K26

CFG_1

G23

CFG_3

J25

CFG_4

L25

CFG_5

L27

CFG_6

F24

CFG_7

D24

CFG_8

D26

CFG_9

J23

CFG_10

B26

CFG_11

A23

CFG_12

C23

CFG_13

B24

CFG_14

B22

CFG_15

K24

CFG_16

C25

CFG_17

L23

PM_SYNC#

J35

PM_EXT_TS#_0

J39

PM_EXT_TS#_1

L39

PWROK

AY39

RSTIN#

BB18

DPLL_REF_CLK

B42

DPLL_REF_CLK#

D42

DPLL_REF_SSCLK

B50

DPLL_REF_SSCLK#

D50

DMI_RXN_0

AG55

DMI_RXN_1

AL49

DMI_RXN_2

AH54

DMI_RXN_3

AL47

DMI_RXP_0

AG53

DMI_RXP_1

AK50

DMI_RXP_2

AH52

DMI_RXP_3

AL45

DMI_TXN_0

AG49

DMI_TXN_1

AJ49

DMI_TXN_2

AJ47

DMI_TXN_3

AG47

DMI_TXP_0

AF50

DMI_TXP_1

AH50

DMI_TXP_2

AJ45

DMI_TXP_3

AG45

ME_JTAG_TCK

AN45

ME_JTAG_TDO

AT44

ME_JTAG_TDI

AP44

ME_JTAG_TMS

AN47

PM_DPRSTP#

F6

SB_CK_1

BA23

SB_CK#_1

BB24

RSVD5

AN11

RSVD6

AM10

RSVD7

AK10

RSVD8

AL11

RSVD1

J43

RSVD2

L43

RSVD3

J41

RSVD4

L41

GFX_VID_0

G33

GFX_VID_1

G37

GFX_VID_2

F38

GFX_VID_3

F36

GFX_VR_EN

G39

SM_RCOMP_VOH

BK32

SM_RCOMP_VOL

BL31

THERMTRIP#

K28

DPRSLPVR

K36

RSVD9

F12

CL_CLK

AK52

CL_DATA

AK54

CL_PWROK

AW40

CL_RST#

AL53

CL_VREF

AL55

NC_1

A7

NC_2

A49

NC_3

A52

NC_4

A54

NC_5

B54

NC_6

D55

NC_7

G55

NC_8

BE55

NC_9

BH55

NC_10

BK55

NC_11

BK54

NC_12

BL54

NC_13

BL52

NC_14

BL49

NC_15

BL7

SDVO_CTRLCLK

B38

SDVO_CTRLDATA

A37

CLKREQ#

C31

RSVD14

C27

ICH_SYNC#

K42

PEG_CLK#

P50

PEG_CLK

R49

TSATN#

D10

NC_16

BL4

GFX_VID_4

G35

NC_17

BL2

NC_18

BK2

NC_19

BK1

NC_20

BH1

NC_21

BE1

NC_22

G1

DDPC_CTRLDATA

F32

DDPC_CTRLCLK

F34

HDA_BCLK

C29

HDA_RST#

B30

HDA_SDI

D28

HDA_SDO

A27

HDA_SYNC

B28

CFG_18

L33

CFG_19

K32

CFG_20

K34

SM_PWROK

AY37

SM_REXT

BH20

SM_DRAMRST#

BA37

RSVD15

D30

RSVD17

J9

RSVD20

AW42

RSVD22

BB20

RSVD23

BE19

RSVD24

BF20

RSVD25

BF18

R93 1.02K/F_4R93 1.02K/F_4

R100 10K_4R100 10K_4

C418

2.2u/6.3V_6

C418

2.2u/6.3V_6

R79 150/F_4R79 150/F_4

R80 30.1/F_4R80 30.1/F_4

R299 4.7K_4R299 4.7K_4R264 1K/F_4R264 1K/F_4

C421

2.2u/6.3V_6

C421

2.2u/6.3V_6

LVDS

PCI-EXPRESS GRAPHICS

TV

VGA

U18C

CANTIGASFF_1p0

LVDS

PCI-EXPRESS GRAPHICS

TV

VGA

U18C

CANTIGASFF_1p0

PEG_COMPI

U45

PEG_COMPO

T44

PEG_RX#_0

D52

PEG_RX#_1

G49

PEG_RX#_2

K54

PEG_RX#_3

H50

PEG_RX#_4

M52

PEG_RX#_5

N49

PEG_RX#_6

P54

PEG_RX#_7

V46

PEG_RX#_8

Y50

PEG_RX#_9

V52

PEG_RX#_10

W49

PEG_RX#_11

AB54

PEG_RX#_12

AD46

PEG_RX#_13

AC55

PEG_RX#_14

AE49

PEG_RX#_15

AF54

PEG_RX_0

E51

PEG_RX_1

F48

PEG_RX_2

J55

PEG_RX_3

J49

PEG_RX_4

M54

PEG_RX_5

M50

PEG_RX_6

P52

PEG_RX_7

U47

PEG_RX_8

AA49

PEG_RX_9

V54

PEG_RX_10

V50

PEG_RX_11

AB52

PEG_RX_12

AC47

PEG_RX_13

AC53

PEG_RX_14

AD50

PEG_RX_15

AF52

PEG_TX#_0

L47

PEG_TX#_10

AB46

PEG_TX#_3

H54

PEG_TX#_4

L55

PEG_TX#_5

T46

PEG_TX#_7

U49

PEG_TX#_8

T54

PEG_TX#_9

Y46

PEG_TX#_1

F52

PEG_TX#_11

W53

PEG_TX#_12

Y54

PEG_TX#_13

AC49

PEG_TX#_14

AF46

PEG_TX#_15

AD54

PEG_TX#_2

P46

PEG_TX_0

J47

PEG_TX_1

F54

PEG_TX_2

N47

PEG_TX_3

H52

PEG_TX_4

L53

PEG_TX_5

R47

PEG_TX_6

R55

PEG_TX_7

T50

PEG_TX_8

T52

PEG_TX_9

W47

PEG_TX_10

AA47

PEG_TX_11

W55

PEG_TX_12

Y52

PEG_TX_13

AB50

PEG_TX_14

AE47

PEG_TX_15

AD52

L_CTRL_CLK

K38

L_CTRL_DATA

L37

L_DDC_CLK

J37

L_DDC_DATA

L35

L_VDD_EN

B36

LVDS_IBG

F50

LVDS_VBG

H46

LVDS_VREFH

P44

LVDS_VREFL

K46

LVDSA_CLK#

D46

LVDSA_CLK

B46

LVDSA_DATA#_0

G45

LVDSA_DATA#_1

F46

LVDSA_DATA#_2

G41

LVDSA_DATA_1

G47

LVDSA_DATA_2

F40

LVDSB_CLK#

D44

LVDSB_CLK

B44

LVDSB_DATA#_0

B40

LVDSB_DATA#_1

A41

LVDSB_DATA#_2

F42

LVDSB_DATA_1

C41

LVDSB_DATA_2

G43

L_BKLT_EN

C37

TVA_DAC

J27

TVB_DAC

E27

TVC_DAC

G27

TVA_RTN

F26

CRT_BLUE

J29

CRT_DDC_CLK

D36

CRT_DDC_DATA

C35

CRT_GREEN

G29

CRT_HSYNC

J33

CRT_TVO_IREF

D32

CRT_RED

F30

CRT_IRTN

E29

CRT_VSYNC

G31

LVDSA_DATA_0

F44

LVDSB_DATA_0

D40

L_BKLT_CTRL

D38

TV_DCONSEL_0

B34

TV_DCONSEL_1

D34

PEG_TX#_6

R53

LVDSA_DATA#_3

C45

LVDSA_DATA_3

A45

LVDSB_DATA#_3

D48

LVDSB_DATA_3

B48

R78 150/F_4R78 150/F_4

R98 *0_4R98 *0_4

R270 80.6/F_4R270 80.6/F_4

T15T15

T17T17

R82 150/F_4R82 150/F_4

R112

1K/F_4

R112

1K/F_4

C75 0.1u/10V_4C75 0.1u/10V_4

C423

0.01u/25V_4

C423

0.01u/25V_4

R271 499/F_4R271 499/F_4

T8T8

R294 2.2K_4R294 2.2K_4

R349 *10K/F_4R349 *10K/F_4

C71 0.1u/10V_4C71 0.1u/10V_4