DS110DF410

www.ti.com.cn

ZHCSDP9D –OCTOBER 2011–REVISED APRIL 2015

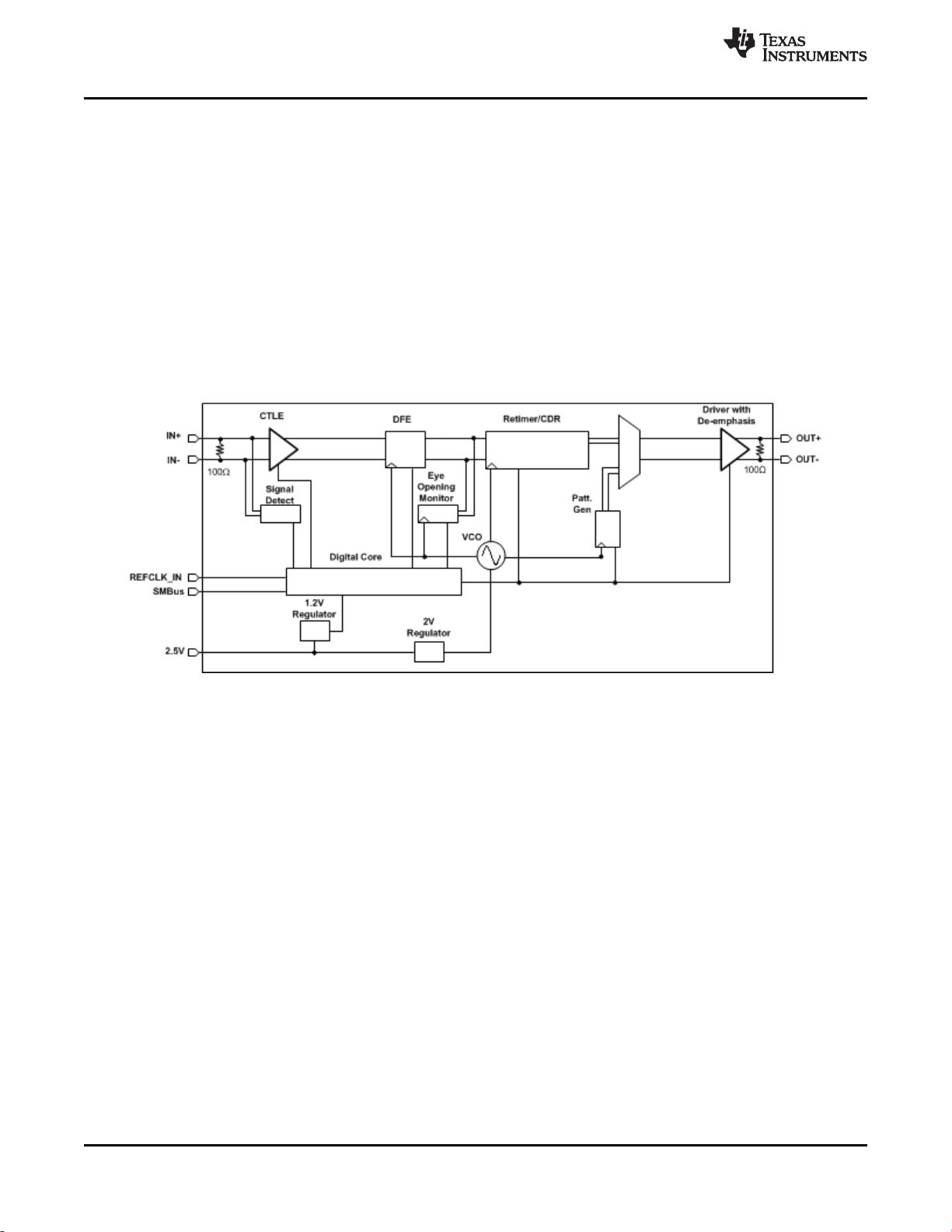

Feature Description (continued)

Once the CDR has locked and the CTLE has been adapted, the CTLE boost level will be frozen until a manual

re-adapt command is issued or until the CDR re-enters the lock acquisition state. The CTLE is typically

readapted by resetting the CDR.

The CTLE consists of 4 stages, with each stage having 2-bit boost control. This allows for 256 different stage-

boost combinations. The CTLE adaption algorithm allows the CTLE to adapt through 32 of these stage-boost

combinations. These 32 stage-boost combinations comprise the EQ Table in the channel registers; see channel

registers 0x40 through 0x5F. This EQ Table can be reprogrammed to support up to 32 of the 256 stage-boost

settings.

CTLE boost levels are determined by summing the boosts levels of the 4 stages. Different stage-boost

combinations that sum to the same number will have approximately the same boost level, but will result in a

different shape for the EQ transfer function (boost curve).

The fourth stage in the CTLE can be programmed through the SMBus interface to become a limiting stage rather

than a linear stage. This is useful in some applications, but it should not be typically used in combination with the

DFE.

8.3.4 DFE

A 5-tap DFE can be enabled within the data path of each channel to assist with reducing the effects of cross talk,

reflections, or post cursor inter-symbol interference (ISI). The DFE must be manually enabled, regardless of the

selected adapt mode. The DFE can be manually configured to specified tap polarities and tap weights.

The DFE taps are all feedback taps with 1UI spacing. Each tap has a specified boost weight range and polarity

bit.

8.3.5 Clock and Data Recovery

The DS110DF410 performs its clock and data recovery function by detecting the bit transitions in the incoming

data stream and locking its internal VCO to the clock represented by the mean arrival times of these bit

transitions. This process produces a recovered clock with greatly reduced jitter at jitter frequencies outside the

bandwidth of the CDR Phase-Locked Loop (PLL). This is the primary benefit of using the DS110DF410 in a

system. It significantly reduces the jitter present in the data stream, in effect resetting the jitter budget for the

system.

The DS110DF410 uses the 25 MHz reference to determine the coarse tuning setting for its internal VCO. On

power-up, on CDR reset, and when the DS110DF410 loses lock and cannot re-acquire lock after four attempts,

the 25 MHz reference is used to calibrate the VCO frequency. The required VCO frequency is set by using the

rate/subrate settings (see Table 2) or by manually setting the PPM count and divide ratio. To calibrate the VCO

frequency, the DS110DF410 searches through the available VCO coarse tuning settings and counts the divided

VCO frequency using the 25 MHz reference as a clock source. The VCO coarse tuning setting which provides

the VCO frequency closest to the required frequency is stored, and this coarse tuning setting is used for

subsequent operation. This produces a fast, robust phase lock to the input signal.

8.3.6 Output Driver

The output driver is capable of driving variable output voltages with variable amounts of analog de-emphasis.

The output voltage and de-emphasis level can be configured by writing registers over the SMBus. The

DS110DF410 cannot determine independently the appropriate output voltage or de-emphasis setting, so the user

is responsible for configuring these parameters. They can be set for each channel independently.

An idealized transmit waveform with analog de-emphasis applied is shown in Figure 4.

Copyright © 2011–2015, Texas Instruments Incorporated 13