DS110DF111

www.ti.com.cn

ZHCSDW7A –MAY 2013–REVISED JUNE 2015

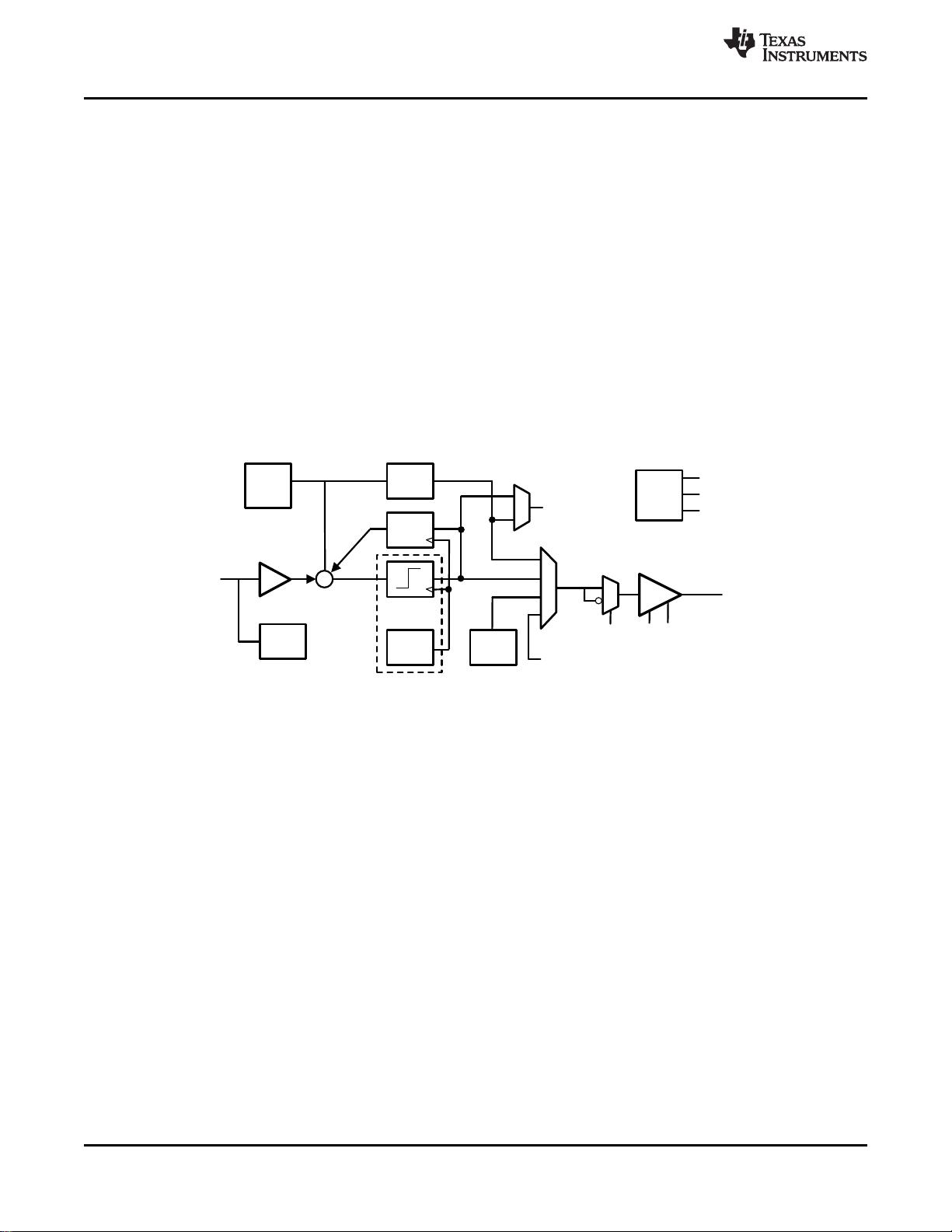

Feature Description (continued)

To make configuration of these settings easier, the DS110DF111 is designed to determine the correct settings

for the CTLE autonomously by automatically adapting these equalizations to the input transmission medium. The

automatic adaptation takes place when a signal is first detected at the input to the DS110DF111, immediately

after the DS110DF111 acquires phase lock.

The automatic adaptation is also triggered whenever the CDR circuitry is reset. The DS110DF111 uses its

internal eye monitor to generate a figure of merit for the adaptation. The DS110DF111 adjusts its CTLE boost

settings in a systematic way to optimize this figure of merit. When 8b/10b encoding is used and the input

channels has more than 15 dB of loss, the CTLE table and or adaption algorithm needs to be modified so as to

prevent CTLE mal-adaption. This scenario occurs when the CTLE boost is insufficient at lower settings to cause

regeneration of the high-frequency content of the K28.5 pattern. As boost is increased, the adaption Figure of

Merit (FOM) temporarily observes eye closure as the EQ boost begins to restore the high-frequency content. If

the FOM does not improve within the look-beyond counter depth, the CTLE will settle at a lower boost, which is

insufficient to equalize the signal and provide good BER.

The 5-tap DFE discriminates against input noise and random jitter as well as against crosstalk at the input to the

DS110DF111. The DFE tap weights and polarities are adaptive and operate in conjunction with the CTLE to

achieve an acceptable BER with more severe channel impairments.

7.3.1.2 Clock And Data Recovery

The DS110DF111 performs its clock and data recovery function by detecting the bit transitions in the incoming

data stream and locking its internal VCO to the clock represented by the mean arrival times of these bit

transitions. This process produces a recovered clock with greatly reduced jitter at jitter frequencies outside the

bandwidth of the CDR Phase-Locked Loop (PLL). This is the primary benefit of using the DS110DF111 in a

system. It significantly reduces the jitter present in the data stream, in effect resetting the jitter budget for the

system.

7.3.1.3 PRBS Pattern Generator

Each channel in the DS110DF111 can be configured to generate and output its own pseudo random bit

sequence (PRBS). The DS110DF111 pattern generators support the following PRBS sequences:

• PRBS-9, 2

9

- 1

• PRBS-31, 2

31

- 1

7.3.1.4 Datapath Multiplexer and Output Driver

The DS110DF111 datapath multiplexer is used to control which internal signal will be presented to the output

driver block. Inputs to this multiplexer include raw equalized data without clock recovery, retimed data, PRBS

patterns, and Loopback data from the other datapath.

The DS110DF111 output driver is used to control specific signal characteristics to enhance transmission quality.

The output driver is used to control the following signal features

• Amplitude

• De-Emphasis

• Edge Rate

• Polarity

The DS110DF111 is commonly used in applications where lossy transmission media exist both at the input and

the output of the DS110DF111. The CTLE compensates for lossy transmission media at the input to the

DS110DF111. The output de-emphasis compensates for the lossy transmission medium at the output of the

DS110DF111.

When there is a transition in the output data stream, the output differential voltage reaches its configured

maximum value within the configured rise/fall time of the output driver. Following this, the differential voltage

rapidly falls off until it reaches the configured VOD level minus the configured de-emphasis level. This

accentuates the high-frequency components of the output driver signal at the expense of the low frequency

components. The pre-distorted DS110DF111 output signal, with high-frequency components emphasized relative

to its low frequency components, exhibits less inter-symbol interference after traveling down a dispersive

transmission medium than an undistorted output signal.

Copyright © 2013–2015, Texas Instruments Incorporated 11