20 EZ-USB® Technical Reference Manual, Document # 001-13670 Rev. *D

Introducing EZ-USB®

1.12 EZ-USB Feature Summary

The EZ-USB chips include the following features:

■ Low power consumption enabling bus-powered designs

■ For EZ-USB FX2LP, an on-chip 480 Mbps transceiver.

For EZ-USB FX1, an on-chip 12 Mbps transceiver. Both

devices contain a PLL and SIE—the entire USB physical

layer (PHY).

■ Double-, triple- and quad-buffered endpoint FIFOs

accommodate the 480 Mbps USB data rate

■ Built in, enhanced 8051 running at up to 48 MHz

❐ Fully featured: 256 bytes of register RAM, two

USARTs, three timers, two data pointers

❐ Fast: four clocks (83.3 ns at 48 MHz) per instruction

cycle

❐ SFR access to control registers (including I/O ports)

that require high speed

❐ USB-vectored interrupts for low ISR latency

❐ Used for USB housekeeping and control, not to

move high-speed data

■ ‘Soft’ operation—USB firmware can be downloaded over

USB, eliminating the need for hard coded memory

■ Four interface FIFOs that can be internally or externally

clocked. The endpoint and interface FIFOs are unified to

eliminate data transfer time between USB and external

logic.

■ General Programmable Interface (GPIF), a microcoded

state machine which serves as a timing master for a

glueless interface to the EZ-USB FIFOs

■ ECC Generation based on the SmartMedia™ standard

The EZ-USB family offers single-chip USB 2.0 peripheral

solutions. Unlike designs that use an external PHY, the EZ-

USB integrates everything on one chip, eliminating costly

high pin-count packages and the need to route high speed

signals between chips.

1.13 EZ-USB Integrated

Microprocessor

The EZ-USB’s CPU uses on-chip RAM as program and data

memory. The Memory chapter on page 71, describes the

various internal/external memory options.

The CPU communicates with the SIE using a set of registers

occupying on-chip RAM addresses 0xE500-0xE6FF. These

registers are grouped and described by function in individual

chapters of this reference manual and summarized in regis-

ter order. See chapter “Registers” on page 211.

The CPU has two duties. First, it participates in the protocol

defined in the Universal Serial Bus Specification Version

2.0, Chapter 9, USB Device Framework. Thanks to the EZ-

USB’s ‘smart’ SIE, the firmware associated with the USB

protocol is simplified, leaving code space and bandwidth

available for the CPU’s primary duty—to help implement

your device. On the device side, abundant input/output

resources are available, including I/O ports, USARTs, and

an I2C bus master controller. These resources are

described in the Input/Output chapter on page 181, and the

Timers/Counters and Serial Interface chapter on page 193.

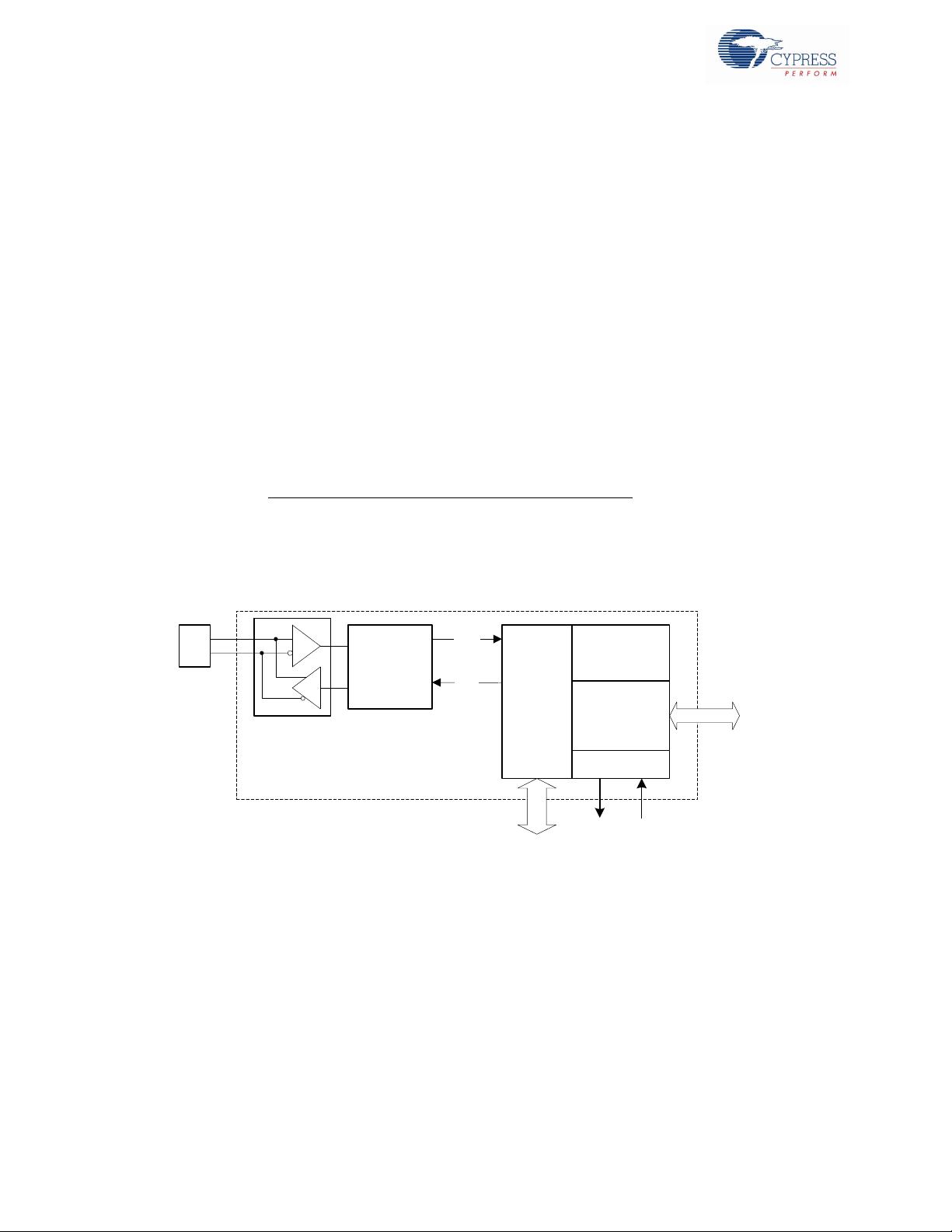

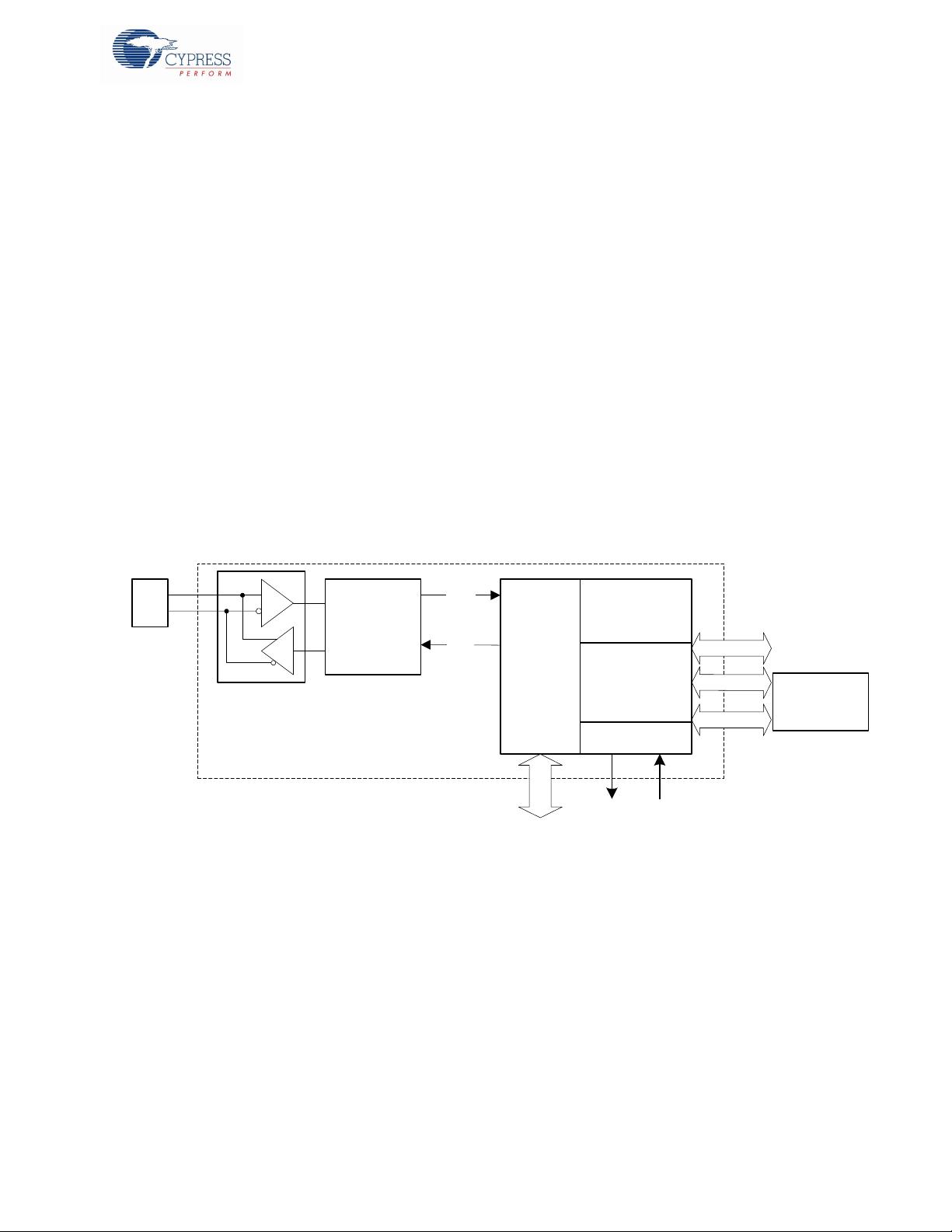

It is important to recognize that the EZ-USB architecture is

such that the CPU sets up and controls data transfers, but it

normally does not participate in high bandwidth transfers. It

is not in the data path; instead, the large data FIFOs that

handle endpoint data connect directly to outside interfaces.

To make the interface versatile, a programmable timing gen-

erator (GPIF, General Programmable Interface) can create

user-programmed waveforms for high bandwidth transfers

between the internal FIFOs and external logic.

The EZ-USB chips add eight interrupt sources to the stan-

dard 8051 interrupt system:

■ INT2: USB Interrupt

■ INT3: I2C Bus Interrupt

■ INT4: FIFO/GPIF Interrupt

■ INT4: External Interrupt 4

■ INT5: External Interrupt 5

■ INT6: External Interrupt 6

■ USART1: USART1 Interrupt

■ WAKEUP: USB Resume Interrupt

The EZ-USB chips provide 27 individual USB-interrupt

sources which share the INT2 interrupt, and 14 individual

FIFO/GPIF-interrupt sources which share the INT4 interrupt.

To save the code and processing time which normally would

be required to identify an individual interrupt source, the EZ-

USB provides a second level of interrupt vectoring called

Autovectoring. Each INT2 and INT4 interrupt source has its

own autovector, so when an interrupt requires service, the

proper ISR (interrupt service routine) is automatically

invoked. The Interrupts chapter on page 59 describes the

EZ-USB interrupt system.