S6D0137: 20050113版132RGB源极驱动器与内部GRAM技术

需积分: 9 57 浏览量

更新于2024-07-15

收藏 712KB PDF 举报

"S6D0137_V0.5_20050113.pdf 是三星半导体系统LSI部门发布的一款针对65,536/262,144颜色TFT-LCD的模拟源极驱动器S6D0137的初步数据手册,版本为0.5,日期为2005年1月13日。该芯片集成了132路RGB信号源和162路栅极驱动,同时具备内部GRAM功能。文档主要涵盖了电源电路、电压设置模式图、伽玛校正功能、灰度放大器结构、伽玛调整寄存器、高低电平调整寄存器、电阻网络以及振荡电路等关键内容。此外,还列出了直流特性、功耗信息以及修订历史。"

文档详细内容分析:

1. **电源电路 (Power Supply Circuit)**: 这部分详细介绍了驱动器所需的电源配置,包括各个电源引脚的电压设定和电源稳定性对显示性能的影响。

2. **电压设置模式图 (Pattern Diagrams for Voltage Setting)**: 提供了设置不同电压的图案图,用于指导用户如何正确配置电压以达到理想的显示效果。

3. **伽玛校正功能 (Gamma Adjustment Function)**: 伽玛校正是提升液晶显示器色彩准确性的关键,这部分详细解释了如何通过S6D0137内置的灰度放大器来调整伽玛曲线,以优化颜色表现。

4. **灰度放大器结构 (Structure of Grayscale Amplifier)**: 描述了灰度放大器的内部结构,它负责将数字信号转换为模拟电压,进而控制液晶像素的亮度。

5. **伽玛调整寄存器 (Gamma Adjustment Register)**: 包括高电平、中电平和低电平调整寄存器,允许用户通过编程改变不同亮度级别的伽玛值,以适应不同的显示环境。

6. **电阻网络和64选1选择器 (Ladder Resistor Network / 64-to-1 Selector)**: 这些电路用于生成连续的灰度等级,64选1选择器根据寄存器设置选择合适的电阻值,形成不同的灰阶电压。

7. **可变电阻 (Variable Resistor)**: 可能用于微调伽玛曲线或适应电源波动。

8. **64选1选择器 (The 64-to-1 Selector)**: 详细介绍了这个电路的工作原理和作用。

9. **固定伽玛寄存器值 (Fixed Gamma Register Value)**: 提供了预设的伽玛值,可以直接应用以简化设置过程。

10. **振荡电路 (Oscillation Circuit)**: 负责生成系统所需的时钟信号,确保驱动器内部操作的同步。

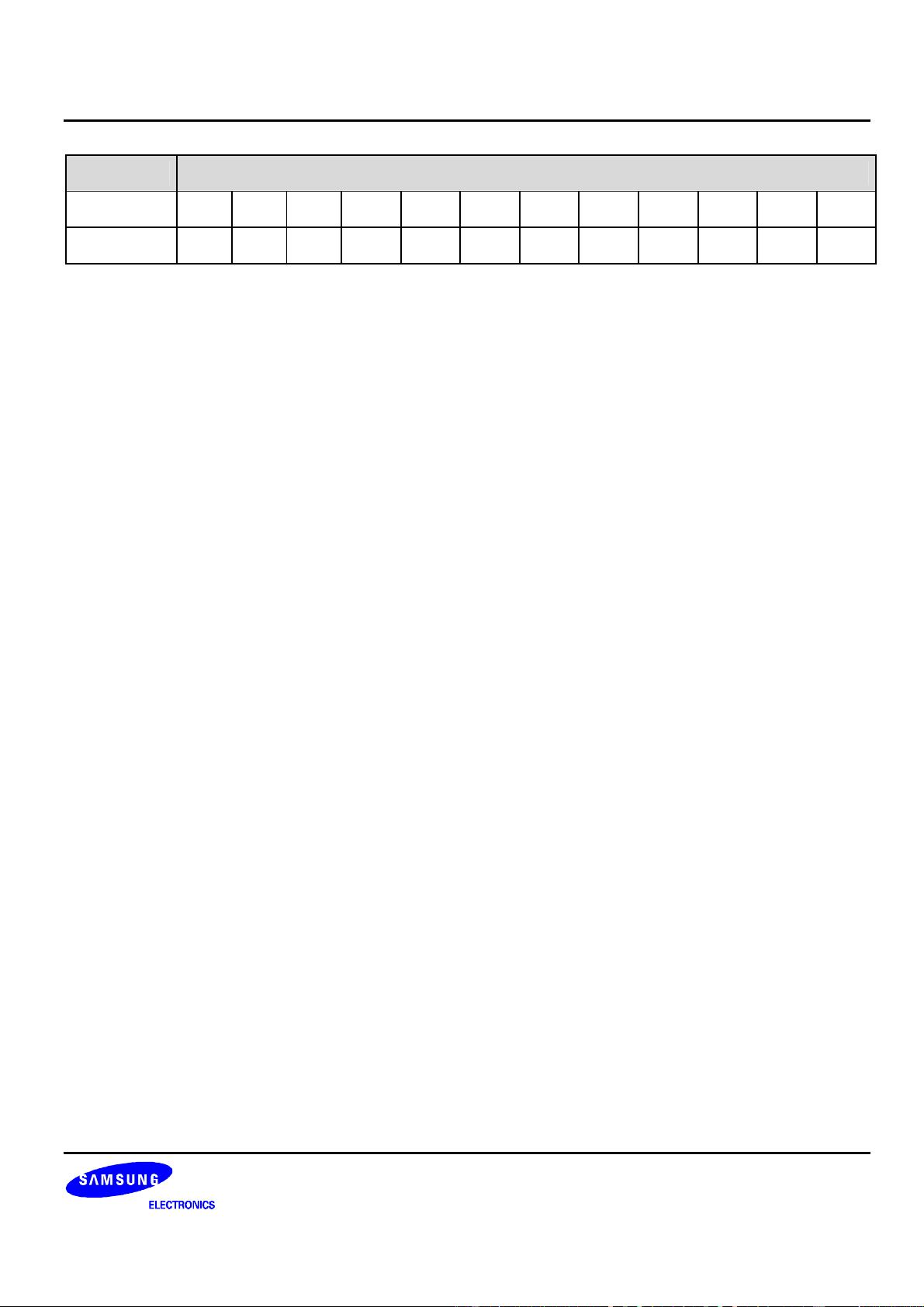

11. **直流特性 (DC Characteristics)**: 描述了芯片在直流工作状态下的电气特性,如输入输出电压范围、电流消耗等。

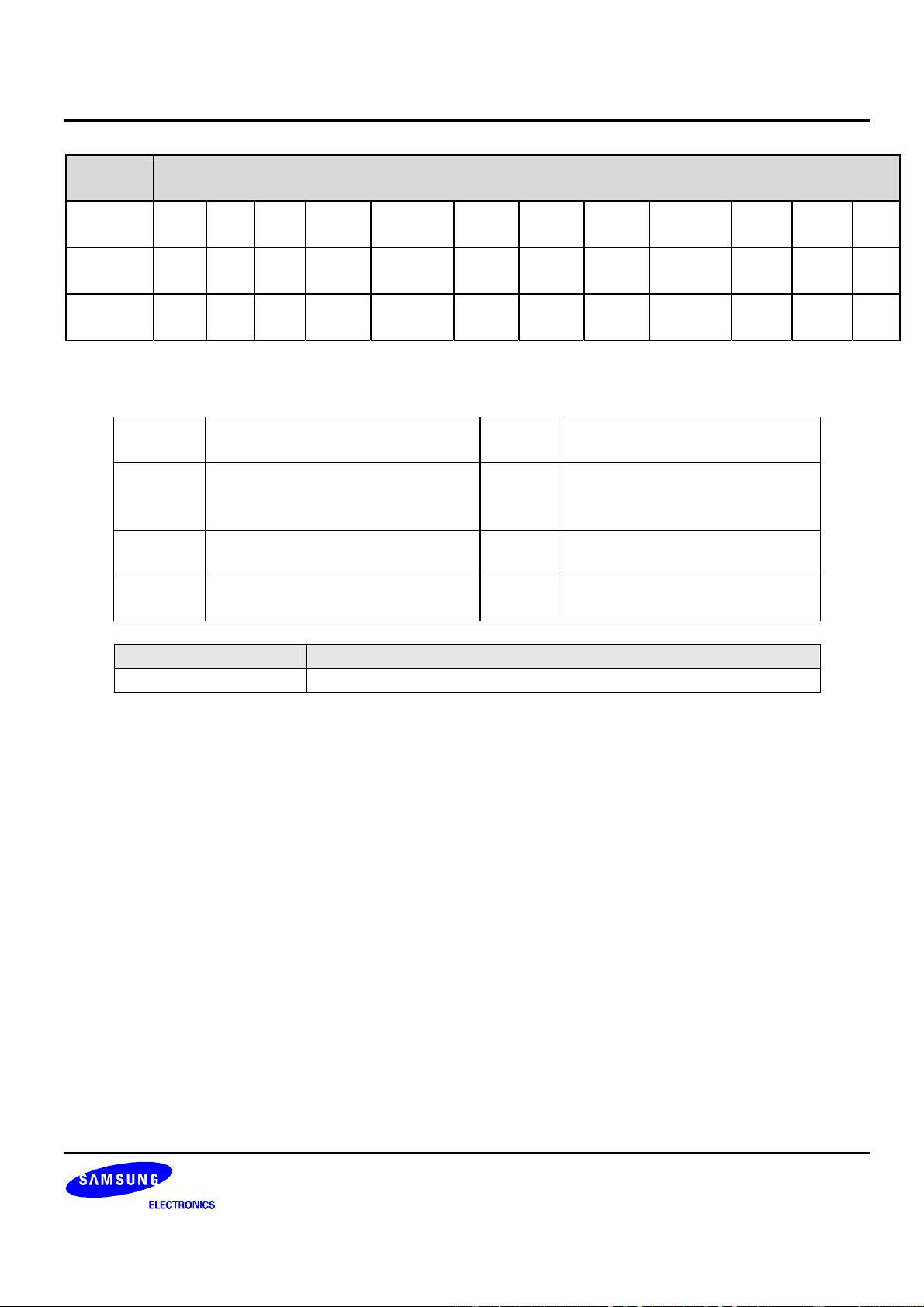

12. **功耗 (Power Consumption)**: 提供了芯片在运行时的平均功耗和峰值功耗信息。

13. **修订历史 (Revision History)**: 记录了文档的修改历程,有助于追踪和理解设计的演变。

14. **注意事项 (Notice)**: 可能包含版权信息、使用限制或其他重要的法律声明。

这个文档对于理解和使用S6D0137驱动器来说是至关重要的,尤其是对于那些需要精确控制TFT-LCD显示质量的工程师而言。

2021-02-28 上传

2021-02-28 上传

2023-05-25 上传

2023-05-25 上传

2023-05-31 上传

2023-06-09 上传

2023-10-10 上传

2023-06-08 上传

2023-05-25 上传

u010365054

- 粉丝: 5

- 资源: 1237

最新资源

- Lombok 快速入门与注解详解

- SpringSecurity实战:声明式安全控制框架解析

- XML基础教程:从数据传输到存储解析

- Matlab实现图像空间平移与镜像变换示例

- Python流程控制与运算符详解

- Python基础:类型转换与循环语句

- 辰科CD-6024-4控制器说明书:LED亮度调节与触发功能解析

- AE particular插件全面解析:英汉对照与关键参数

- Shell脚本实践:创建tar包、字符串累加与简易运算器

- TMS320F28335:浮点处理器与ADC详解

- 互联网基础与结构解析:从ARPANET到多层次ISP

- Redhat系统中构建与Windows共享的Samba服务器实战

- microPython编程指南:从入门到实践

- 数据结构实验:顺序构建并遍历链表

- NVIDIA TX2系统安装与恢复指南

- C语言实现贪吃蛇游戏基础代码