w w w . c h i n a f i x . c o m

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

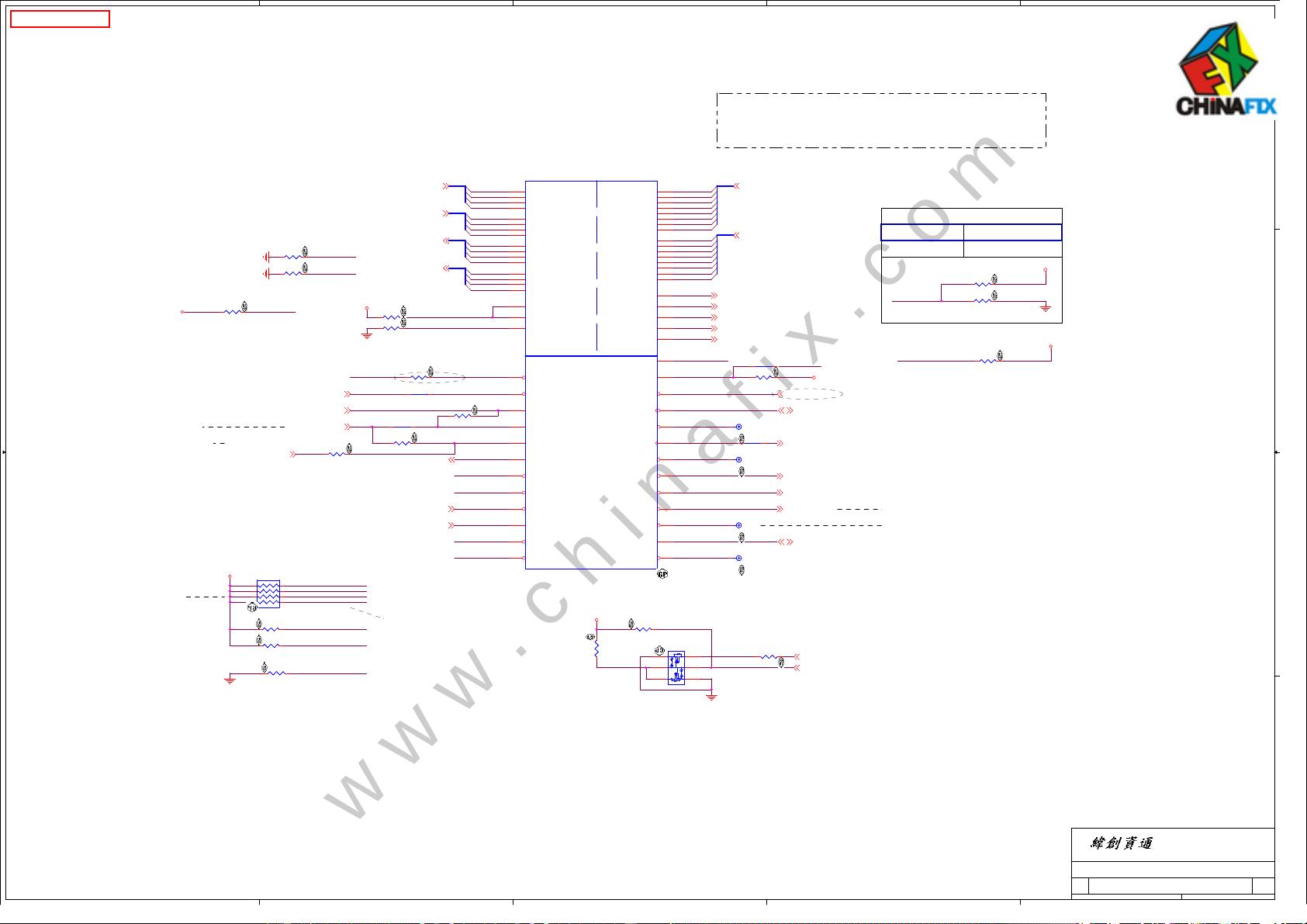

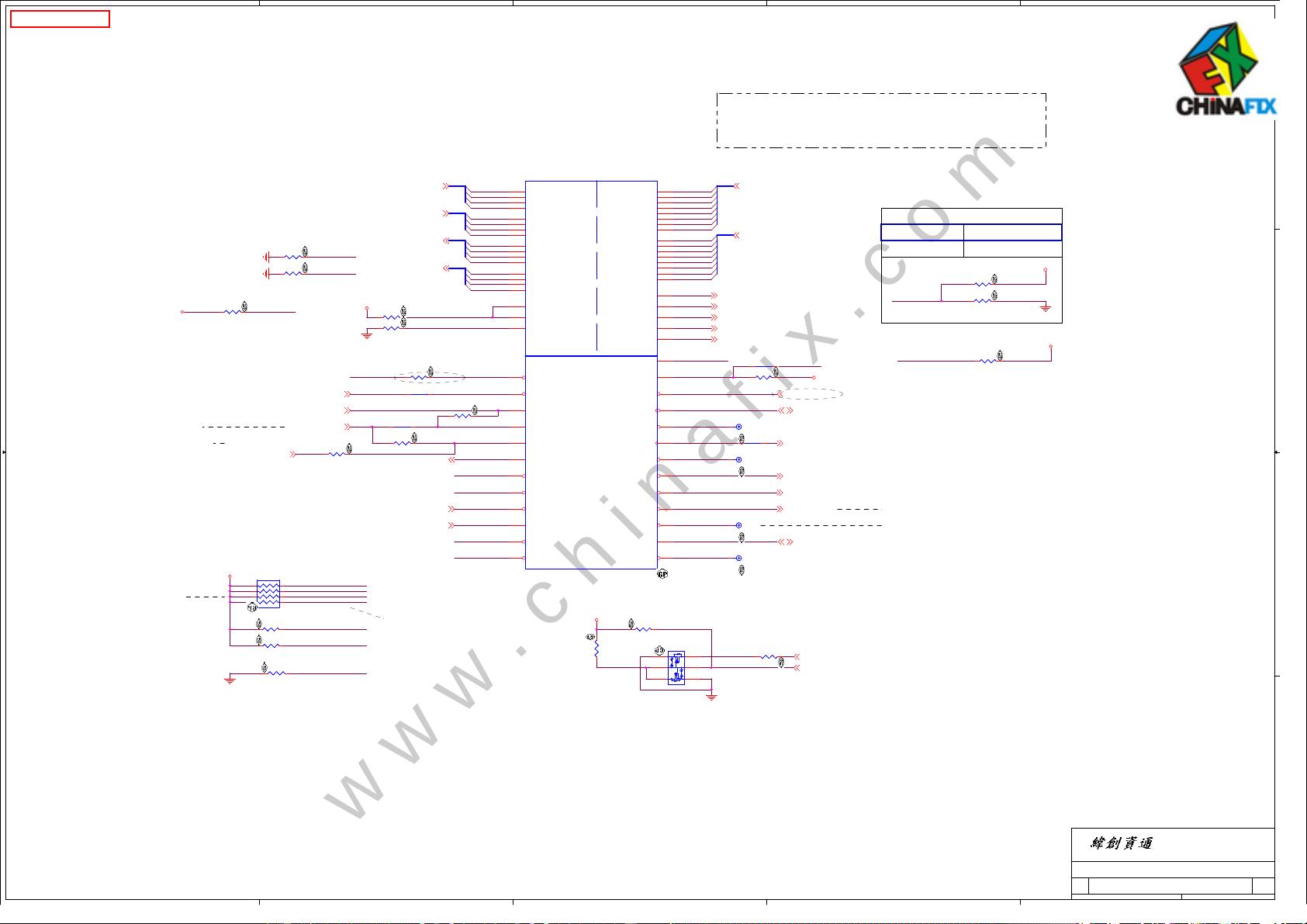

BATLOW#

PM_CLKRUN#

PM_PWRBTN#

SUS_PWR_ACK

DSW ODVREN

PM_SUS_STAT#

SUS_CLK

DSW ODVREN

PM_RSMRST#

PCH_DPW ROK

PM_RI#

PM_PWRBTN#

RBIAS_CPY

SUSACK#SUS_PWR_ACK

PWROK

DMI_COMP_R

PWROK

SYS_PWROK

MEPWROK

BATLOW#

PM_RI#

AC_PRESENT

PM_RSMRST#

PCIE_WAKE#

SYS_RESET#

PM_RSMRST#

3V_5V_POK_#

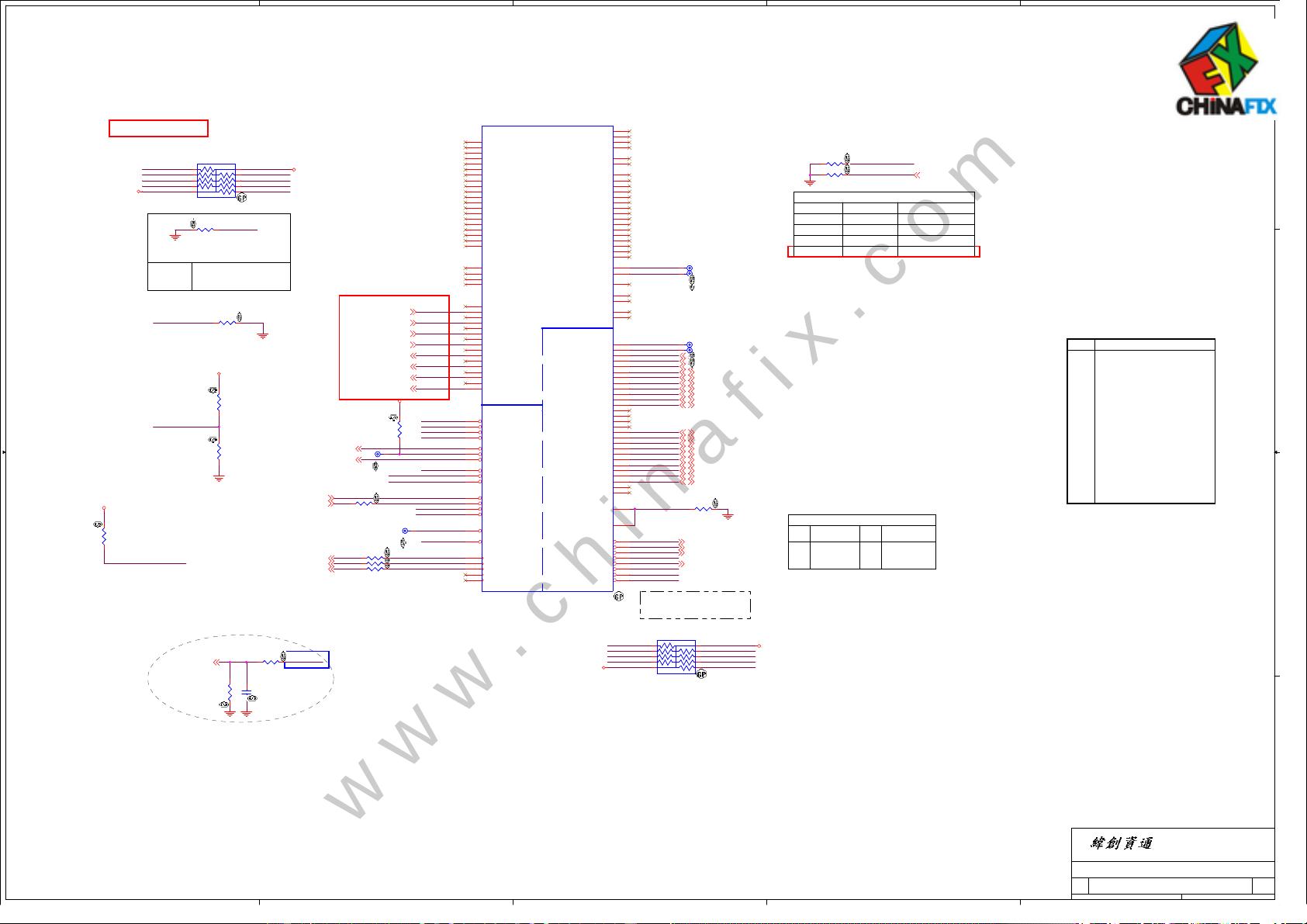

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXP1

DMI_RXP2

DMI_RXP0

DMI_TXN1

DMI_TXN0

DMI_TXN3

DMI_TXN2

DMI_TXP1

DMI_TXP0

DMI_TXP3

DMI_TXP2

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXP3

FDI_TXP0

FDI_TXP5

FDI_TXP4

FDI_TXP6

FDI_TXP1

FDI_TXP2

PM_RSMRST#

DMI_RXN3

DMI_RXP3

FDI_TXP7

FDI_TXN7

PM_SLP_LAN#

PM_SLP_SUS#

PM_SLP_S5#

SUS_PWR_ACK

SYS_RESET#

RTC_AUX_S5

3D3V_S5

3D3V_S0

RTC_AUX_S5

1D05V_VTT

3D3V_AUX_S5

3D3V_S0

H_PM_SYNC 5

PM_CLKRUN# 27

DMI_RXN[3:0]4

DMI_RXP[3:0]4

DMI_TXN[3:0]4

DMI_TXP[3:0]4

XDP_DBRESET#5

SYS_PWROK36

S0_PWR_GOOD27

PM_PWRBTN#27,97

AC_PRESENT27

PM_DRAM_PW RGD37

FDI_TXN[7:0] 4

FDI_TXP[7:0] 4

FDI_INT 4

FDI_FSYNC0 4

FDI_FSYNC1 4

FDI_LSYNC0 4

FDI_LSYNC1 4

PCH_SUSCLK_KBC 27

PM_SLP_S3# 27,36,37,47

PM_SLP_S4# 27,46,97

PCIE_WAKE# 31,65,66

RSMRST#_KBC 27

3V_5V_POK 41

PM_SLP_A# 27,45

MPWROK45

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

LA480

SD

PCH : DMI/FDI/PM

A2

19 103Friday, January 06, 2012

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

LA480

SD

PCH : DMI/FDI/PM

A2

19 103Friday, January 06, 2012

<Core Design>

Title

Size Document Number Rev

Date: Sheet of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

LA480

SD

PCH : DMI/FDI/PM

A2

19 103Friday, January 06, 2012

<Core Design>

Signal Routing Guideline:

DMI_ZCOMP keep W=4 mils and

routing length less than 500

mils.

DMI_IRCOMP keep W=4 mils and

routing length less than 500

mils.

PCH_WAKE#

CRB : 1K

CHKLIST: 10K

DSWODVREN - On Die DSW VR Enable

HIGH Enabled (DEFAULT)

LOW Disabled

SSID = PCH

For platforms not supporting Deep S4/S5

1.VccSUS3_3 and VccDSW3_3 will rise at the same time (connected on board)

2.DPWROK and RSMRST# will rise at the same time (connected on board)

3.SLP_SUS# and SUSACK# are left as ‘no connect’

4.SUSWARN# used as SUSPWRDNACK/GPIO30

S0_PWR_GOOD after PM_SLP_S3# delay 200 ms

Platforms supporting Deep S4/S5, but not wishing

to participate in the handshake during wake and Deep S4/S5

entry may tie SUSACK# to SUSWARN#.

For platforms supporting DEEP S4/S5 state, a low on this

signal indicates that PCH is in Deep Sleep state and that

EC/platform logic does not need to keep the Suspend Rails

ON.

If high means EC must keep SUS rails ON.

If DEEP S4/S5 is not supported, then this pin can be left

unconnected.

This signal is used to control power planes to the IntelR ME

sub-system. This signal will be asserted in M-off state. If M3

is not supported then SLP_A# will have the same timings as

SLP_S3#.

Active Sleep Well

(ASW) Power OK

PWROK: it indicates to PCH that

its CORE well power is stable.

SYS_PWROK: the system is ready to start the exit from

reset (de-asserts PLT_RST# to the processor)

SUS_ACK#: For non-DWS platforms, this signal can be left unconnected.

Due to the internal pull-up on this signal it will be pulled high

in order for the boot sequence to proceed.

SUSPWRDNACK : No longer requires a 10-K pull-up to VccSUS

(3.3 V).

1 2

R1930 0R2J-2-GP

Non-SBA

R1930 0R2J-2-GP

Non-SBA

1 2

R1905

10KR2J-3-GP

DY

R1905

10KR2J-3-GP

DY

1 2

R1923

0R2J-2-GP

DY

R1923

0R2J-2-GP

DY

12

R1909 10KR2J-3-GPR1909 10KR2J-3-GP

1

TP1905TP1905

1 2

R1921

1KR2J-1-GP

R1921

1KR2J-1-GP

12

R1922 10KR2J-3-GP

DY

R1922 10KR2J-3-GP

DY

12

R1925 100KR2J-1-GPR1925 100KR2J-1-GP

1

TP1901TP1901

1

2

3

45

6

7

8

RN1901

SRN10KJ-6-GP

RN1901

SRN10KJ-6-GP

12

R1908

10KR2J-3-GP

R1908

10KR2J-3-GP

1 2

R1901

49D9R2F-GP

R1901

49D9R2F-GP

1 2

R1911

10KR2J-3-GP

DY

R1911

10KR2J-3-GP

DY

1 2

R1918 330KR2J-L1-GP

DY

R1918 330KR2J-L1-GP

DY

1 2

R1904 100KR2J-1-GPR1904 100KR2J-1-GP

1 2

R1914 0R0402-PADR1914 0R0402-PAD

1 2

R1992 0R0402-PADR1992 0R0402-PAD

1 2

R1919 8K2R2J-3-GPR1919 8K2R2J-3-GP

1 2

R1916 0R0402-PADR1916 0R0402-PAD

1 2

R1931 0R2J-2-GP

SBA

R1931 0R2J-2-GP

SBA

1 2

R1926 10KR2J-3-GP

DY

R1926 10KR2J-3-GP

DY

1

TP1904TP1904

1

TP1902TP1902

1

2

34

5

6

Q1901

2N7002KDW-GP

84.2N702.A3F

2nd = 84.DM601.03F

Q1901

2N7002KDW-GP

84.2N702.A3F

2nd = 84.DM601.03F

1 2

R1917 330KR2J-L1-GPR1917 330KR2J-L1-GP

1 2

R1915 0R2J-2-GP

DY

R1915 0R2J-2-GP

DY

1 2

R1924

10KR2J-3-GP

R1924

10KR2J-3-GP

1 2

R1913

0R0402-PAD

R1913

0R0402-PAD

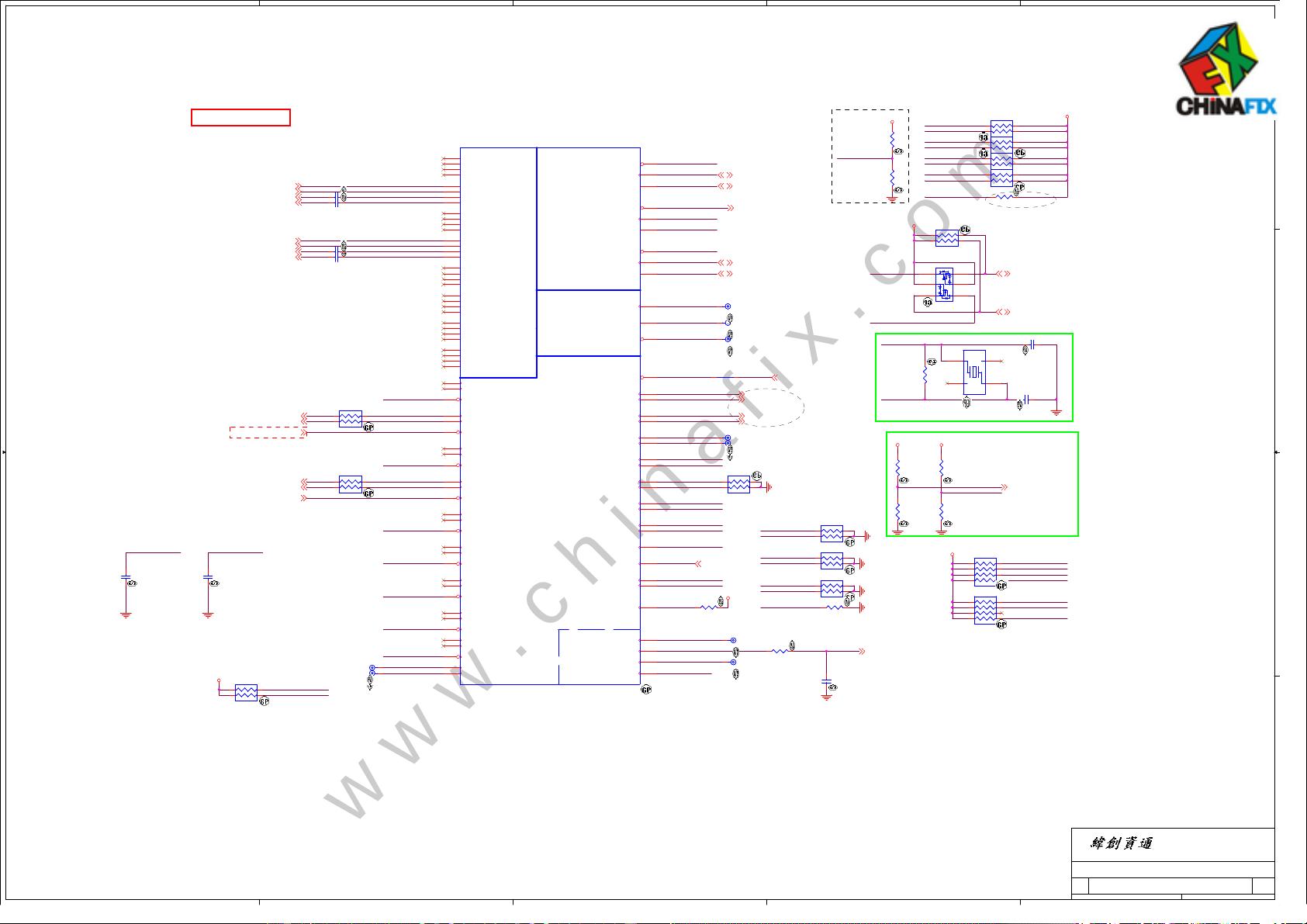

DMI0RXN

BC24

DMI1RXN

BE20

DMI2RXN

BG18

DMI3RXN

BG20

DMI0RXP

BE24

DMI1RXP

BC20

DMI2RXP

BJ18

DMI3RXP

BJ20

DMI0TXN

AW24

DMI1TXN

AW20

DMI2TXN

BB18

DMI3TXN

AV18

DMI0TXP

AY24

DMI1TXP

AY20

DMI2TXP

AY18

DMI3TXP

AU18

DMI_ZCOMP

BJ24

DMI_IRCOMP

BG25

FDI_RXN0

BJ14

FDI_RXN1

AY14

FDI_RXN2

BE14

FDI_RXN3

BH13

FDI_RXN4

BC12

FDI_RXN5

BJ12

FDI_RXN6

BG10

FDI_RXN7

BG9

FDI_RXP0

BG14

FDI_RXP1

BB14

FDI_RXP2

BF14

FDI_RXP3

BG13

FDI_RXP4

BE12

FDI_RXP5

BG12

FDI_RXP6

BJ10

FDI_RXP7

BH9

FDI_FSYNC0

AV12

FDI_FSYNC1

BC10

FDI_LSYNC0

AV14

FDI_LSYNC1

BB10

FDI_INT

AW16

PMSYNCH

AP14

SLP_SUS#

G16

SLP_S3#

F4

SLP_S4#

H4

SLP_S5#/GPIO63

D10

SYS_RESET#

K3

SYS_PWROK

P12

PWRBTN#

E20

RI#

A10

WAKE#

B9

SUS_STAT#/GPIO61

G8

SUSCLK/GPIO62

N14

ACPRESENT/GPIO31

H20

BATLOW#/GPIO72

E10

PWROK

L22

CLKRUN#/GPIO32

N3

SUSWARN#/SUSPWRDNACK/GPIO30

K16

RSMRST#

C21

DRAMPWROK

B13

SLP_LAN#/GPIO29

K14

APWROK

L10

DPWROK

E22

DMI2RBIAS

BH21

SLP_A#

G10

DSWVRMEN

A18

SUSACK#

C12

DMI

FDI

System Power Management

3 OF 10

PCH1C

PANTHER-GP-NF

DMI

FDI

System Power Management

3 OF 10

PCH1C

PANTHER-GP-NF

1 2

R1902

750R2F-GP

R1902

750R2F-GP

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功