清华大学微电子所:时序参数详解——Latch与Register

需积分: 9 42 浏览量

更新于2024-07-16

收藏 327KB PDF 举报

本资源是一份关于"时序参数review"的学术论文,由清华大学微电子所的周润德教授在2004年12月15日编写的,主要针对数字大规模集成电路中的时序设计进行深入讲解。论文详细讨论了时序参数对于Register(寄存器)和Latch(触发器)这两种基本电路的重要作用。

首先, Register部分强调了数据的上升时间和下降时间对延时的影响,区分了tc-q(数据到Q端的延迟)、thold(建立时间)和T(总的时钟周期)。当上升时间和下降时间不同时,电路的响应时间会有所不同。此外,还介绍了Latch的时序参数,如tsu(上电时间)和td-q(Q端到D端的延迟),以及它们与datatoclock(数据到时钟)时间的关系。

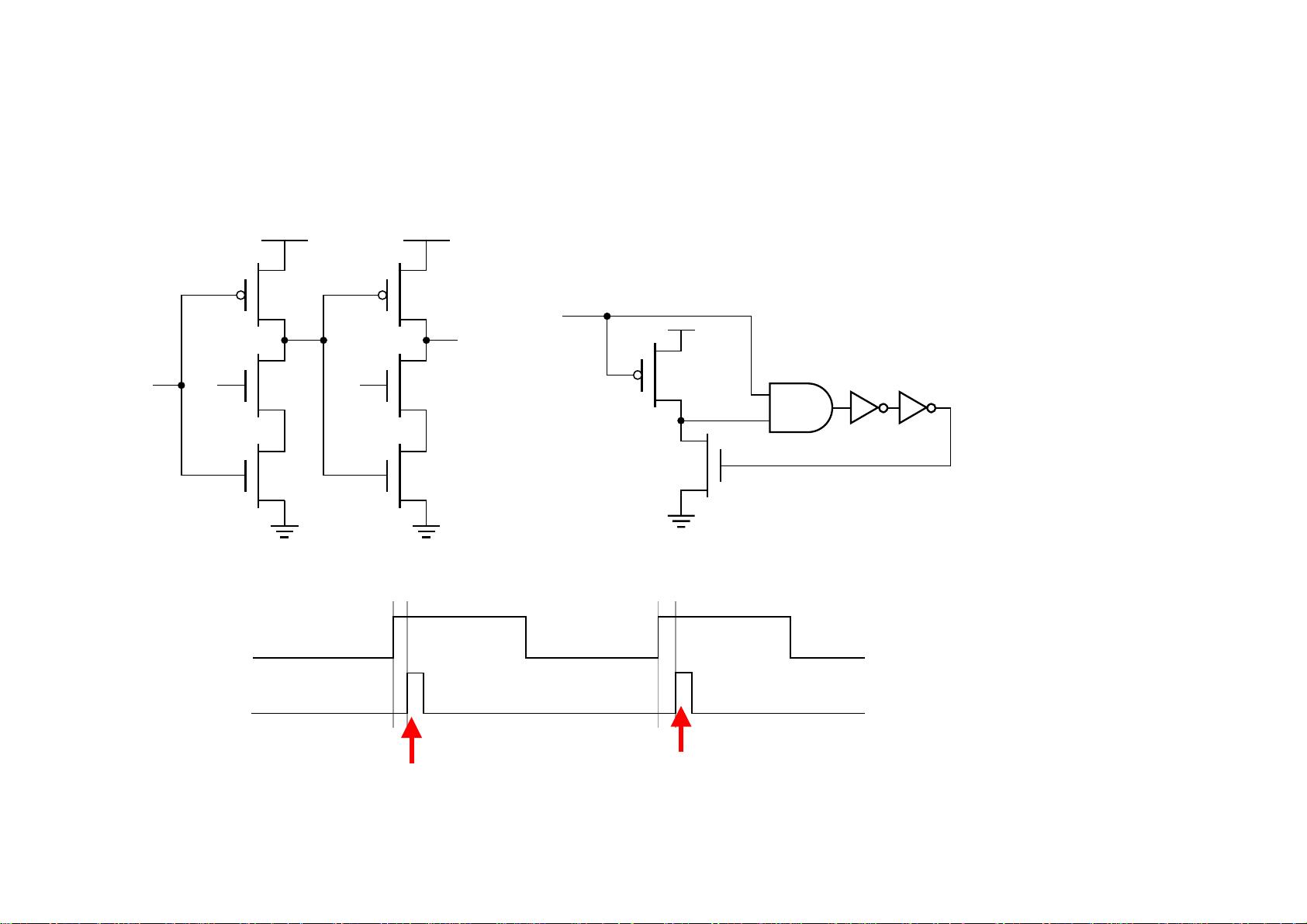

接着,论文探讨了Latch和Register的Latency(tDQ)时序,包括正电平触发 latch和register的响应模式,以及何时正沿触发优于负沿触发。具体关系表明,对于不同的数据到达窗口W,latency的时间差异取决于数据和时钟之间的关系。

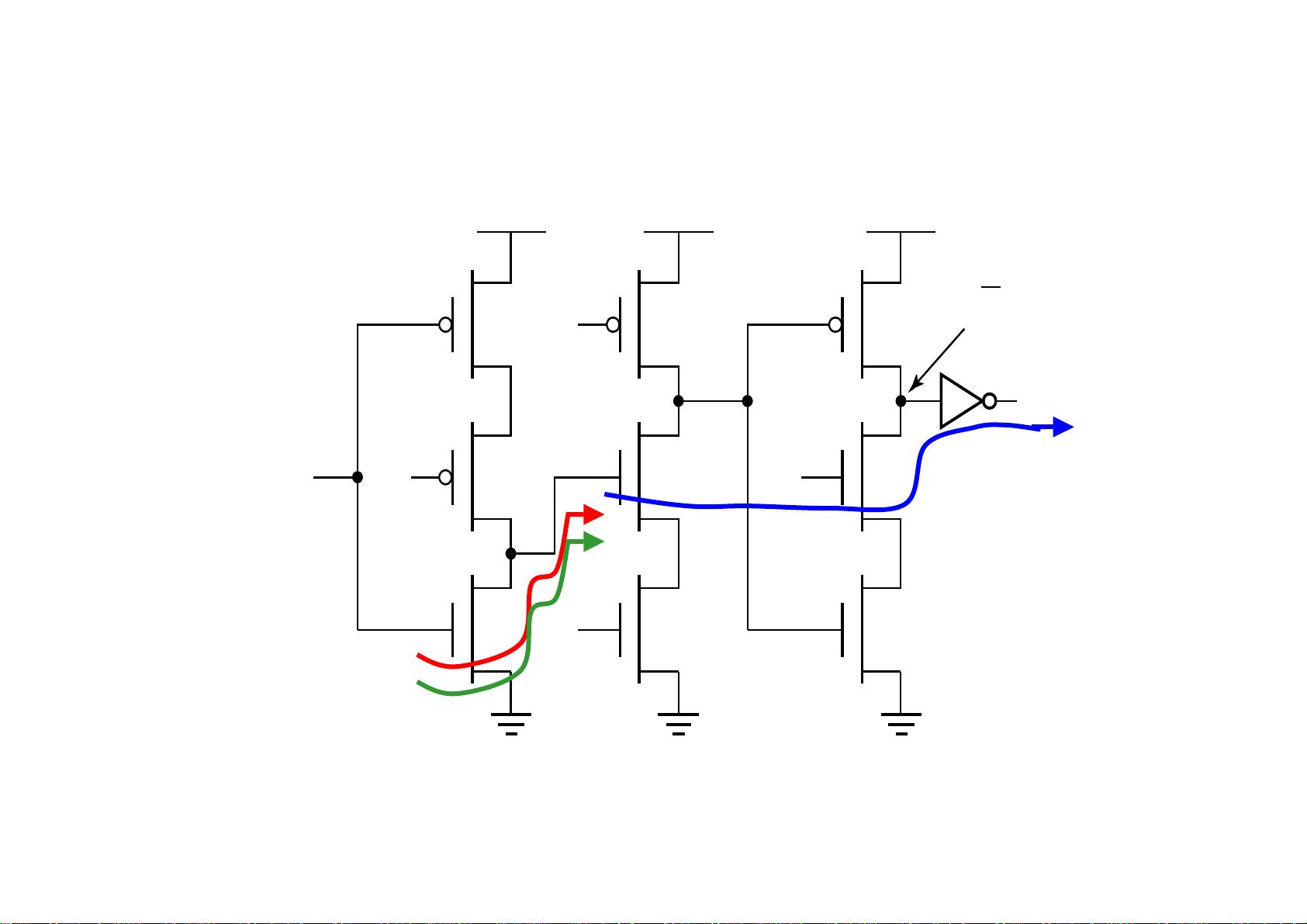

文章进一步解析了Clk-QDelay(时钟到Q延迟)、TSetup-1(第一级设置时间)和THold-1(第一级保持时间)的概念,这些是确保电路稳定工作的重要时序条件。通过示例,如图6和图7所示的电路状态和时间线,解释了如何确定这些时序参数。

最后,资源还涉及到了传输门Latch的时序参数设定,特别是Clk-to-Q延迟、Setup时间和Hold时间的计算,以及Master-Slave(主从)传输门结构的应用,这对于理解和设计高性能数字电路具有实际指导意义。

整体来看,这份论文为理解并优化数字集成电路中的时序设计提供了关键的知识框架和技术细节,对于从事该领域的工程师来说是一份宝贵的参考资料。

2022-07-09 上传

点击了解资源详情

2023-08-14 上传

2023-06-20 上传

2024-01-24 上传

2023-09-29 上传

2023-06-06 上传

2023-07-14 上传

壹零捌

- 粉丝: 222

- 资源: 101

最新资源

- AirKiss技术详解:无线传递信息与智能家居连接

- Hibernate主键生成策略详解

- 操作系统实验:位示图法管理磁盘空闲空间

- JSON详解:数据交换的主流格式

- Win7安装Ubuntu双系统详细指南

- FPGA内部结构与工作原理探索

- 信用评分模型解析:WOE、IV与ROC

- 使用LVS+Keepalived构建高可用负载均衡集群

- 微信小程序驱动餐饮与服装业创新转型:便捷管理与低成本优势

- 机器学习入门指南:从基础到进阶

- 解决Win7 IIS配置错误500.22与0x80070032

- SQL-DFS:优化HDFS小文件存储的解决方案

- Hadoop、Hbase、Spark环境部署与主机配置详解

- Kisso:加密会话Cookie实现的单点登录SSO

- OpenCV读取与拼接多幅图像教程

- QT实战:轻松生成与解析JSON数据