Spartan-6 FPGA时钟资源用户指南

142 浏览量

更新于2024-06-19

收藏 3.97MB PDF 举报

"Spartan-6 FPGA Clocking Resources User Guide.pdf"

这篇用户指南详细介绍了Xilinx Spartan-6 FPGA的时钟资源及其使用方法。Spartan-6 FPGA是Xilinx公司的一款流行的现场可编程门阵列(FPGA)系列,其在电子设计自动化领域广泛应用于各种系统设计。时钟管理是FPGA设计的关键部分,因为它直接影响到系统的性能、功耗和稳定性。

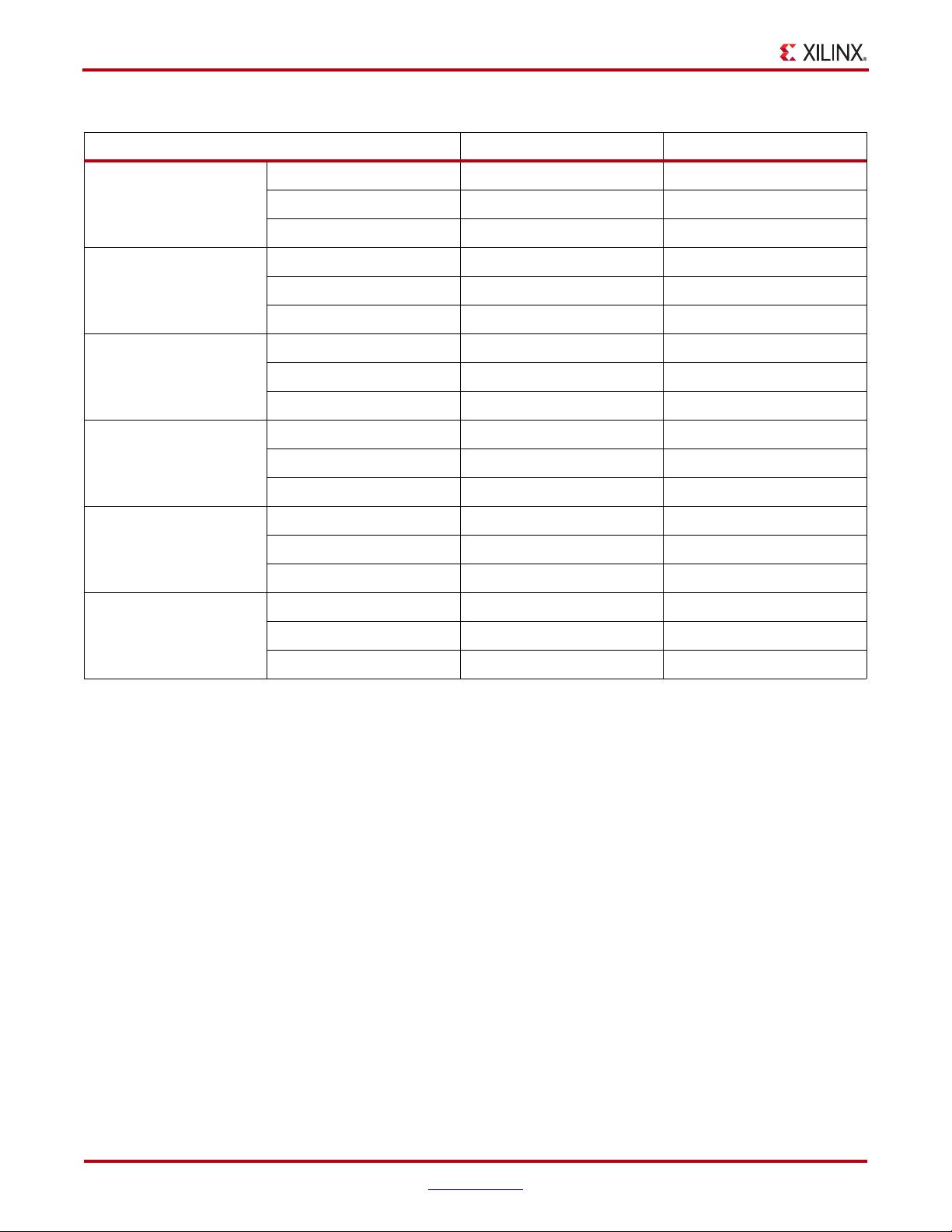

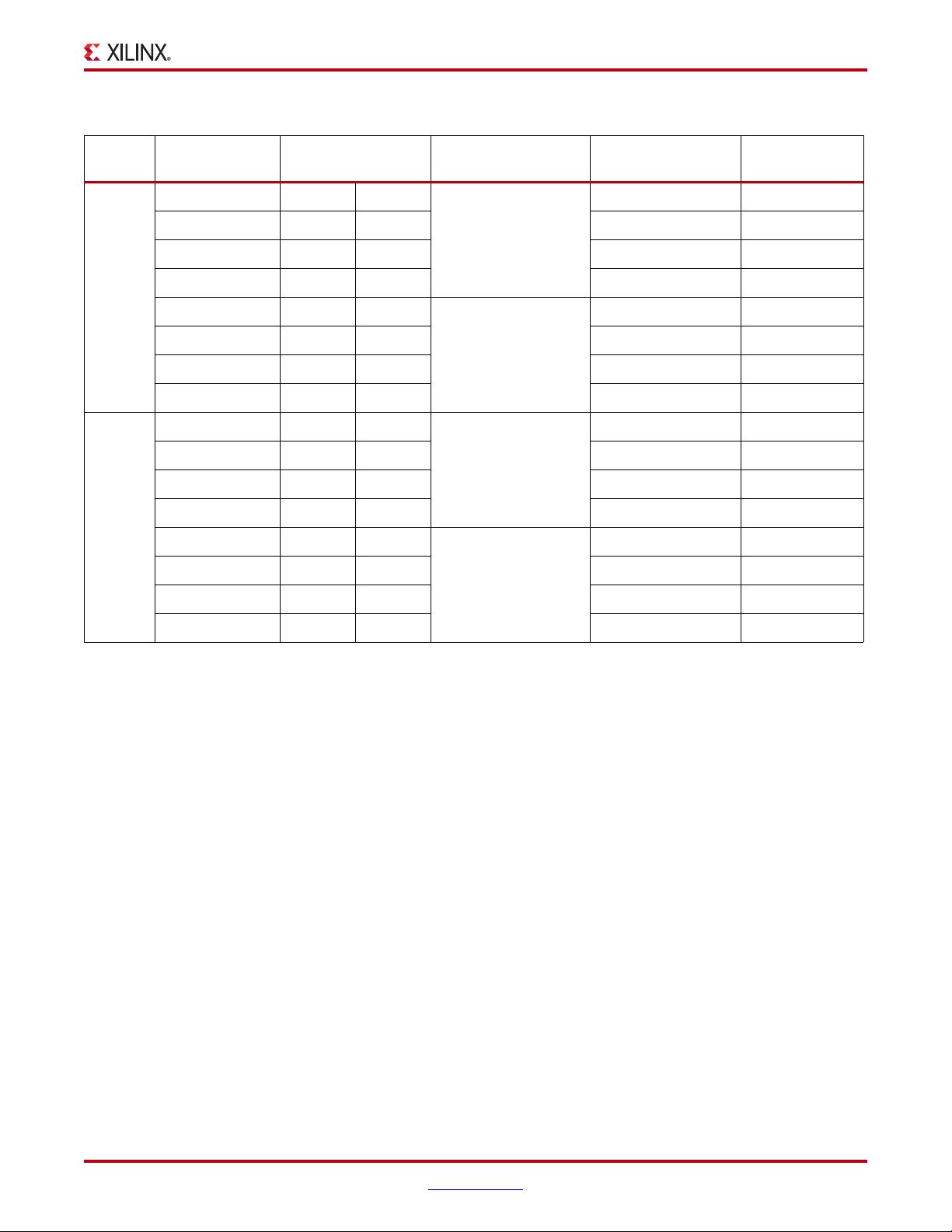

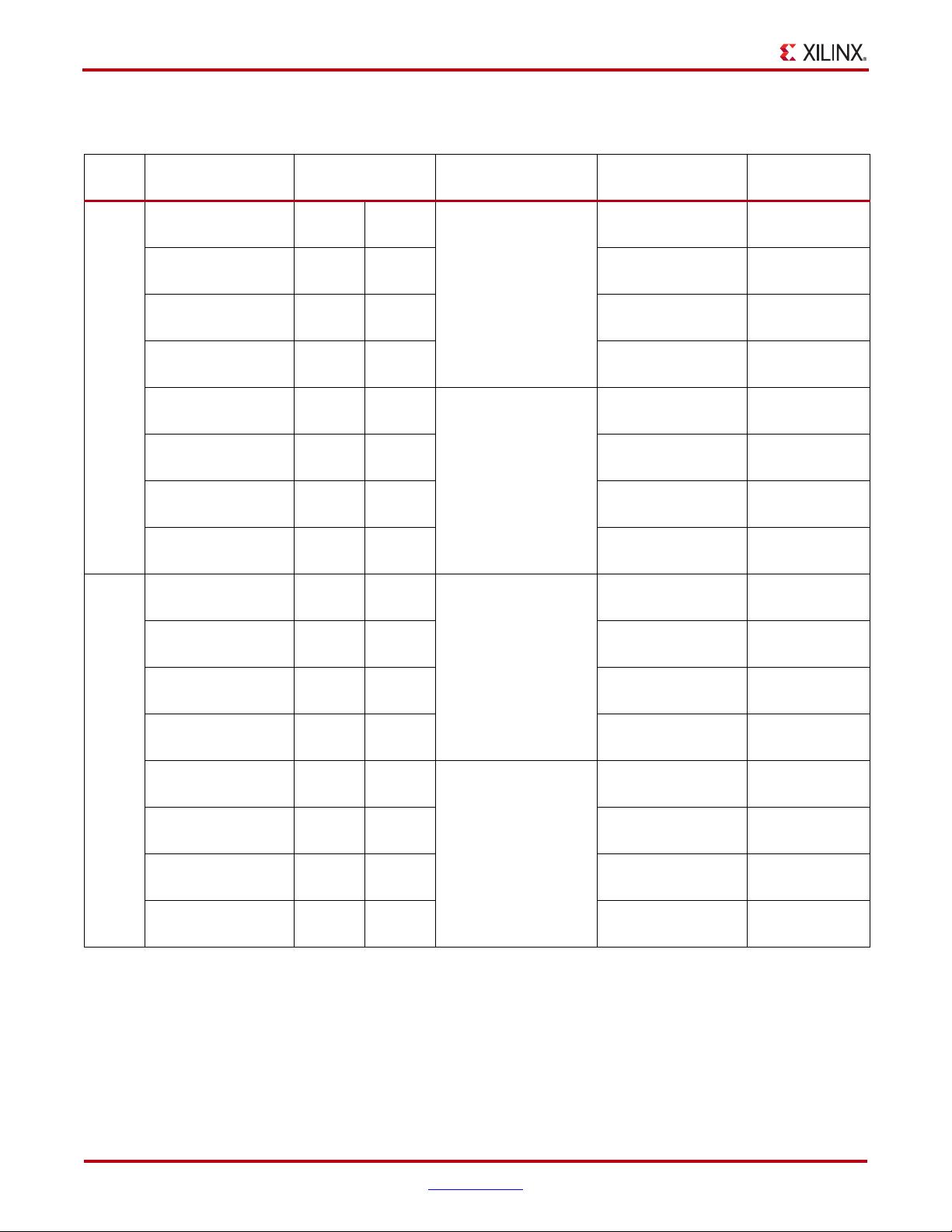

Spartan-6 FPGA的时钟资源包括了多个组件和功能,如全局时钟网络(Global Clock Network)、局部时钟网络(Local Clock Network)、锁相环(Phase-Locked Loop, PLL)、分频器(Dividers)、时钟缓冲器(Clock Buffers)以及时钟管理模块(Clock Management Tiles, CMT)。这些组件共同协作,确保了FPGA内部逻辑的同步运行。

1. 全局时钟网络:提供高效的时钟信号分布,确保整个芯片的时钟信号一致性。它通常由全局时钟输入、全局时钟缓冲器和全局时钟线组成。

2. 局部时钟网络:用于减少时钟信号的传播延迟和降低功耗,主要服务于局部区域内的逻辑单元。

3. 锁相环(PLL):PLL是时钟管理的核心,能够实现频率合成、分频、倍频、相位调整等功能,为FPGA提供灵活的时钟源。

4. 分频器:可以将高频率的时钟信号分频为更低频率的信号,满足不同逻辑单元对时钟速度的需求。

5. 时钟缓冲器:负责将时钟信号从全局或局部网络传送到需要的逻辑块,确保信号质量和驱动能力。

6. 时钟管理模块(CMT):集成在Spartan-6 FPGA中,包含了PLL和分频器等时钟处理功能,提供了高级时钟控制和管理。

用户在设计过程中,需要考虑以下关键因素:

- 时钟树综合(Clock Tree Synthesis, CTS):优化时钟路径,减少时钟 skew,确保所有触发器在同一时刻翻转。

- 功耗管理:通过合理分配时钟资源,降低无效时钟的使用,从而减少功耗。

- 时钟域跨越(Clock Domain Crossing, CDC):处理不同时钟域之间的数据传输,避免数据丢失或错误。

- 时钟抖动(Jitter):理解和控制时钟质量,减小抖动对系统性能的影响。

Xilinx提供的UG382文档详细阐述了如何有效地利用这些时钟资源,包括配置指导、最佳实践以及可能遇到的问题和解决方案。在实际设计中,设计师需要遵循文档中的建议,以确保设计的可靠性和高效性。同时,由于Xilinx有权随时更新文档,因此开发者应定期检查最新的版本,获取最新的技术信息和支持。

457 浏览量

201 浏览量

点击了解资源详情

2023-11-24 上传

706 浏览量

201 浏览量

313 浏览量

1708 浏览量

288 浏览量