FPGA设计关键概念:建立/保持时间、竞争冒险与时钟优化

版权申诉

176 浏览量

更新于2024-07-03

收藏 2.51MB PPT 举报

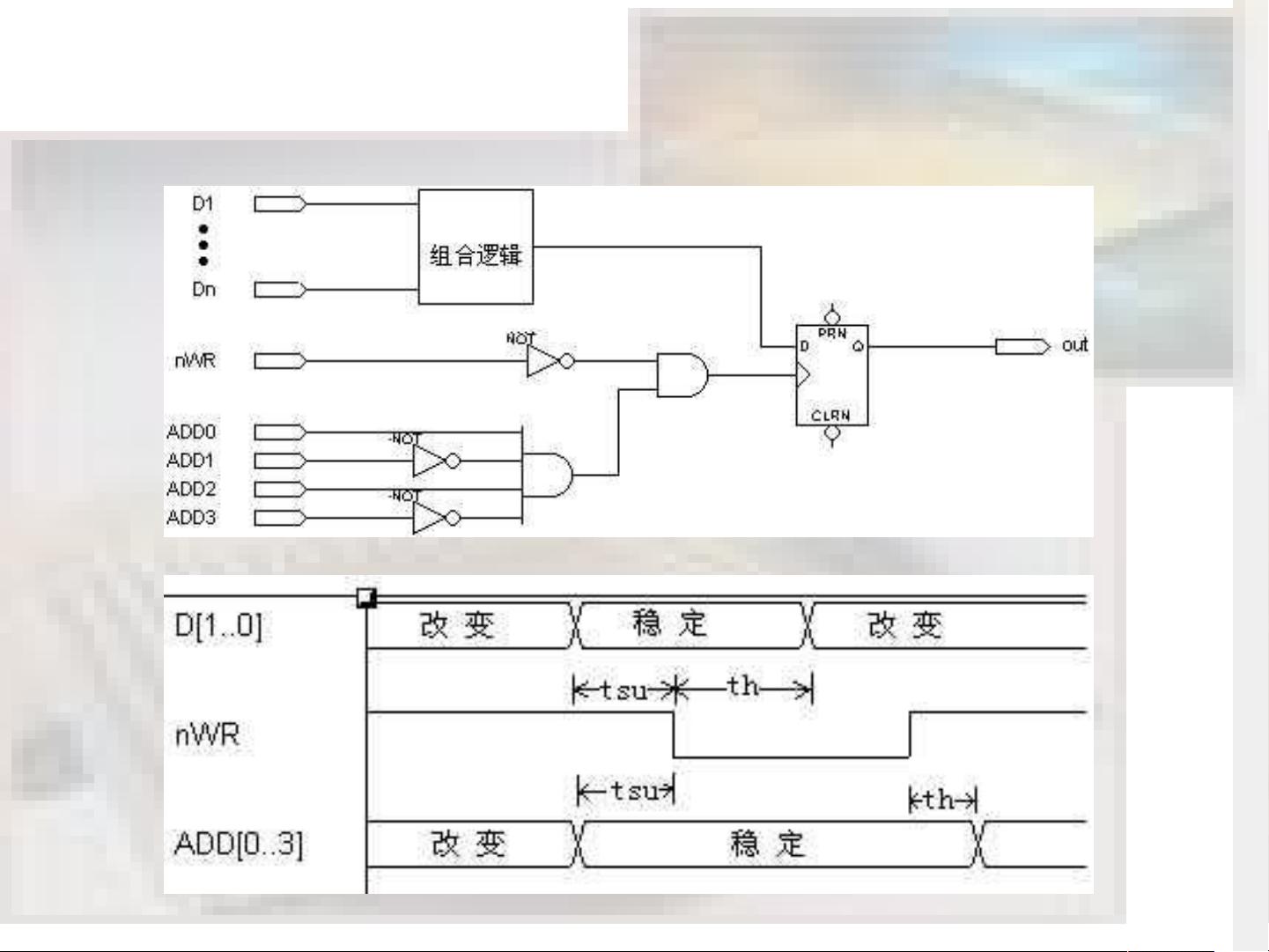

在"EDA 技术:3_3 FPGA 设计的几个概念.ppt"文档中,主要探讨了FPGA设计中的关键概念和技术。首先,介绍了建立时间和保持时间的概念,这两个参数对于确保数据准确无误地在触发器中存储至关重要。建立时间是从时钟上升沿到来之前数据稳定的时间,而保持时间是时钟上升沿后数据维持稳定的时间。若这两个时间不足,可能导致数据丢失。

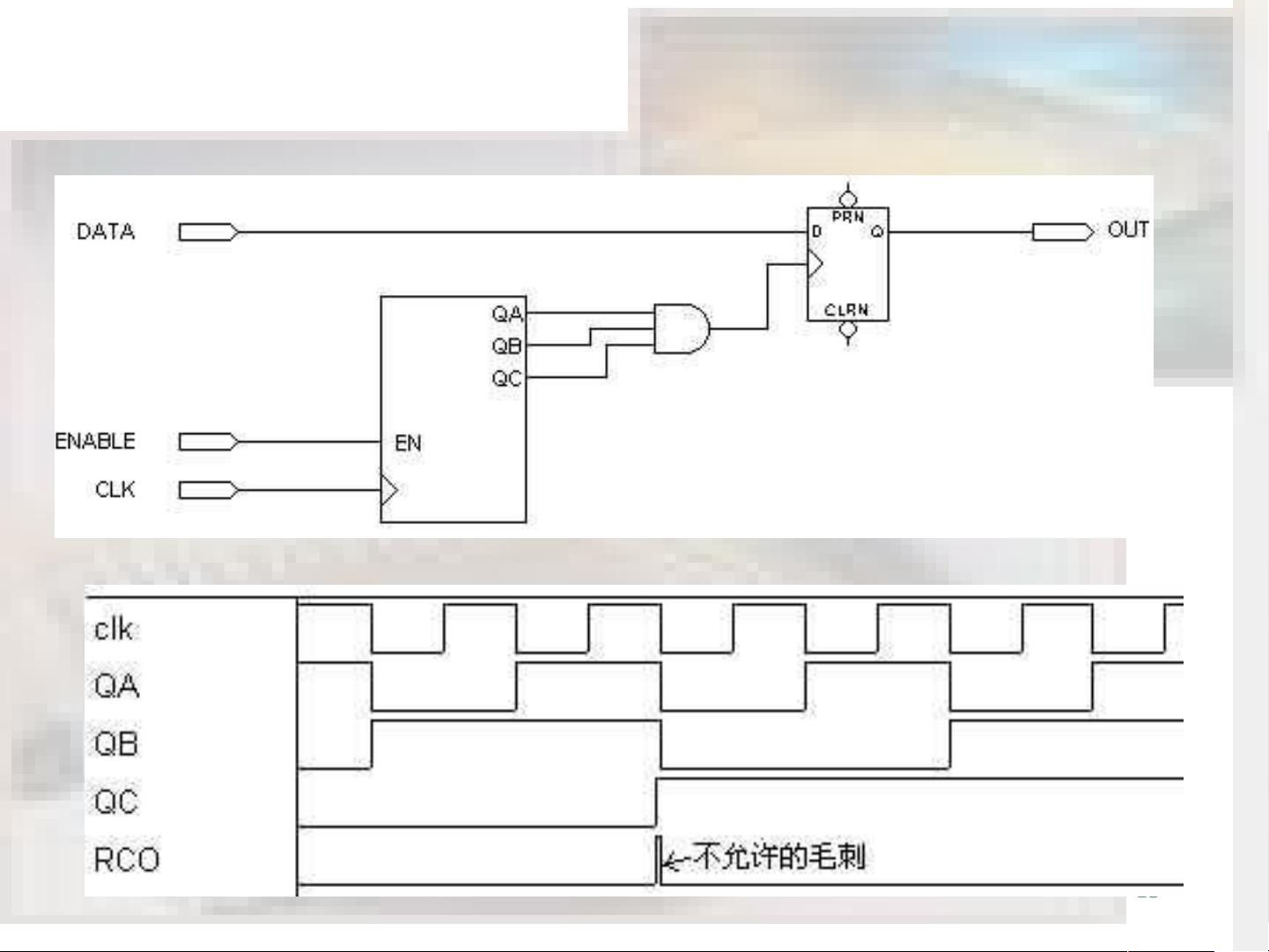

接着,文档深入讨论了竞争和冒险问题,这是数字电路设计中的常见现象。由于信号延迟和线路特性的影响,当多路信号同时变化时,可能会出现逻辑输出的不一致,形成“毛刺”。PLD/FPGA内部由于缺乏自然滤除毛刺的分布电感和电容,这个问题更为突出。为解决冒险,设计者可能采取使用格雷码计数器替代二进制计数器,以降低输出的跳变次数。

时钟信号是任何数字设计的核心,对于FPGA尤其如此。它分为全局时钟、门控时钟、多级逻辑时钟和波动式时钟等不同类型。全局时钟,作为同步时钟,提供设计项目的统一时间基准,但设计不当的时钟可能导致系统行为异常和调试困难。

总结来说,这个PPT文档详细讲解了FPGA设计中的基础要素,包括确保数据可靠性的建立时间和保持时间,处理逻辑冒险的技术,以及对时钟信号的理解和选择。这些知识点是FPGA设计者必须掌握的关键技能,有助于确保设计的正确性和效率。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-04-04 上传

2023-05-25 上传

2023-07-28 上传

智慧安全方案

- 粉丝: 3761

- 资源: 59万+

最新资源

- 计算机人脸表情动画技术发展综述

- 关系数据库的关键字搜索技术综述:模型、架构与未来趋势

- 迭代自适应逆滤波在语音情感识别中的应用

- 概念知识树在旅游领域智能分析中的应用

- 构建is-a层次与OWL本体集成:理论与算法

- 基于语义元的相似度计算方法研究:改进与有效性验证

- 网格梯度多密度聚类算法:去噪与高效聚类

- 网格服务工作流动态调度算法PGSWA研究

- 突发事件连锁反应网络模型与应急预警分析

- BA网络上的病毒营销与网站推广仿真研究

- 离散HSMM故障预测模型:有效提升系统状态预测

- 煤矿安全评价:信息融合与可拓理论的应用

- 多维度Petri网工作流模型MD_WFN:统一建模与应用研究

- 面向过程追踪的知识安全描述方法

- 基于收益的软件过程资源调度优化策略

- 多核环境下基于数据流Java的Web服务器优化实现提升性能