Quartus 11.0与ModelSim 10.0c联合仿真教程:配置与实践

需积分: 10 99 浏览量

更新于2024-07-19

收藏 1.2MB DOC 举报

Quartus 11.0与ModelSim 10.0c联合仿真的教程

一、概述

在现代集成设计环境中,高级逻辑综合器如Quartus 11.0通常不再内置仿真功能,而是倾向于与其他模拟器配合使用,以提供全面的设计验证。本文将详细介绍如何在Quartus 11.0中与ModelSim 10.0c进行联合仿真,以便有效地测试和调试VHDL或Verilog设计。

二、基本调用流程

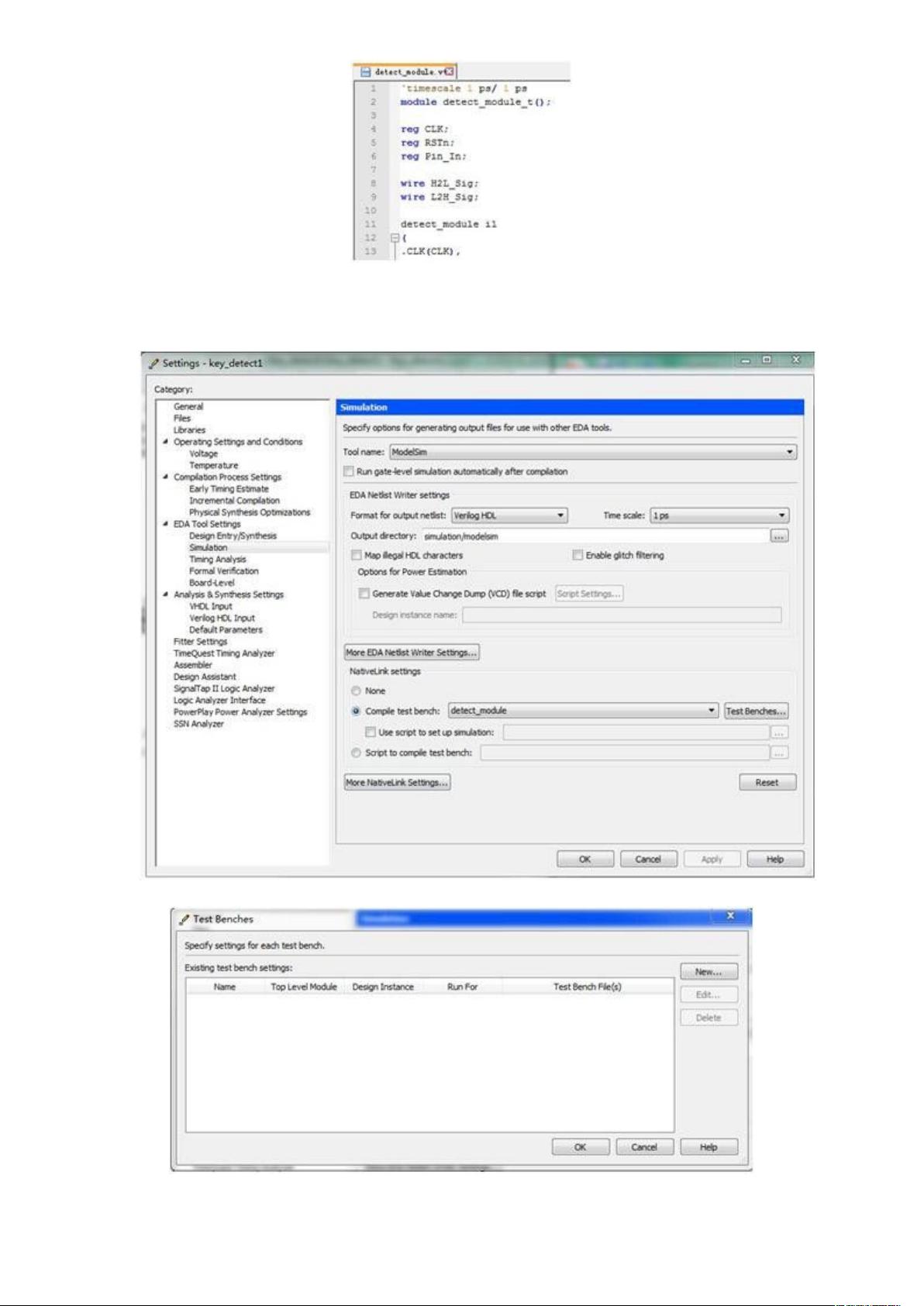

1. **设定仿真工具**

在Quartus 11.0中,你需要通过Assignment > Setting > EDATool Settings > Simulation > Toolname来配置仿真工具。选择ModelSim作为默认的仿真器,确保正确安装并配置好环境变量。

2. **自动生成测试激励文件**

在Processing菜单中选择"Start > StartTestBenchTemplateWriter",这将自动生成一个以Topmodule命名的testbench文件(如detect_modul_t.vt或detect_modul_t.vht),并将它存放在simulation/modelsim文件夹内。

3. **编辑testbench文件**

打开自动生成的testbench文件,可以添加用户自定义的激励信号、初始化语句,并且可以更改模块名称,例如这里将其命名为'detect_modul_t',以适应后续的仿真步骤。

4. **启用Native Link**

为了使Quartus能够自动调用ModelSim进行仿真,需要在Simulation设置中启用Native Link。确保"Compile testbench"选项被选中,这样工具会在编译时自动链接到testbench。

5. **指定TestBench**

首次使用时,点击TestBenches中的"New"选项创建一个新的测试bench设置。在NewTestBenchSetting对话框中,选择与生成的testbench文件相对应的Test Bench名称,如'detect_modu'。

6. **关联TestBench**

在NewTestBenchSetting对话框中输入指定的TestBench名称后,点击OK按钮,确保Quartus能够识别并调用对应的testbench文件进行仿真。

三、注意事项

- 在实际操作中,确保Quartus和ModelSim的版本兼容性,以避免潜在的问题。

- 定期更新ModelSim的驱动和库文件,以获取最新的仿真支持和优化。

- 在进行大规模设计时,可能需要编写复杂的testbenches,包括时序分析和覆盖率检查等高级功能,这些功能在本文中暂未涉及,但ModelSim提供了丰富的工具和文档供进一步学习。

通过以上步骤,你就可以在Quartus 11.0环境中利用ModelSim 10.0c进行有效的设计验证,确保硬件设计的正确性和可靠性。随着设计的复杂度增加,熟悉这两种工具的深入结合将大大提高工作效率。

2024-10-27 上传

2024-10-28 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

tianxiayitong0603

- 粉丝: 0

- 资源: 1

最新资源

- Elmag-开源

- Customer-Revenue-Prediction

- Scratch少儿编程项目音效音乐素材-【风】相关音效-诡异的风.zip

- 火箭服务器

- robot,c语言吃豆子源码,c语言项目

- aircnc-react:一个漂亮而简单的应用程序,适用于开发公司景点

- sc-fermi-开源

- 陀螺仪和加速度计的卡尔曼MATLAB仿真.rar

- naviworks

- SF-DST10-RDS4

- Tic-Tac-Toe---Player-againts-Computer---Java-Swing

- my-vocab

- Scratch少儿编程项目音效音乐素材-【打斗】音效-打群架.zip

- 暴雪:转到暴雪API数据的客户端库

- ADIS16255Driver,c语言库源码大全,c语言项目

- DSAPCS1092:这是CYCU的DS课程